- 1git与github区别与简介_git和github的区别

- 2cmd命令行怎样运行python,在CMD命令行中运行python脚本的方法

- 3基于Python电商用户行为的数据分析、机器学习、可视化研究_利用机器学习算法分析用户行为数据

- 4【leetcode】n皇后问题--回溯法_n皇后问题回溯法

- 5基于SpringBoot+Vue+uniapp的明水县苹果网吧计费管理系统的详细设计和实现(源码+lw+部署文档+讲解等)_网吧计费系统 开源

- 6git访问失败,无法从git服务器下载代码或上传代码的解决办法_git 访问失败

- 7数据结构之二叉树(Binary-Tree)_数据结构中的树有哪些?介绍二叉树。

- 8JAVA华为面试题_在编译程序时所能指定的环境变量不包括

- 9手把手教你Anaconda安装虚拟环境配置yolov5_anaconda安装yolov5

- 102024金三银四Android面试心得,已拿到多个offer(1),大厂面试流程慢

2024年Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis,2024年最新设计思想与代码质量优化+程序性能优化+开发效率优化_vivado2024手册

赞

踩

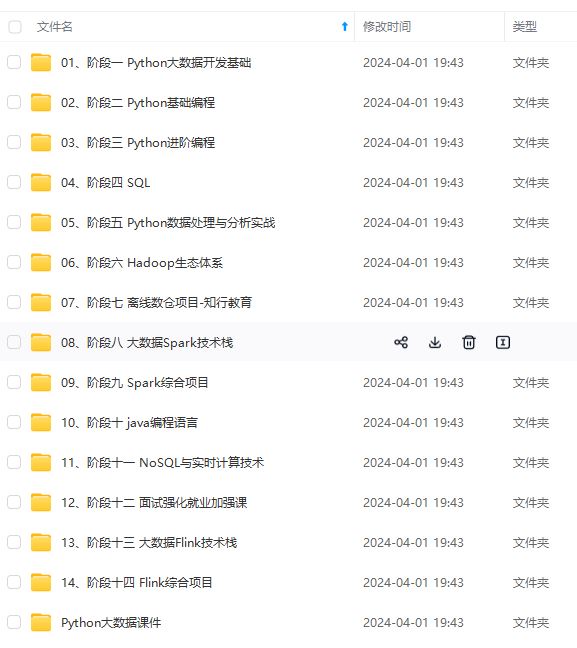

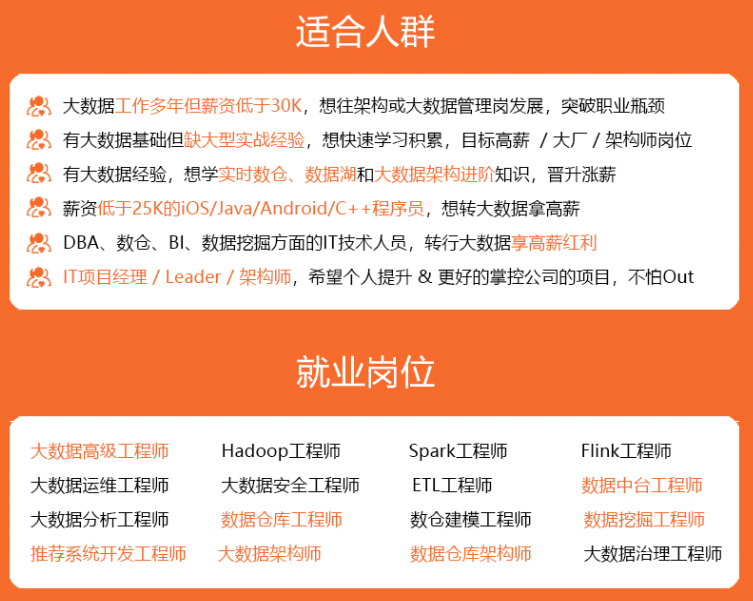

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

假设要实现简单的加法器----2个8bit输入的加法,不考虑进位,即输出同样为8bit。根据需求可以很容易地写出代码:

module test(

input [7:0] in1,

input [7:0] in2,

output [7:0] out

);

assign out = in1 + in2; //简单加法器

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

这个代码的核心只有一句,就是用一个assign语句将两个输入相加。这一语句转化成逻辑电路,很明显就是一个加法器。

光说不练云玩家,接下来添加测试工程,并把该文件保存后,按下图顺序点击:

可以看到RTL分析后的电路:

和预期的一致吧?就是一个2输入8bit的加法器。

3、综合(synthesis)

综合是指将高级抽象层次的语言描述转化成较低层次的***电路结构,***也就是说将硬件描述语言描述的电路逻辑转化成查找表LUT、触发器等FPGA内部存在的基本逻辑单元的互连关系,也就是我们常说的综合网表。

比如上面的例子,RTL分析后的电路是一个2输入8bit的加法器,那么综合后的电路是什么样子呢?按下图顺序点击:

可以看到综合后的电路是这样的:

好家伙,出来一大堆乱七八糟的,这跟RTL电路完全不一样呀?这些玩意都是啥?

- 2个输入端口的8+8 共16个IBUF,是FPGA的IO口默认添加的输入缓冲,这个更多是为了电气方面的考量,和逻辑关系不大

- 8个LUT2 + 2个CARRY4,这都是FPGA底层的逻辑资源,用来实现各种组合逻辑功能

- 1个输出端口的8个OBUF,是FPGA的IO口默认添加的输出缓冲,

那么,为什么RTL电路和综合后的电路有如此大的区别?因为RTL电路是把HDL转化成逻辑电路,而综合后的电路则是用FPGA内部的逻辑资源来实现。所以最直接的原因就是FPGA底层没有加法器这个东西,只能用其他逻辑资源来实现加法器的功能。

4、实现(implementation)

综合后生成的综合网表只是表示了逻辑资源之间虚拟的连接关系,并没有规定每个逻辑资源位置以及连线长度等。实现就是一个将综合网表中的逻辑资源位置以及连线长度确定的过程。

比如上例中,综合后的电路由8个lut2 + 2个CARRY4 + 24个IOB组成,但是FPGA内部的LUT、CARRY4和IOB的数量远不止这些,所以需要根据用户设定的策略(面积优化、速度优化)来找到具体的逻辑资源。

那么实现后的电路是什么样子呢?按下图顺序点击:

此时,看到的是整个FPGA芯片的资源使用详情:

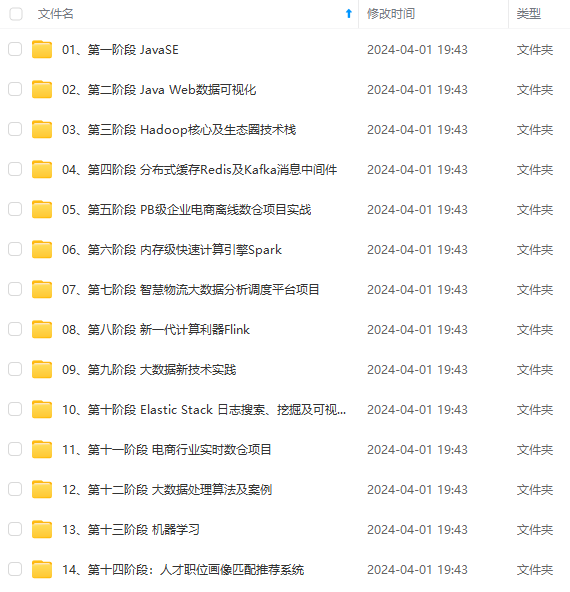

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新**