- 1Flink服务的HA配置_flink ha

- 2AI今日头条如何做到三天起号,简单无需经验 3分钟创作1条

- 3git访问失败,无法从git服务器下载代码或上传代码的解决办法_git 访问失败

- 4杨植麟闫俊杰都来站台!钉钉要建中国最开放AI生态

- 5hadoop单机版安装_hadoop单机配置

- 6九型人格:四、The TRAGIC ROMANTIC 悲情浪漫者 - 我若不是独特的,就没有人会爱我_我若没有就没有人会爱我九型人格

- 7一篇文章带你走进 UDP报文段的 『首部格式』_udp报文首部

- 8【C++】Mutex::AutoLock介绍_c++ autolock

- 9网络编程基础知识拾遗:用大白话解释什么是交换机、路由器、光猫、IP地址和子网掩码、公网和内网IP、端口和域名

- 10基于Hugging Face -Transformers的预训练模型微调_hugging face transformers

FPGA之JESD204B接口——总体概要 实例 下_hmc7044驱动

赞

踩

1、概述

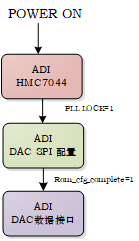

DAC正常工作的前提是电源以及时钟稳定工作,因此需要首先配置锁相环,根据ADI评估板EVAL-AD9174开发记录—上的时钟需求配置出需要的时钟频率,待时钟锁定后配置dac内部锁相环,NCO,jesd模式等寄存器,待dac配置完成后实现与FPGA之间数据link。

2、HMC7044配置

2.1、接口驱动

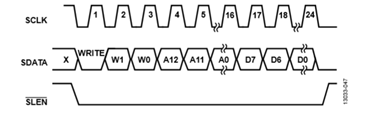

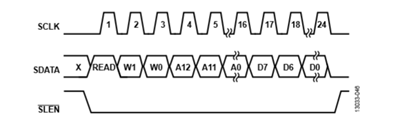

时钟接口代码由ROM配置模块、操作维护配置模块和SPI接口组成。其中ROM配置模块用于存储时钟和时钟的上电配置数据;操作维护配置接口则用于接收从操作维护接口送入的配置数据,并转换为SPI接口所需的数据;SPI接口负责将并行配置数据按照PLL芯片所定义的SPI时序,转换为串行数据送给PLL芯片进行寄存器配置。

写时序:首先片选信号拉低,接着24位数据依次在24个时钟上升沿送入HMC7044中;

读时序:如图1-14所示,片选信号拉低,接着16位数据在时钟上升沿送入时钟芯片中,对应8 bit寄存器数据会随着下个时钟上升沿串行传输返回至FPGA。

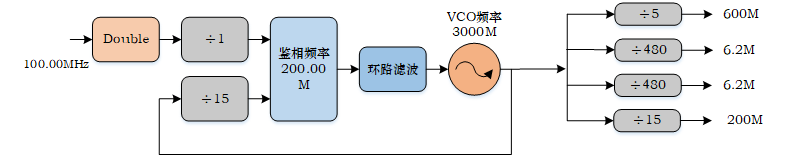

2.2、配置参数

根据pll数据手册以及adi锁相环工具可以比较方便导出所需要时钟的配置参数,本设计只使用了单锁相环模式,主要配置参数有锁相环R/N分频,环路滤波参数、通道分频参数等。

参考手册及pll工具:

① HMC7044

② ADIsimCLK

③ HMC7044 GUI

通过HMC7044 GUI界面配置可以导出完整的配置参数,导入到rom中进行上电默认配置。

3、DAC配置

3、DAC配置

3.1、接口驱动

同PLL配置,不再赘述。

3.2、配置参数

DAC配置寄存器步骤如下所示:

1、 对DAC供电并设置寄存器为写模式;

2、 配置DAC内部锁相环PLL;

3、 配置DAC内部DLL;

4、 校准控制寄存器;

5、 配置JESD204B模式;

6、 配置通道路径:数字增益和通道NCO;

7、 配置主要DAC路径:PA保护和主要NCO;

8、 配置JESD204B串行链路;

9、 配置传输层:同步和使能链路;

利用adi 评估软件可以导出完整配置参数

① ACE

4、JESD数据通道

4、JESD数据通道

JESD204B接口主要由JESD204B PHY IPcore、JESD204B IPcore、数据整理模块组成,如图各模块功能如下:

1、 JESD204B PHY IPcore:该模块为Xilinx提供的IPcore,主要负责将FPGA中串行数据转换为并行数据,并通过GTX送入DAC中进行数模转换。

2、 JESD204B IPcore:该模块为Xilinx提供的IPcore,主要负责根据JESD204B协议建立与DAC的连接,将FPGA中处理的数据基于JESD204B协议发送到DAC。

3、 信号产生模块:通过算法产生所需DAC发送的数据。

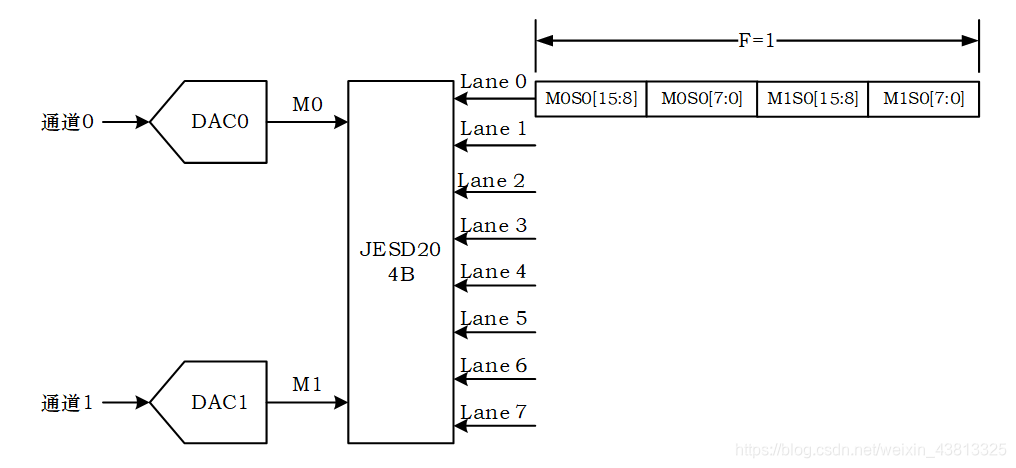

根据AD9174手册的描述,在上节所选的JESD204B工作参数的状态下,其输出数据帧格式如图所示。

根据数据帧格式,组帧模块如下:

DDS发送单音信号测试频谱如图。。