热门标签

热门文章

- 1推荐7个学习Vue3开源项目_vue开源项目实例源码

- 2AI Mass人工智能大模型即服务时代:智能投资的智慧财富

- 322.MongoDB删除操作效率及相关问题验证_mongo删除性能

- 4第六篇:Python编程精粹:深入常用库与高效开发实践

- 5【机器学习】机器学习与大模型在人工智能领域的融合应用与性能优化新探索_机器学习+大模型

- 6高考志愿填报,选专业应该考虑哪些因素?

- 7java输入与输出_java输入和输出

- 8numpy()的类型-astype、dtype_numpy float astype str

- 9收藏!2024 年最具潜力 44 个顶级开源项目,涵盖 11 类 AI 学习框架、平台_序列大数据的智能计算 开源项目(1)_大厂开源项目

- 10mongoDB windows 安装,启动服务 + docker 安装_windows安装mongodb并启动进入

当前位置: article > 正文

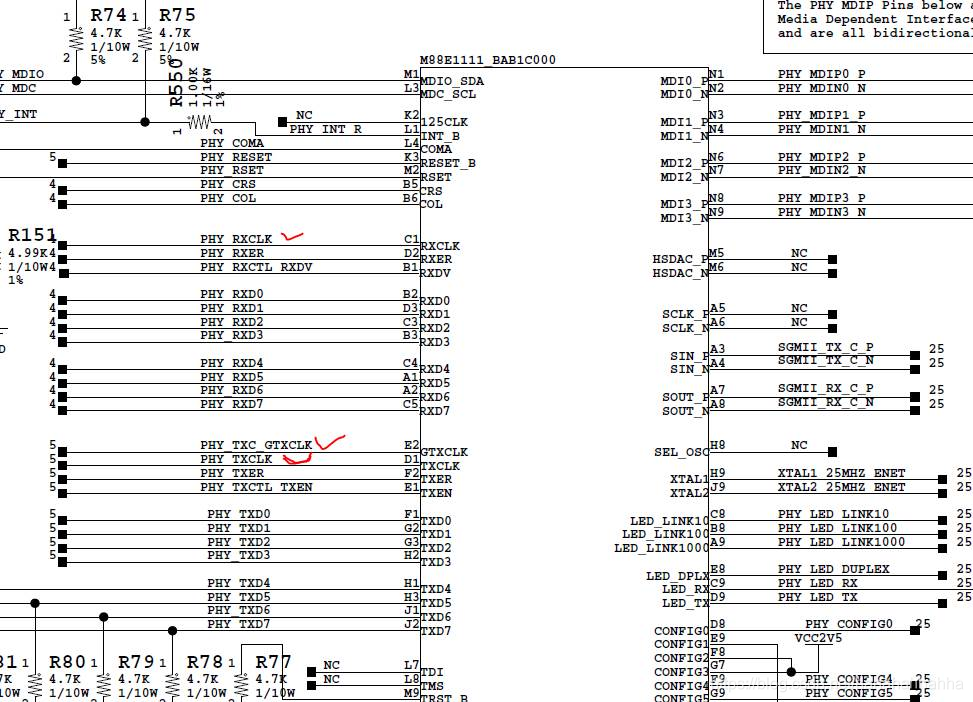

【硬件】以太网PHY芯片有三个时钟说明_电路txclk

作者:酷酷是懒虫 | 2024-07-05 04:57:09

赞

踩

电路txclk

硬件以太网PHY芯片有三个时钟,对此进行了梳理:

PHY芯片时钟的选择:

PHY芯片中有3个时钟, Gtx_clk,Rx_clk ,Tx_clk。

1) GTX_CLK仅使用在GMII模式下,时钟频率为125M,发送数据时的时钟。

2) RX_CLK在GMII和MII模式下均可使用,网络接收数据的时钟。

3) TX_CLK仅使用在MII模式下,发送数据时的时钟。

与MII接口相比,GMII的数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

附件为KC705原理图,第25页是M88E1111的连接图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/酷酷是懒虫/article/detail/789263

推荐阅读

相关标签