- 1【IEEE出版】第六届电子与通信,网络与计算机技术国际学术会议(ECNCT 2024,7月19-21)_2024 ecnct

- 2如何在 JavaScript 中对字符串进行索引、拆分和操作_js字符素引

- 3前端7大常用布局方式_前端布局

- 4Postman学习笔记一界面详解,发送请求,查看响应_postman 查看请求报文

- 5C++进阶学习——单向链表的实现_set next c++

- 6使用YOLOv8+SAHI增强小目标检测效果并计算评估指标_yolov8 sahi使用

- 7开启物联网的真正潜力需要在更大程度上克服数据挑战

- 8创建型设计模式----工厂方法模式_创建型-工厂方法模式

- 9Spring Boot 实现 WebSocket 示例_websocket端口号在哪设置,spring

- 10前端常用的设计模式总结——工厂模式_前端工厂模式

FPGA基础知识 VHDL简述_fpga vhdl

赞

踩

目录

EDA技术概论

1.FPGA与CPLD有什么区别,各应用在什么场合?

(1)

| CPLD | FPGA | |

| 内部结构 | Product-term | Look-up Table |

| 程序存储 | 内部EEPROM | SRAM,外挂EEPROM |

| 资源类型 | 组合电路资源丰富 | |

| 集成度 | 低 | 高 |

| 使用场合 | 完成控制逻辑 | 能完成比较复杂的算法 |

| 速度 | 慢 | 快 |

| 其他资源 | - | EAB,锁相环 |

| 保密性 | 可加密 | 一般不能保密 |

(2) FPGA采用SRAM 进行功能配置,系统掉电后数据丢失不易保存,因此需要另加EPROM 来保存数据。

CPLD 一般采用EEPROM存储技术,系统掉电后数库不丢失。

(3)FPGA器件含有丰富的触发器资源,易于实现时序逻辑。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少、

(4)FPGA是细粒结构,CPLD是粗粒结构。

CPLD的利用率较FPGA低。

(5)FPGA为非连续性布线,CPLD为连续性布线。

2.硬件描述语言国际标准有两种,分别是? vhdl verilog hdl

3.基于EDA软件的FPGA / CPLD设计流程

4.EDA技术的含义和内容是什么?

EDA(Electronic Design Automation)是电子设计自动化的意思,指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

VHDL是电子系统设计者和 EDA工具之间的交流界面。

5.VHDL硬件描述语言的特点?

(1)具有强大的语言结构,系统硬件描述能力强、设计效率高;具有较高的抽象描述能力

(2)VHDL语言可读性强,易于修改和发现错误。

(3)VHDL具有丰富的仿真语句和库函数。

(4)VHDL源代码进行早期功能仿真,有利于大系统的设计与验证。

(5)VHDL设计与硬件电路关系不大

VHDL简述知识点

1.、VHDL中最基本的结构是什么?其作用各是什么?

库、程序包使用说明;

库(library)和包的建立和使用有利于设计的重用和代码共享,同时可以使代码结构更加清晰。

实体说明;

与实体对应的结构体说明

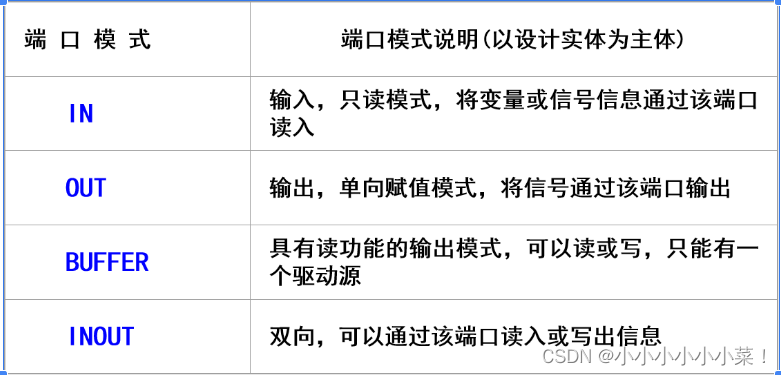

2、说明inout、out 和 buffer有何异同点

3.类属(GENERIC)参量是一种端口界面常数

GENERIC([常数名1:数据类型:=设定值1];

[常数名n:数据类型n:=设定值n]);

4.

常数:constant

信号:signal

数据类型:type

元件:component

函数:function

过程 :procedure

block结构内部语句: 并行描述语句

process结构内部语句是: 顺序描述语句

configuration 配置语句格式和结构体architecture相同 : for + 被选结构体.

1.after 语句和wait for 语句的区别

(1). after表示从仿真周期的起点开始,到当前信号值发生变化时的整个时间区间,当该信号需要再次变化时,时间量只能升序。 例:

x<=1 after 10ns; x<=2 after 20ns; x<=3 after 30ns;

(2). wait for语句表示一个信号值的保持时间长度,时间量的大小不必升序。例:

x<=1;wait for 10ns; x<=2; wait for 5ns; x<=5; wait for 2ns;

静态数据对象:

1.constant -> constant set_bit : BIT :='1'; (一旦赋值不能改变)

常量的作用范围取决于它定义的位置:

包集中:全局;

实体中:对该实体内的所有结构体而言是全局的;

结构体中:结构体内是全局的。

2.generic -> generic (width:integer := 16);

常以一种说明的形式放在实体或块结构体前的说明部分,说明内部电路结构和规模 。

非静态数据:

1.variable -> variable a,b : STD_LOGIC

例: variable counter: integer range 0 to 255 := 100;

变量是一个局部量,只能在进程和子程序中使用;

变量的赋值是一种数据存取是立即发生的,不存在时延。

2.signal -> signal dbus : std_logic_vector(15 downto 0)

signal sys_clk : bit := '0';

- 信号赋值延迟更新数值、时序电路;

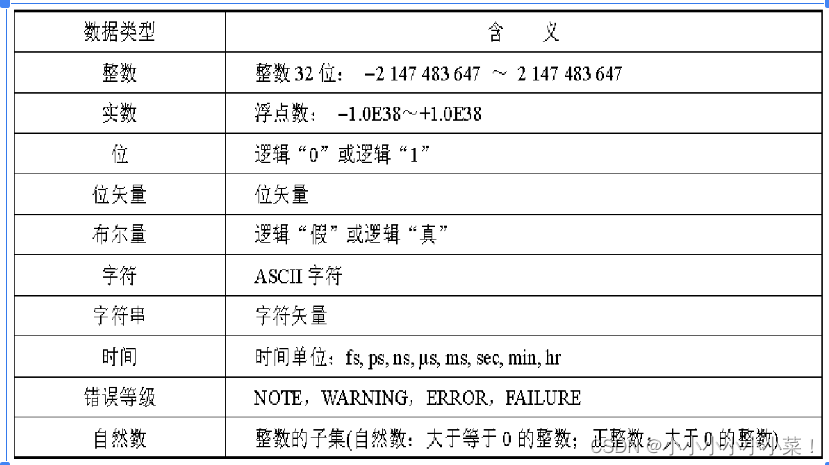

预定义类型在VHDL标准程序包STANDARD中定义,在应用中自动包含进VHDL的源文件,不需要USE语句显示调用

注意:

- 实数一定要带有小数点。

- 整数的子类 : 1.natural -> 大于等于0的整数

2.positive -> 正整数

- 在系统仿真时,时间数据特别有用,用它可以表示信号延时,从而使模型系统能更逼近实际系统的运行环境。

- 如果用户需使用这10种以外的数据类型,则必须进行自定义。但大多数的CAD厂商已在包集合中对标准数据类型进行了扩展。 例如,数组型数据等。

用户自定义的数据类型

1.枚举类型: type my_logic is ('Q','z','0');

2.数组类型:

· type row is array(7 downto0 ) of std_logoc 一维数组

· type matrix is array(0 TO 2 ) of row 1*1维数组

· type matrix is array(0 TO 3,7 downto0 ) of std_logic 二维数组

3.记录类型 (recorde)

记录类型和数组类型有些相似,RECORD类型内部可以包含不同类型的数据,而ARRAY只能包含相同类型的数据

type birthday IS recorde

day: integer range 1 TO 31

month:month_name;

end recorder;

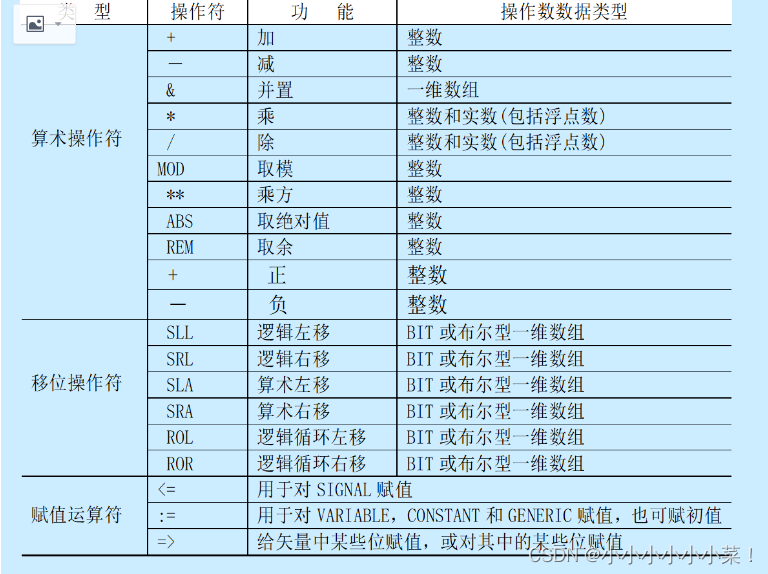

4.赋值运算符:

- <= 用于对signal赋值

- := 用于对variable,constant 和 generic 赋值,也可用于初始赋值

- =〉 给矢量中某些位赋值,或对某些位之外的其它位赋值