- 1redis的基础底层篇 zset的详解_redis zset

- 2离线数仓数据导出-hive数据同步到mysql

- 3VR全景在线虚拟展厅实现全方位沉浸式互动体验_vr在线体验瑟瑟

- 4怎么自学python自动化测试-Python移动自动化测试面试 学习 教程

- 5vscode的launch.json是什么_vscode launch.json

- 6Git error: cannot lock ref_error: cannot lock ref 'refs/heads/main': is at

- 7MySql重点复习——删除表的方式_mysql删除表

- 8YOLOv9改进策略 | 损失函数篇 | 利用真实边界框损失之MPDIoU助力YOLOv9精度更上一层楼_pred_bboxes_pos = torch.masked_select

- 9华为OD机试统一考试D卷C卷 - 查找接口成功率最优时间段(C++ Java JavaScript Python C语言)

- 10【Git】本地仓库关联远程仓库_git本地仓库关联远程

[原创]Cadence软件使用记录8_Allegro绘制PCB菜鸟初成_pcb allegro candence

赞

踩

先对前述文章做个补充:

有的接插件是有机械孔的,这个mechanical hole有讲究,字不重要看图:

需要指明每一层的连接几何尺寸,17.2最高支持32层VIA,所以要问,我就画四层板,中间不应该是两层么,你整这么多层?没问题!用不上的层,自动忽略了。

菜鸟初成

零零散散的要点:

-

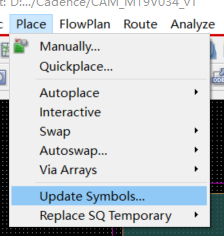

当发现元件封装画错了怎么办?

打开元件封装,重画。然后

选择你想要的更新的元件封装,单击左下角的refresh按钮就行了(前提是你待更新的元件在当前PCB中未被fix,如果被fix了,那就unfix解除之后再更新) -

在内电层分割的时候,如何高效操作?

先把地相关的NET高亮起来,比如PCB包含AGND和DGND两种地,分别着不同的色就好了。先单击刷子,再选个颜色

选你想要高亮的NET,单击就好。由于我这里已经分割了内电层,所以整块区域都亮了。

不想这么闪耀,回到过去?

取消高亮就行了,选ALL

另外,不要怪allegro颜色暗淡,是因为你没有调光,如下图:

-

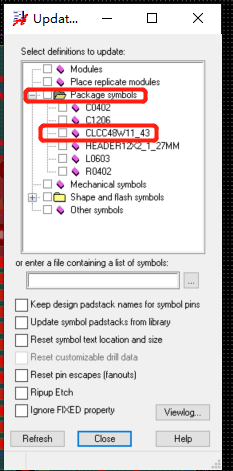

一般需要用fill处理的部分,画块几何图形就好了

只不过需要你指定一下,net name,软件自己不去体会的。 -

画了多个几何图形,也叫shape,如何合并?

然后依次点击需要的合并的shape就好了。 -

我只是想放些过孔,比如电源附近,怎么搞

通过布线按钮,在需要的NET上双击,便得到VIA。然后借助copy命令,把这个VIA按照一定的几何关系摆放下去。效率相当高!

明明FILL重叠了为什么也不避让?

那是因为你没有设置smooth:

先说这个情形只发生在动态铜且未开启smooth,但是为什么不报错?

这需要解释一下dynamic fill选项:

smooth:铜皮会自动实施避让

rough:用于显示铜皮的连接,注意在输出光绘文件时,需要选择smooth

disabled:铜皮不会实时避让,需要单击update to smooth才会避让

有的教材建议先动态,然而逐个把动态铜转换成静态铜

我的建议:

直接开smooth,动态铜绘图,一了百了

其他配置参数一览:

Shape fill:

Xhatch style:铜皮填充方式,不展开了

Hatch Set:填充铜皮的平行线的设置,根据Xhatch style的不同设置不同,也不展开

Void controls:

artwork format:设置光绘文件采用的文件格式

minimum aperture for gap width:指定两个避让之间或避让与铜皮边界之间的最小距离

suppress shapes less than:在进行动态覆铜时,由于cline和pin等的阻隔,可能整个铜皮将被分离成多个部分,如果某个部分的面积小于本处指定的大小,则将被忽略,不予覆铜

Clearances

DRC:按照DRC检测中设置的间隔产生避让(也就是之前提到的CM)

thermal/anti:根据在pin或者via焊盘中设置的thermal/anti产生避让

说说DRC

这是大哥,慢慢说。

每次画完板子,必须要做DRC检查,尤其是未完成的布线。

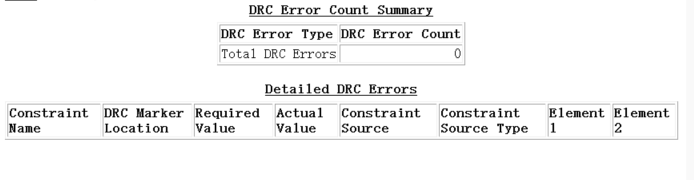

首先保证,全部是0.不是?通过reports找,比如:

这里会清楚的告诉你,哪个元件的引脚没连。

DRC还要看哪些?其实在之前的博客中已经提到CM,即constrain manager。这里就是部分的DRC约束,所以,要设置查看DRC,也来CM里。

你让软件运行DRC,你得告诉软件,分析哪些内容,所以单击analyze然后依次设置。

Design Modes(Package)

Electrical Options、

Electrical Modes、

Physical Modes、

Spacing Modes、

Same net Spacing Modes、

SMD Pin Modes、

Custom Measurement Modese

这些都要在ON这个栏位全部都选中

勾选On-line DRC,

OK开始更新DRC。

UPDATE DRC的方法:在菜单栏中执行:Tools–Dtabase check如下图

log信息报告无DRC错误

No DRC errors detected.

- 1

我认为制造一个

更新一下DRC看看

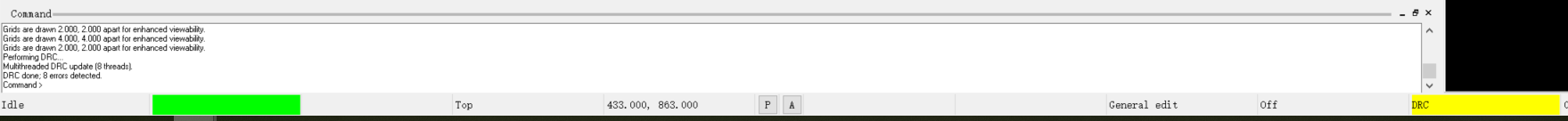

Performing DRC...

Multithreaded DRC update (8 threads).

DRC done; 8 errors detected.

Command >

- 1

- 2

- 3

- 4

怎么查看错误呢?

-

看DRC的字母代号,对号入座,待会给个表

比如这里的PL,是说Pin跟Line太近了 -

生成report挨个对,其实还不如quick report,一个个看也挺好。(从UI看reports直接粗暴循环调用了quick report)

建议的几个report:Daling lines、via and antenna Report、Unconnected Pins Report、Unplaced Components Report、Design Rules Check(DRC) Report等等

常见DRC对照表:

好了,到这里重要的部分已经讲完,现在按部就班走流程吧:

丝印处理

最多的问题,丝印层和装配层干嘛的?

先从封装制作谈起:我们画封装会指定物理图形层、丝印层和装配层,都在package geometry中,分别是place bound、silkscreen 和assembly。

物理外形图形PLACE BOUND TOP /BOTTOM

常用来指示元件内部的布局区域,画封装时用到。这个装配层为这个元件圈了一块地,这就是bound。如果两个元件靠的太近,就会DRC,靠的就是计算装配层的bound是否交叠。

丝印层SilkScreen layer:

零件的外形平面图,丝印层是指代表器件外廓的图形符号。就是拿到板子后,直观看到的字符标识。

装配层Assembly layer:

但是你也不能空荡荡的只画块地吧?所以,标识一下这是谁的地,这就是ref des,隶属于

装配层。

然而你画电路总要加点版本信息什么的,但这好像不属于上面两个情况啊。好的,我们自己搞一个C++类,board geometry,专门画自定义的文本。

现在要生产加工了,喷板字符到底写什么?,在artwork control form设置的时候,添加一下就好了。

软件后台操作(我假想的):再定义一个类,你想导出哪一层,就继承哪一层,你来确定!所以,

- 你指定ref des导出没问题,

- 你指定ref des不导出,而将silkscreen导出也没问题。

所以,发现一个问题,既然装配层都标识好了,我还费什么劲,直接最后导出的时候选择ref des不就完了么?是的!但是,我还是建议规范些:三个都得画,bound作为边界这自不必说,assembly作为装配层参考也画,但后期的字符就不调整了。而silkscreen必须要调整一下大小和位置,用作生产喷丝印。

另外,现在17.2引入新的功能autosilk,这个隶属于manufacturing类。但是,功能真的不咋地,虽说按既定规则自动抽取某些silk到autosilk,但是,它无法保持之前autosilk的既定丝印位置不变。导致我改版后重新autosilk还得重调丝印。倒不如还按之前的办法,手动调整,既美观还可以热更新。

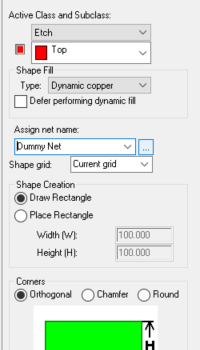

字体调整

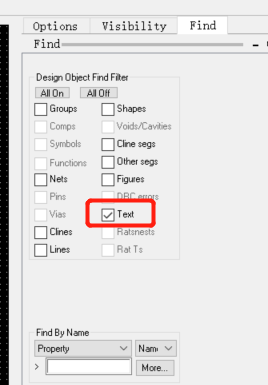

直接来说就是,change选中text,右键done完成:

必然需要勾选Text的,因为你改的就是它

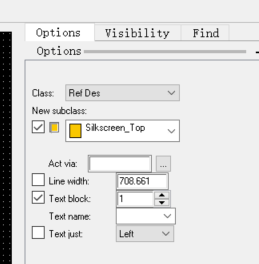

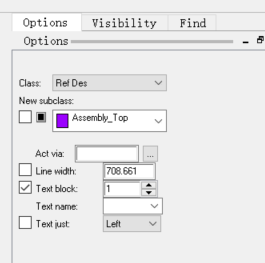

options中选中ref des -> silkscreen,因为我们想改丝印大小。但是,如下做法是错误的,是最为常见的错误!

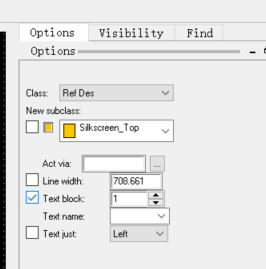

正确的如下:

为什么?就是不要勾选silkscreen的复选框。因为你现在是change,会把ref des的assembly子类改变到silkscreen子类中。到那时你就有两个silkscreen了!如果已经失误了怎么办?我的方法是update symbol,之前博客讲过update方法,此不赘述。

我只想改silkscreen的大小而不是assembly?那就隐藏assembly层,再change

关于字体的设置,如下图,不赘述

ADD->TEXT,写错了,想改?EDIT->TEXT

MARK点

不用加(就三个字还开一小节也是醉了)

Quick Reports

reports又来了:

tools->quick reports->dangling lines,via and antenna report

看看我的报告:

没毛病啊,怎么会这么多天线:

原来是我用过孔代替埋孔,这就导致天线报错:

看看官方报告策略:

Report methodology:

- Dangling lines have at least one end not connected.

- Dangling vias have one or no connection

- Plus are not a test, thieving or netshort property via.

- Antenna vias do not have connections on their start and end layers.

- Plus they are not a thieving vias.

- Optionally, VOLTAGE nets, testvias and through vias can be suppressed with

the environment variable report_antennavia. - Section may be suppressed by variable report_noantennavia.

- Not part of the current partition.

- To suppress items in dangle report add the OK_DANGLE property to the via

or connect line.

翻译翻译:

如果一个多层板的VIA ,没有任何连接或者只有一层有连线,判断为Dangling Vias(悬挂的过孔)

以四层板为例,如果信号只是从第2层连到第4层,则判断为: Antenna Vias (天线过孔)

原因为VIA所在第一层没任何连接,则为Antenna

如果信号从第1层连到第4层,则不报错

我的问题就是VIA剩一段没用,当然就被当做天线了

怎么办?不管它,这不是问题

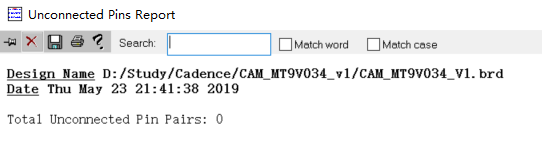

tools->quick reports->unconnected pins report

只有显示0,才算全联通

Total Unconnected Pin Pairs: 0

- 1

tools->quick reports->design rules check(drc) report

下面还有钻孔和光绘,今天就写到这里吧