- 1PostgreSQL 14安装和配置_postgresql14

- 2四元数和欧拉角转换_四元数转欧拉角公式

- 3实习|基于SSM的实习管理系统设计与实现(源码+数据库+文档)_实习管理系统的数据库设计

- 4ChatGPT 之 B2B 转化策略

- 5axios 请求拦截器&响应拦截器_axios请求拦截器和响应拦截器

- 6[面经] 5年前端 - 历时1个月收获7个offer

- 7Day:007(3) | Python爬虫:高效数据抓取的编程技术(scrapy框架使用)

- 8ubuntu虚拟机与windows之间实现复制粘贴功能_windows与ubuntu复制粘贴

- 9Git学习笔记之Git安装、创建版本库以及远程仓库_git安装、创建版本库、版本控制、远程仓库、分支管理、标签管理、连接及使用、组

- 10Jieba分词模式详解、词库的添加与删除、自定义词库失败的处理

VHDL的操作符_vhdl <=

赞

踩

一、赋值操作符

作用在于更新被赋值数据对象的值,数据对象主要是指信号和变量。VHDL赋值操作符也有信号赋值与变量赋值的区别,分别是:

- ”<="是信号赋值操作符,可以对标量型的信号类型对象或是矢量型信号类型对象整体赋值。

- ”<=“是变量赋值操作符,可以对变量、常量、属性(generic)和信号初始值的赋值或子程序对变量进行赋值。

- ”>=“是矢量型的数据对象的部分进行赋值。

以上赋值举例如下:

**--属性赋值操作** generic(data_bus:integer:=8); **--常量赋值操作** constant address_bus:integer range 1 to 7:=7; **--信号初始化赋值操作** signal datasum:std_logic_vector(7 downto 0):="00000000"; **--变量初始化赋值操作** variable temp:integer range 0 to 63:=0; variable seg:std_logic_vector(7 downto 0); **--信号赋值操作** datasum<="11000011"; **--变量赋值操作** temp:=23; **--信号部分赋值操作** signal datasum:std_logic_vector(7downto 0); datasum<=(7=>'0',6=>'1',others=>='0'); **--变量部分赋值操作** variable datasum:std_logic_vector(7 downto 0); datatemp:=(7 =>'0',6=>'1'.others=>'0');

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

二、逻辑操作符

VHDL支持7种逻辑操作符的运算,这些运算操作符所支持的常用数据类型有bit、bit_vector、std_logic、std_logic_vector等。

- not (对操作数按位取非操作,对应硬件的”非门“。

- and(对操作数按位取与操作,对应硬件的”与门“。

- or(对操作数按位取或操作,对应硬件的”或门“。

- nand(对操作数按位取与非操作,对应硬件的”与非门“。

- nor(对操作数按位取或非操作,对应硬件的”或非门“。

- xor(对操作数按位取异或操作,对应硬件的”异或门“。

- nxor(对操作数按位取同或操作,对应硬件的”同或门“。

连续逻辑操作符

当语句中出现连续多个逻辑操作符时,为了提高VHDL程序可读性与正确性,建议用括号加以分隔,如下:

dout<=not a and b xor c;--此语句有歧义

dout<=(not a) and (b xor c);--加上括号分隔更加清晰

- 1

- 2

三、算术操作符

VHDL算术操作符属于算法级的操作,只能操作相应的数据类型,而且有些是不可综合的。常用算术操作符主要有以下8种:

- “+”(对操作数取和)

- “-”(对操作数取差或对单个操作数取负)

- “*”(对操作数取积)

- “/”(对操作数取商)

- “* * " (对操作数作指数运算)

- “abs”(对操作数取绝对值运算)

- “mod”(对操作数取模运算)

- "rem“ (对操作数取余运算)

可以应用算术操作符的数据类型有integer、signed、unsigned和real。其中,real类型是不可综合的。如果VHDL程序引用ieee库的std_logic_signed或是std_logic_unsigned,则std_logic_vector类型的数据对象也可以应用算术操作符。由于算术操作符是算法级别的,可综合性不同则综合器就不同,一般有以下规则:

- “+”、“-” 和 “*” 操作符可综合

- “/”、“mod”和 “rem”一般不可综合,但如果操作数为2的整数幂时可综合。

- “* * “一般只支持左操作数是2的整数幂的情况。

- ”abs"一般不支持。

四、关系操作符

关系操作符运算结果都是布尔类型,要么为真(true)要么为假(false),对相同类型数据的对象进行数据大小比较。

- ”=“(相等操作符,比较两个数是否相等)

- ”/=“(不相等操作符,比较两个数是否不相等)

- ”<“(小于操作符,比较左操作数是否比右操作数小)

- ”>”(大于操作符)

- “<=”(小于等于操作符)

- ">=“(大于等于操作符)

使用注意问题:

- 在进行两个操作数的关系操作时,两个操作数的数据类型必须一致或是定义了相关的重载函数。

- ”=“、和 ”/=“ 使用所有的数据类型。

- ”<“、”>“、”<=“ 和 ”>=“适用的数据类型有整型、实型、位矢量及数组类型。

- ”<“ 操作数与信号赋值操作符一样,判断意义时,要根据上下文来理解。

五、移位操作符

移位操作符是对矢量数据对象进行移位操作。

- “sll”(逻辑左移操作符,最右边空出的位用"0"填充)

- “srl”(逻辑右移操作符,最左边空出的位用"0"填充)

- “sla”(算术左移操作符,最右边空出的位用原来最右边的值填充)

- “sra”(算术右移操作符,最左边空出的位用原来最左边的值填充)

- “rol”(循环左移操作符,最右边空出的位用原来最左边的值填充)

- “ror” (循环右移操作符,最左边空出的位用原来最右边的值填充)

位移操作符的使用格式如下:

操作数 移位操作符 进行移位的位数

假设 data=“11001010"举例如下:

data sll 1 --操作后 data="10010100"

data srl 1 --操作后 data="01100101"

data sla 1 --操作后 data="10010100"

data sra 1 --操作后 data="11100101"

data rol 1 --操作后 data="10010101"

data ror 1 --操作后 data="01100101"

使用移位操作符的操作数据类型必须是bit、boolean的数组或是std_logic_vector或是integer数据类型。

- 1

- 2

- 3

- 4

- 5

- 6

- 7

六、连接操作符

连续操作符(”&“)用不同的位来产生一个位数据更多的矢量。连续操作符可用于两个位的连接,也可以用于两个矢量的连接,如下:

signal ba,bb:std_logic;

signal da,db:std_logic_vector(1 downto 0);

signal data:std_logic_vector(3 downto 0);

da<=ba& bb;

db<=ba&'1';

data<=da&db;

data<=ba&'1'&da;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

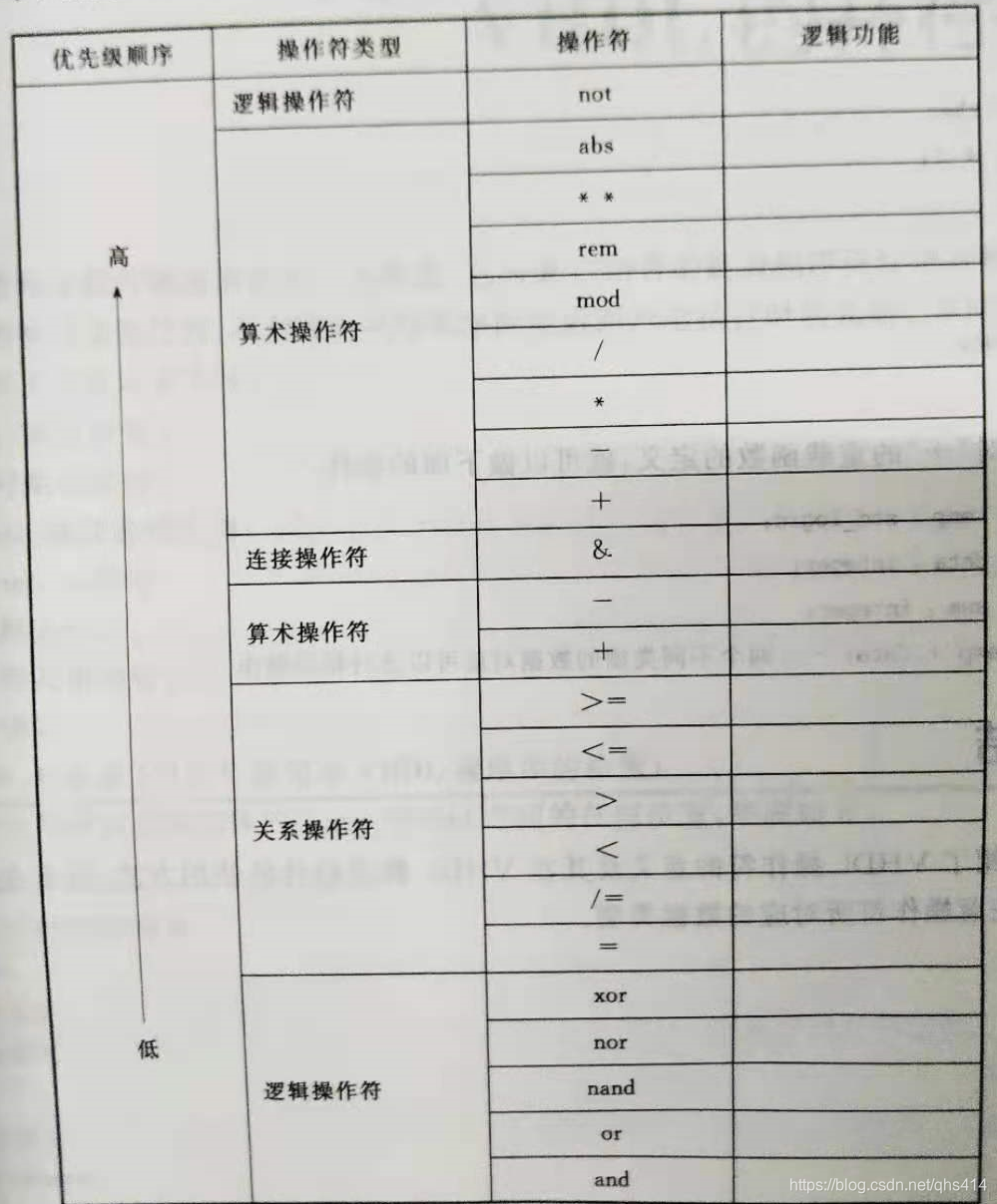

七、操作符的优先级

操作符优先级一般指的是同一语句中的优先级,当然括号也可以改变语句中操作的先后顺序。

八、操作符的重载

对于预定义操作符所作用操作数的数据类型必须一致。有时为了方便不同让数据类型的数据对象进行操作,就需要对操作符重新定义,这就是重载。

function "+"(1:std_logic;r:integer) return integer is

variable sum:integer:=0;

begin

if 1='1' then

sum:=r;

end if;

return sum;

end;

--有上面对”+“的重载函数的定义,就可进行下面的操作

variable temp:std_logic;

variable data:integer;

variable sum:integer;

sum:=temp+data;--两个不同类型的数据对就可以进行相加操作

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13