- 1PE-YOLO: Pyramid Enhancement Network for Dark Object Detection——论文笔记

- 2SecureRandom漏洞解析_securerandom seed

- 3数字图像处理学习笔记(三)——空间分辨率和灰度分辨率、等偏爱曲线

- 4内网渗透测试:初探远程桌面的安全问题_tson rdp-tcp# /dest:console

- 5【大数据开发运维解决方案】OGG实时同步Oracle数据到Kafka实施文档(供flink流式计算)_ogg kafka

- 6SourceTree 切换分支出现错误:The following untracked working tree files would be overwritten by checkout

- 7Flutter原理简介——Flutter 是怎么运转的?_flutter引擎原理

- 8Java开源框架集(全)_xsmjmx

- 9libevent源码解析--event,event_callback,event_base

- 10【无公网IP】在公网环境下Windows远程桌面Ubuntu 18.04_ubuntu 局域网桌面

千兆以太网MII接口类型_接口信号及时序介绍_千兆网数据时序

赞

踩

千兆以太网MII接口类型主要有GMII、RGMII、SGMII、TBI和RTBI 五种

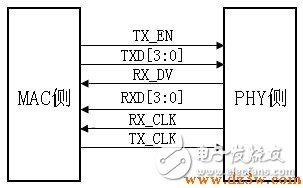

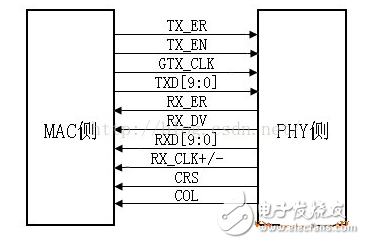

GMII接(如下图): 与MII接口相比,GMII的TX/RX数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作MII模式时,使用TX_CLK和8根数据线中的4根。 RGMII接口(如下图所示):

RGMII即Reduced GMII,是RGMII的简化版本,将接口信号线数量从24根减少到14根(COL/CRS端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。

RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。 TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;同样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。RGMII的收发时序如下图所示:

SGMII接口(如下图所示):

SGMII即Serial GMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样,参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用。收发都可以从数据中恢复出时钟。在TXD发送的串行数据中,每8比特数据会插入TX_EN/TX_ER 两比特控制信息,同样,在RXD接收数据中,每8比特数据会插入RX_DV/RX_ER 两比特控制信息,所以总的数据速率为1.25Gbps=625Mbps*2. 其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。8B/10B变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取,关于8B/10B变换知识。

TBI接口(如下图所示):

TBI即Ten Bit Interface的意思,接口数据位宽由GMII接口的8位增加到10位,其实,TBI接口跟GMII接口的差别不是很大,多出来的2位数据主要是因为在TBI接口下,MAC芯片在将数据发给PHY芯片之前进行了8B/10B变换(8B/10B变换本是在PHY芯片中完成的,前面已经说过了),另外,RX_CLK+/-是从接收数据中恢复出来的半频时钟,频率为62.5MHz,RX_CLK+/-不是差分信号,而是两个独立的信号,两者之间有180度的相位差,在这两个时钟的上升沿都采样数据。RX_CLK+/-也叫伪差分信号。除掉上面说到的之外,剩下的信号都跟GMII接口中的相同。大多数芯片的TBI接口和GMII接口兼容。在用作TBI接口时,CRS和COL一般不用。

RTBI接口(如下图所示):

RTBI即Reduced TBI,简化版TBI,接口数据位宽为5bit,时钟频率为125MHz,在时钟的上升沿和下降沿都采样数据,同RGMII接口一样,TX_EN线上会传送TX_EN和TX_ER两种信息,在时钟的上升沿传TX_EN,下降沿传TX_ER;RX_DV线上传送RX_DV和RX_ER两种信息,在RX_CLK上升沿传RX_DV,下降沿传RX_ER。