热门标签

热门文章

- 1windows下启动rabbitmq_windows启动rabbitmq

- 2使用GitHub制作一个高逼格的在线简历_在线简历word模板 github

- 3C++(运算符重载+赋值拷贝函数+日期类的书写)

- 4如何在Linux环境下安装Jenkins_linux安装jenkins

- 5mysql复制sql语句_MySQL复制表结构 表数据sql语句总结

- 6Milvus入门手册1.0_milvus中文文档

- 7Android11 open failed: EACCES (Permission denied)的解决方法_android open failed: eacces (permission denied)

- 8图论的基本知识

- 9数据结构之二叉搜索树底层实现洞若观火!

- 10GPT-4 API平替?性能媲美同时成本降低98%,斯坦福提出FrugalGPT,研究却惹争议

当前位置: article > 正文

数电和Verilog-宏定义_verilog 宏定义

作者:Cpp五条 | 2024-04-21 11:10:50

赞

踩

verilog 宏定义

A.8 宏定义

`define 定义全局参数

`define DATA_WIDTH 8

module

reg[`DATA_WIDTH-1:0] data; //这相当于定义 reg[7:0] data;

...

endmodule

- 1

- 2

- 3

- 4

- 5

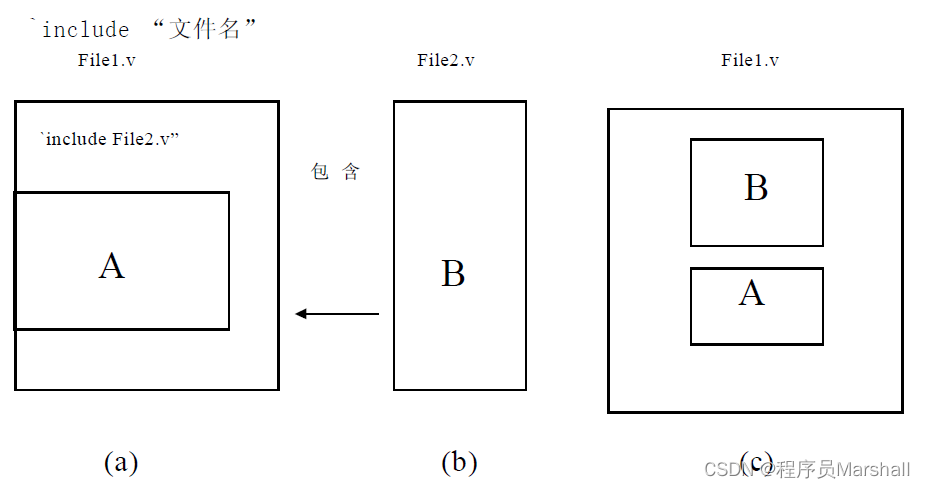

`include 文件包含

示例:

//文件aaa.v module aaa(a,b,out); input a, b; output out; wire out; assign out = a^b; endmodule //文件 bbb.v `include "aaa.v" module bbb(c,d,e,out); input c,d,e; output out; wire out_a; wire out; aaa aaa(.a(c),.b(d),.out(out_a)); assign out=e&out_a; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

`timescale 定义仿真时间单位和精度

上一节课我们讲到过

`timescale 10ns/1ns

- 1

这里置了时间单位是10ns,时间精度是1ns,除此之外

推荐阅读

相关标签