热门标签

热门文章

- 1算法设计:2.向下取整、向上取整符号_向上取整和向下取整

- 2crossover永久试用mac crossover试用期限已到还能用吗_银河麒麟crossover超过15天后续期方法

- 3[收藏] 三种 无限级分类 的数据库设计方案(菜单,,权限管理)_数据库无限层级分类设计方案

- 4先进先出页面置换算法详解_先进先出算法流程图

- 5注册Github账号详细教程【超详细篇--适合新手入门】_建立github账户

- 6【服务器部署系列-001】java环境部署_正式环境部署可以用java -jar方式部署吗

- 7多数据源 dynamic-datasource 模块使用_多数据源datasource如何使用

- 8macbook无法打开移动硬盘 为什么mac上显示不了移动硬盘_mac 移动硬盘不识别 磁盘管理也看不到

- 9SpringAMQP创建交换机和队列_java 使用spring qmpa 创建队列和交换机

- 10git 设置对文件名称大小写不敏感_git 大小写不敏感

当前位置: article > 正文

导航【FPGA模型机课程设计】_fpga导航

作者:Cpp五条 | 2024-06-09 23:42:33

赞

踩

fpga导航

前言

2023-5-22

在课程结束之后设置付费

2023-6-11

以下内容源自《创作模板三》

仅供学习交流使用

推荐

导航

10课程设计收尾及优秀作品展示答辩【FPGA模型机课程设计】

结果

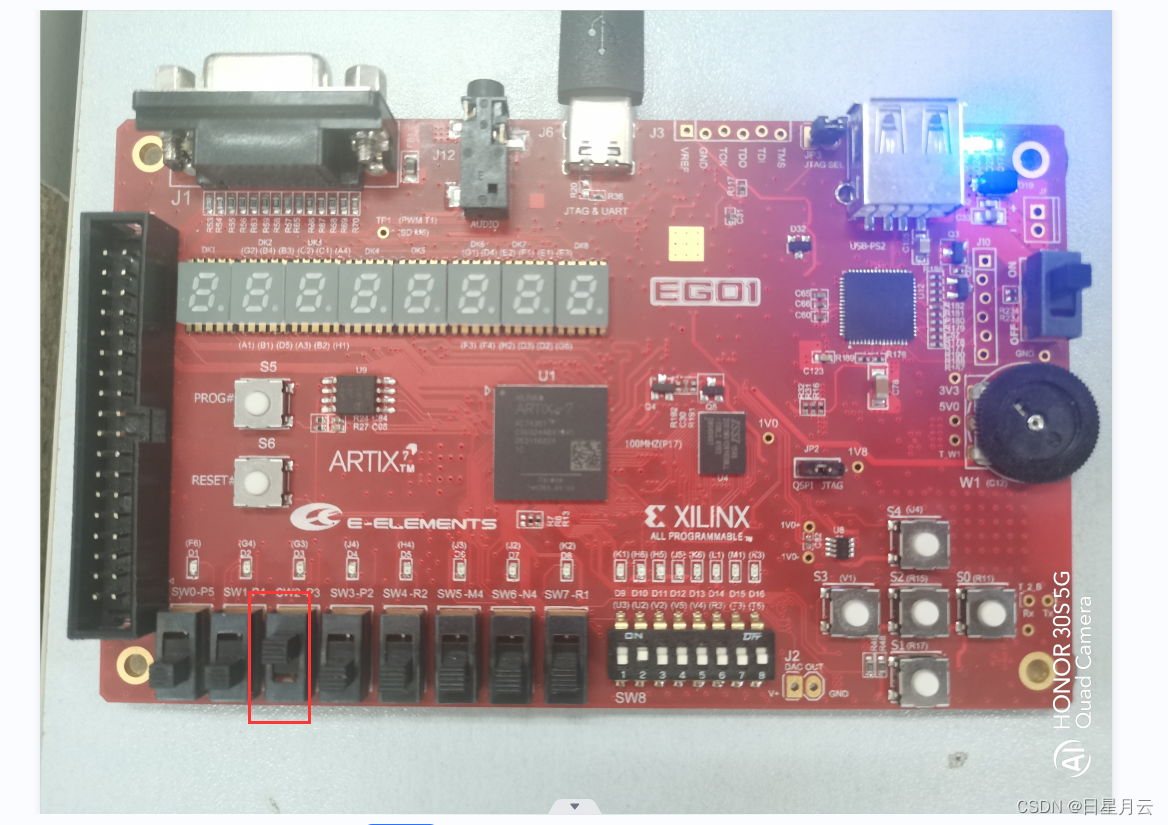

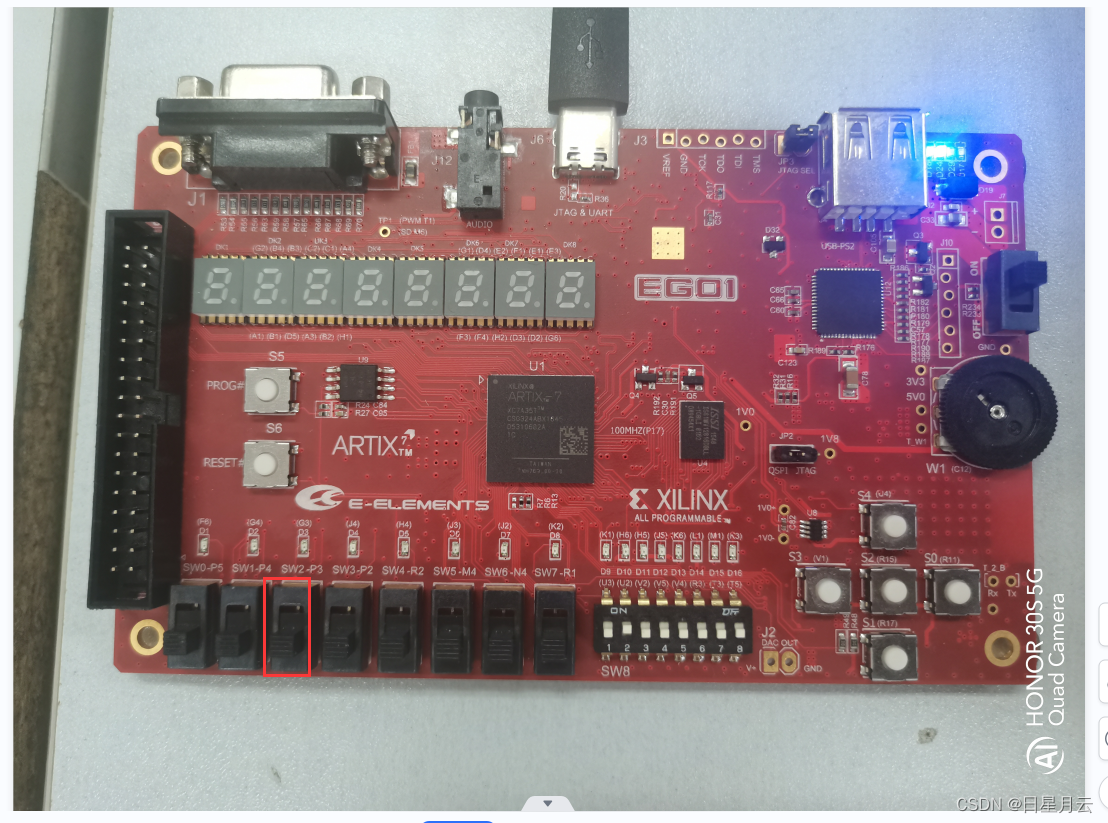

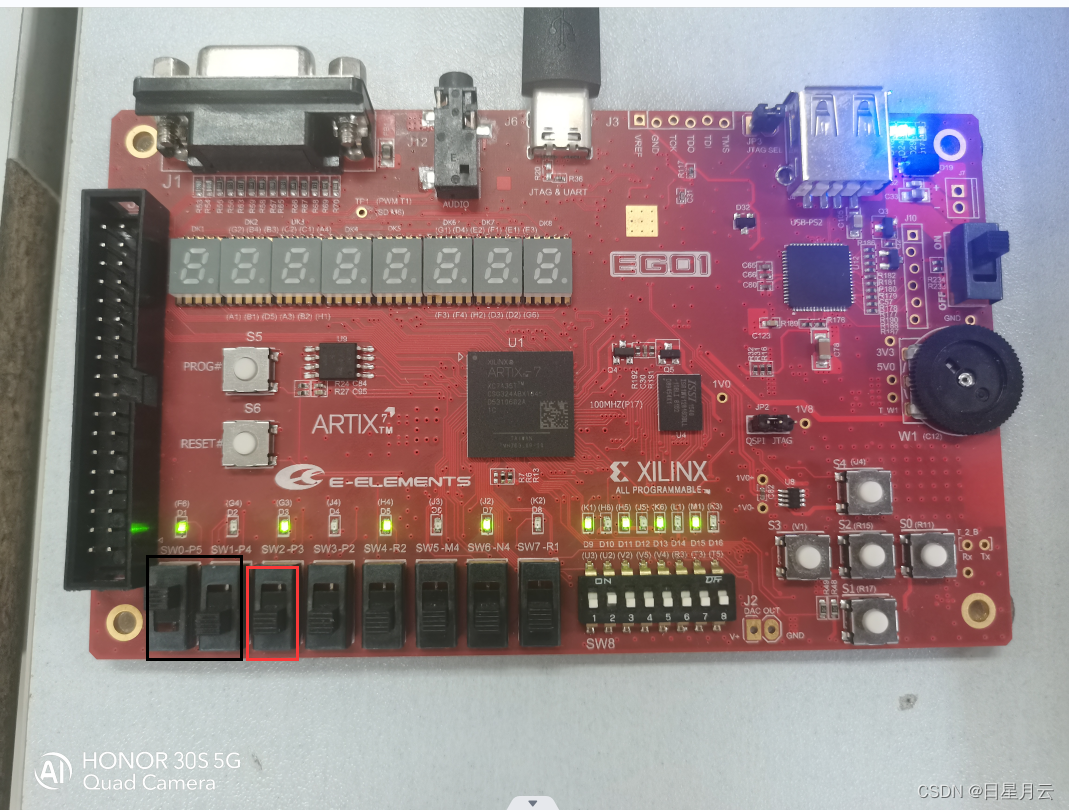

首先,需要把rst值置为有效

在约束文件中

可以看到rst连接的是P3

也就是SW2

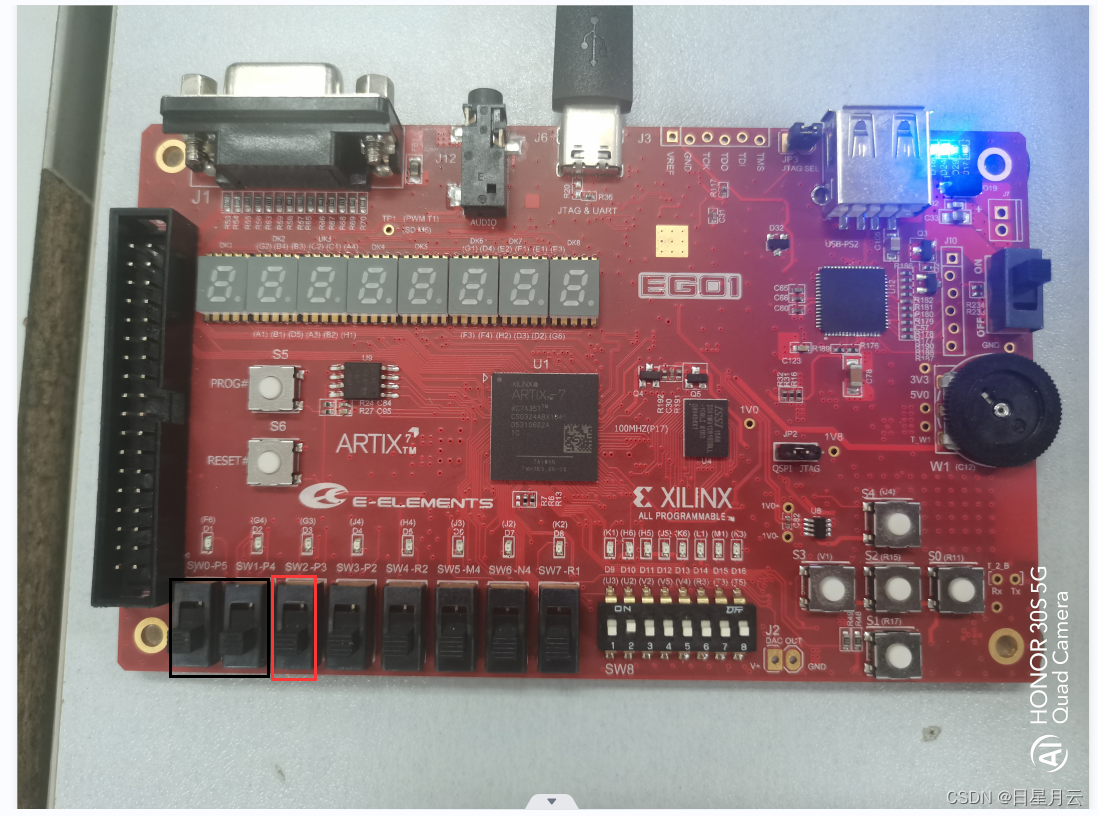

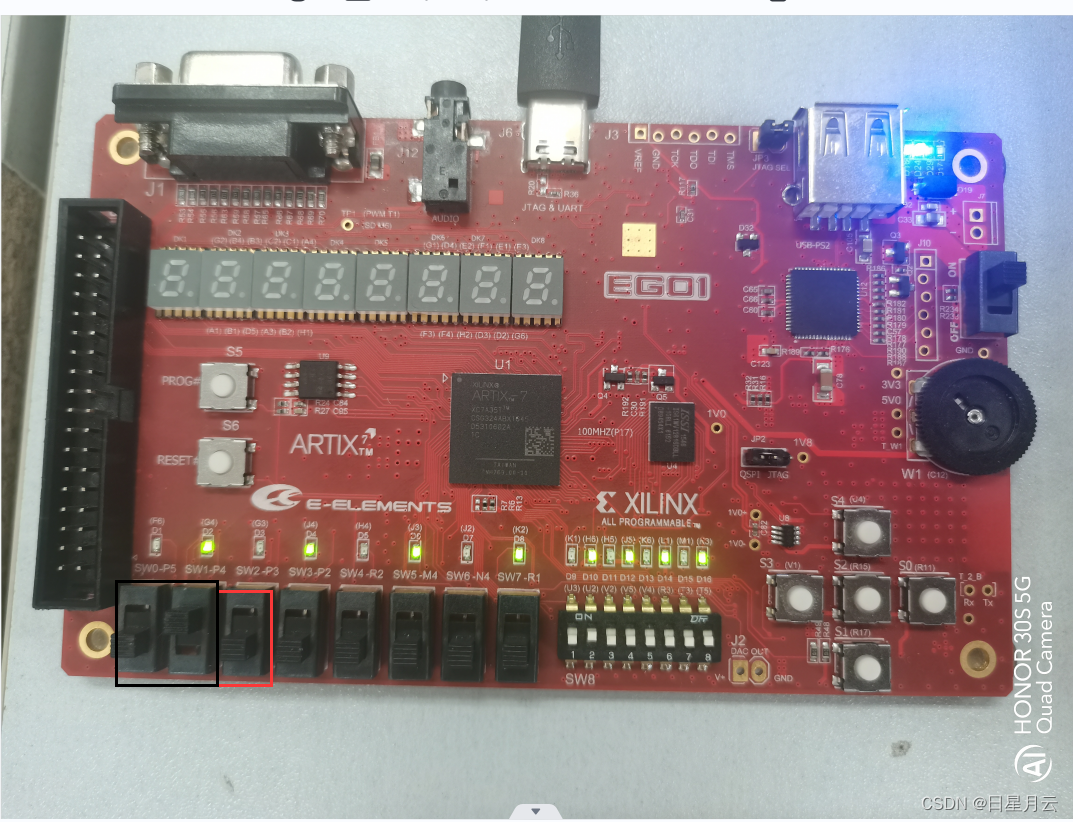

之后把rst置为无效

之后就可以正常运行了

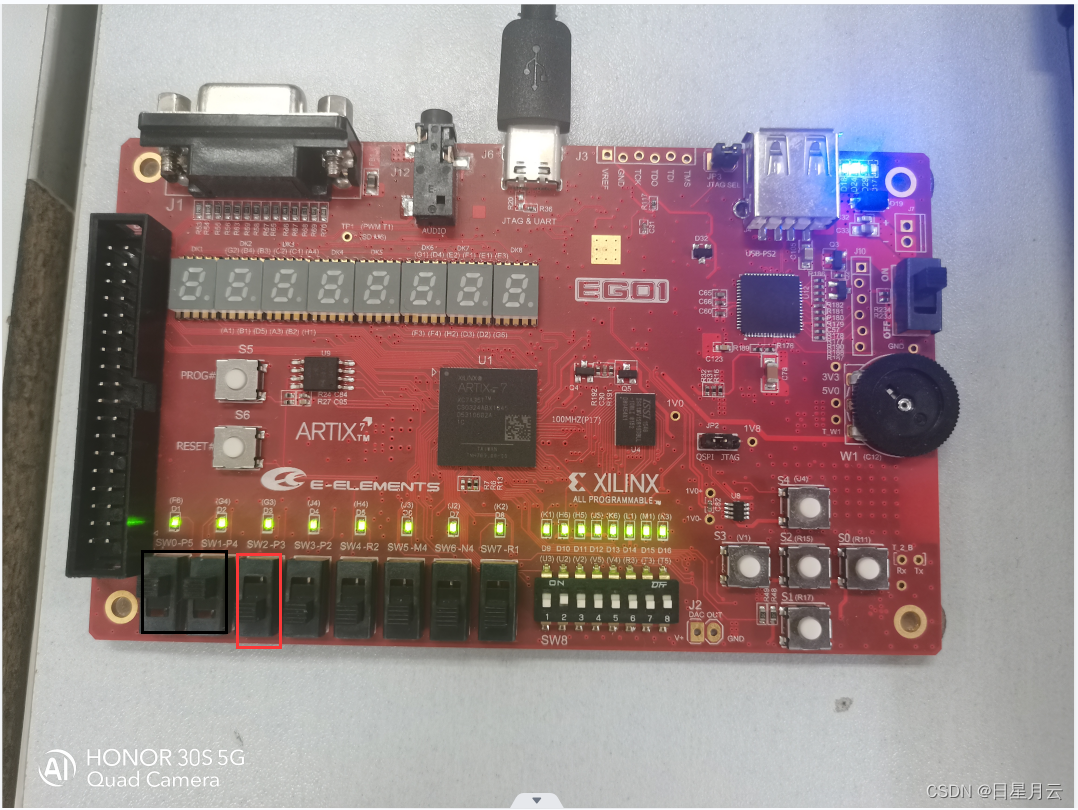

当开关0和1为2’b00时

灯从左往右是16’h0000

当开关0和1为2’b01时

灯从左往右是16’h5555

当开关0和1为2’b10时

灯从左往右是16’haaaa

当开关0和1为2’b11时

灯从左往右是16’hffff

附录

单周期CPU的代码可见

5模型机整体的联调【FPGA模型机课程设计】

单周期CPU下板的代码可见

8模型机在FPGA上的功能测试【FPGA模型机课程设计】

流水线CPU的代码可见

9对流水处理器进行改进和完善【FPGA模型机课程设计】

代码开发过程

1~11 单周期CPU

A~D 单周期CPU

E~F 单周期下板

①~② 单周期下板

I~IV 流水线CPU

- 1

- 2

- 3

- 4

- 5

单周期CPU的代码可见

5模型机整体的联调【FPGA模型机课程设计】

0 框架 1 define 编码 2 IF 取值 3 ID 译码 4 EX 执行 5 MEM 访存 6 DataMem 数据存储器 7 RegFile 存取 A HiLo 高位低位寄存器 B LLbit LLbit寄存器 C CP0 协处理器 D Ctrl 控制模块 8 MIPS 封装 9 InstMem 指令存储器 10 SOC 顶层 11 soc_tb

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

单周期CPU下板的代码可见

8模型机在FPGA上的功能测试【FPGA模型机课程设计】

0 框架 1 define 编码 2 IF 取值 3 ID 译码 4 EX 执行 5 MEM 访存 6 DataMem 数据存储器 7 RegFile 存取 A HiLo 高位低位寄存器 B LLbit LLbit寄存器 C CP0 协处理器 D Ctrl 控制模块 E MIOC 接口 F IO 外设 8 MIPS 封装 9 InstMem 指令存储器 10 SoC 顶层 11 soc_tb ① clk_div 时钟分频模块 ② mips.xdc

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

流水线CPU的代码可见

9对流水处理器进行改进和完善【FPGA模型机课程设计】

0 框架 1 define 编码 2 IF 取值 I IF_ID 流水寄存器 3 ID 译码 II ID_EX 流水寄存器 4 EX 执行 III EX_MEM 流水寄存器 5 MEM 访存 IV MEM_WB 流水寄存器 6 DataMem 数据存储器 7 RegFile 寄存器文件 A HiLo 高位低位寄存器 B LLbit LLbit寄存器 C CP0 协处理器 D Ctrl 控制模块 8 MIPS 封装 9 InstMem 指令存储器 10 SOC 顶层 11 soc_tb

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

最后

2023-6-2

你对我百般注视,

并不能构成万分之一的我,

却是一览无余的你。

祝大家逢考必过

点赞收藏关注哦

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Cpp五条/article/detail/696268

推荐阅读

相关标签