- 1tomcat服务器发布网站的方式小结_tomcat安装部署网页发布总结

- 2(笔记整合)归并排序、快速排序_t(n)=t(n/2)+t(n/4)+cn t(1)=1

- 3GAN在图像分割中的应用_gan做分割

- 4机器学习“CUDA”、“飞桨AI Studio”、“PyCharm”、 “Python”、“ Anaconda”、“numpy”、“飞桨PaddlePaddle”辨析_aistudio cudnn

- 5windows远程桌面_保存密码_mstsc 密码保存

- 6git:从远程仓库更新代码到本地仓库_同一个仓库,别人更新了文件,我这边怎么down下来呢

- 7将master分支内容合并到dev分支_merge master into dev

- 8PyQt5入门学习(一)【PyQt5及PyQt5-tools的安装】

- 9Docker容器嵌入式开发:Ubuntu上配置Spark环境的基本步骤

- 10Odoo服务器搭建——保姆级教程_odoo安装部署

verilog always语法_Verilog代码转VHDL代码经验总结

赞

踩

Verilog语言和VHDL语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把Verilog代码转换为VHDL代码。本文以通用的XHDL工具为例对Verilog转换到VHDL过程中存在的问题进行了总结,欢迎批评指正。

当我们刚开始学习FPGA时,一定会遇到一个问题:

学习Verilog还是VHDL?

等我们学习FPGA到一定程度参加面试时,面试者也会问你一个问题:

你以前用Verilog还是VHDL开发?

你已经习惯某种语言,也发现语言不是学习FPGA时需要考虑的问题,它仅仅是硬件描述语言工具而已。可是,当你发现一份和你使用语言不同的代码作为参考时,你又开始想:

我以后的工作是不是要二种语言都会,这样工作才会得心应手?

事实上,两种语言之间是可以相互转换的。

对于我们做FPGA开发人员来说,如何快速在Verilog和VHDL之间互转,加快开发产品的进度,而不是因为只懂某一种语言而局限了自己的开发。

Vivado可以看两种语言的差异

Verilog与VHDL语法是互通且相互对应的,如何查看二者对同一硬件结构的描述,可以借助EDA工具,如Vivado,打开Vivado后它里面的语言模板后,也可以对比查看Verilog和VHDL之间的差异。

XHDL软件

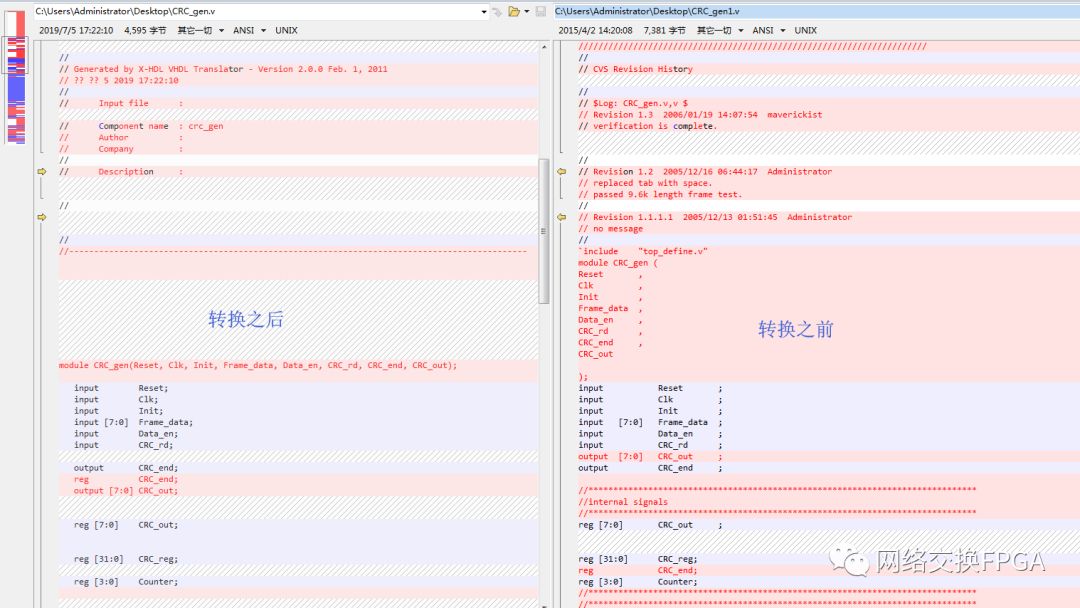

转换所用软件如下图所示:

上图是把转换成VHDL格式的代码,再转换回verilog后与原代码对比的图,可以看出,一些注释之类的信息都没有了,原来的代码规范和风格也发生了变化。

在转换的过程,该软件对代码中的汉语注释不支持,如果出现汉字就无法转换。

笔者之前就曾试着写过Verilog转VHDL代码的工具,见:Verilog HDL代码转VHDL代码,无奈因为不是软件开发出身,写出来的东西通用性和完善性很差。写到此处,再次想起汉天下董事长杨清华所说的话,互联网讲究的是差异化的商业模式,很牛的产品定义,早期不看销售额而看流量,越快越好。这对IC是很可怕的事情,让整个产业变得很浮躁。互联网的模式,在某种程度上是毒瘤。发展集成电路芯片,需要把互联网的模式认知去除。芯片行业需要长期积累、持续关注,需要八年、十年的积累,这个耐心和耐性很重要。

试想一下,如果这么一个简单的小软件是互联网领域经常用到的,估计早已经遍地都是了吧,并且也都很好用呢!

以下仅对Verilog转VHDL过程中出现的问题进行说明。

Xhdl软件转换后状态机的问题

含有状态机的Verilog代码被xhdl软件转换后会出现两种情况:

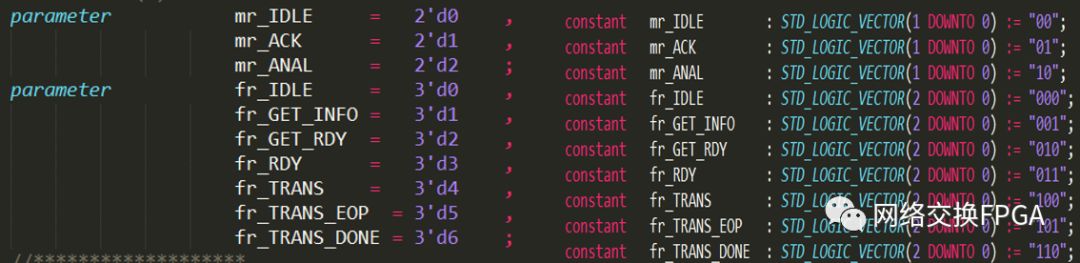

1、当verilog代码中parameter常量写在紧挨着端口位置时,xhdl软件会将其转换为vhdl中的generic内的可传递的参数,如图:

2、当parameter在其它地方出现时,xhdl会将其转换为constant常量,如图:

2、当parameter在其它地方出现时,xhdl会将其转换为constant常量,如图:

无论哪种方式,将其中有错误的地方改正后,都不会出现状态机运行出错,也就是不用将这种状态机书写方式更改为vhdl语法中专门的状态机书写方式。

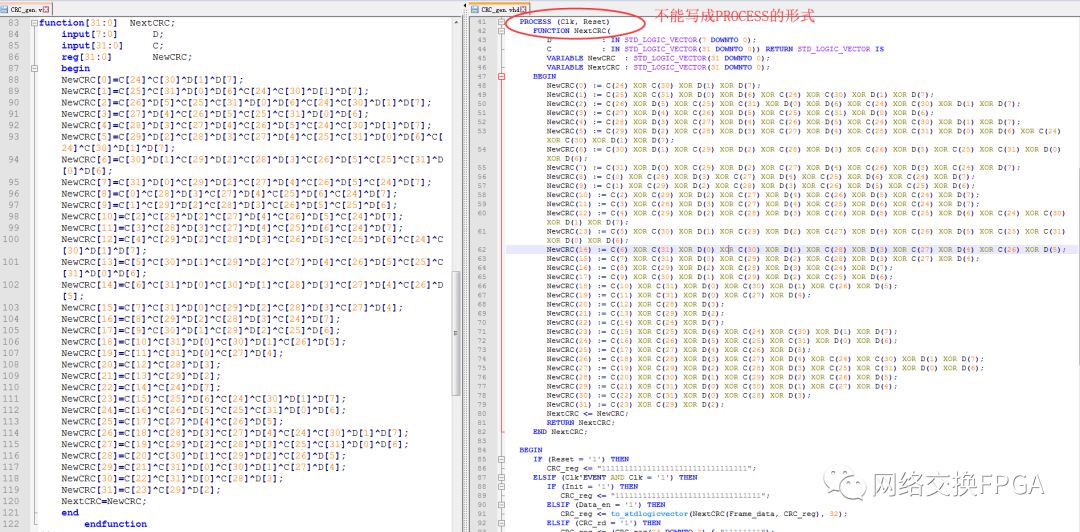

function转换位置出现问题

在用xhdl软件完成转换后会出现function写在了process块内的情况,出现此问题应将function改在architecture下面(与定义信号在相同的位置)。

信号只能赋值给与它位宽类型相同的信号

如下图中的两个信号:

b <= a;

在verilog中此种赋值方式意思是将a的前3位赋值给b,但是在vhdl中此种赋值方式会报出位宽不匹配的错误,应将其更改为:

b <= a(2 downto 0);

同时需要注意a、b的数据类型必须相同,如图中必须都为std_logic_vector类型。

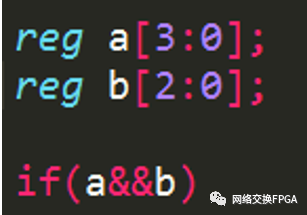

没有逻辑与,需用其它办法解决

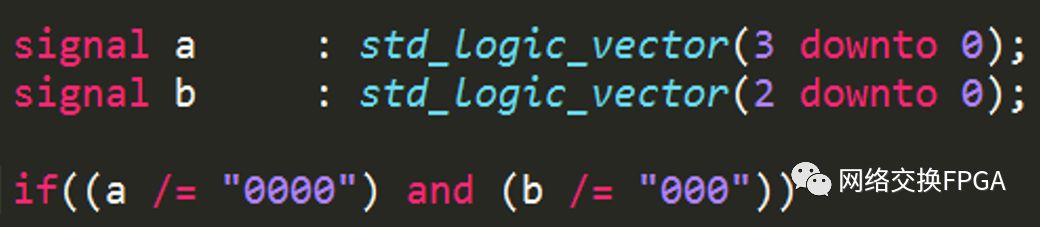

在vhdl中没有逻辑与(verilog中的&&),只有按位与(verilog中的&,vhdl中的and),所以verilog中的逻辑与,在vhdl中有时需要用等价的方式替换,比如:

需要替换为:

注意数据类型转换符号使用的是否正确

在vhdl中有多种数据类型,它们之间可以通过数据类型转换符号相互转换。在xhdl软件中,数据类型转换一般都会出现错误,具体的原因是转换符号使用错误,而在vhdl的语法书上介绍的并不全面。下面介绍几中常用的数据类型转换符号:

1、IEEE.std_logic_1164.all库中包含的:

(1)bit_vector to std_logic_vector :

= to_stdlogicvector(bv_sig);

(2)std_logic_vector to bit_vector :

= to_bitvector();

2、IEEE.std_logic_arith.all库中包含的:

integer to std_logic_vector :

= CONV_STD_LOGIC_VECTOR(,);

3、IEEE.std_logic_signed.all库中包含的:

std_logic_vector to integer :

= CONV_INTEGER();

注意:选用某种数据类型转换符号的时候一定要确认是否包含了相应的库。

其它转换符号可以在如下图的ise软件相应的目录下查找

if后的判断语句在某些情况会出现语法没错误逻辑出现错误

此种情况比较少见,但是一般很难发现,只有通过大量仿真找到错误。具体情况如下图:

原verilog代码:

if((MDR_port_i & outport) == 32'b0)Xhdl软件转换后语法无错误逻辑出现错误:

IF((MDR_port_i /= "0000000000000000000000000000000") AND outport /= "0000000000000000000000000000000" = false)修改后:

IF((MDR_port_i AND outport) = "0000000000000000000000000000000" )个人总结:在原verilog代码中,当if后的判断句出现按位与(&)时,Xhdl软件转换成vhdl后很大可能会出现语法正确逻辑错误。

并置运算时遇到的问题

由于在verilog语法中,位宽不同的两个信号也可以相互赋值,但是在vhdl中对此有严格要求位宽相同,而xhdl软件在转换的时候不会检测这些,所以经常会出现位宽不匹配的情况,尤其是在并置运算时,所以要严格检查并置后的位宽与所赋值信号是否相同。

在verilog中某一信号可以赋值给几个并置的信号,但是在vhdl中不允许这么做,除非左侧并置的都为std_logic类型信号,右侧为std_logic_vector类型信号,注意此时在vhdl中并不是用“&”这个并置运算符,而是“,”。(bit以及bit_vector是否有相似功能暂时未知)具体情况如图:

错误,因为b是std_logic_vector类型

正确情况如下图:

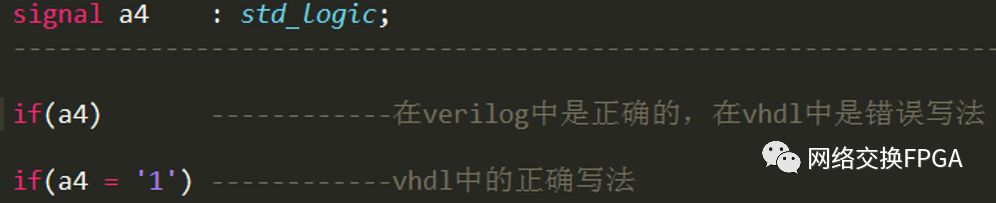

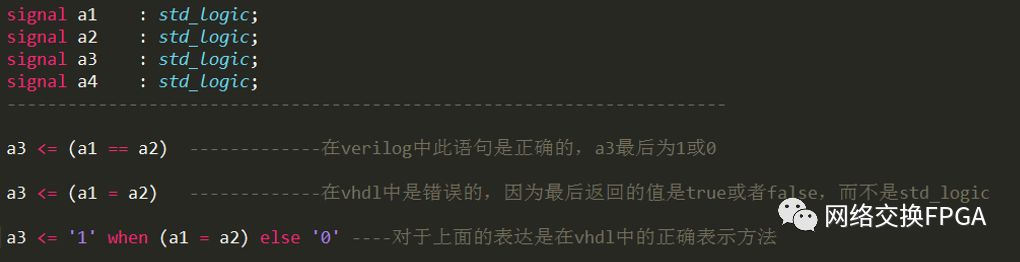

Bool类型的运用以及会出现的问题

在verilog中几个信号经过关系运算后返回的值是1或者0,但是在vhdl中返回的确是bool类型的值,也就是说返回的是true或者false。

1、vhdl中在if后的判断条件最后必须为布尔类型,如图:

2、verilog和vhdl中信号经过关系运算后返回值的区别,如图:

When-else语句不能用在process块内

软件转换后的when-else语句常常被放在process块内,导致出现问题。因为when-else语句是并行信号赋值语句,它本身就相当于一个进程process,因此不能放在进程体中。进程是不能够嵌套的。

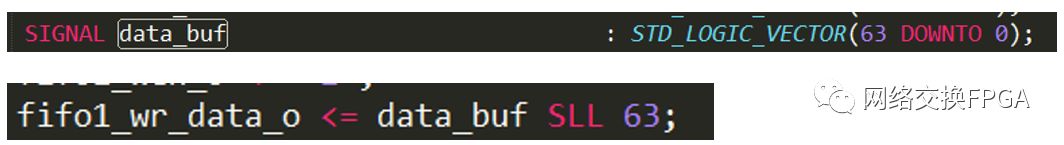

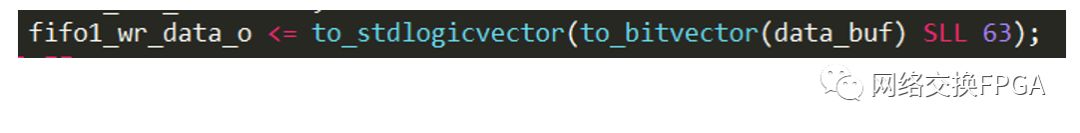

位移操作左侧为bit类型,右侧为integer类型

Verilog中的位移运算经xhdl软件转换后必出现错误,错误的原因是转换成vhdl代码后位移符号两侧数据类型出错,如图

错误情况:

修改后的正确格式:

位移符号左侧应该是bit类型,所以将std_logic_vector类型的信号转换为bit类型,数字“63”默认为integer类型,位移后的结果仍然为bit类型,所以需要将其装换为std_logic_vector类型,并赋值给相同类型的信号。

真双口RAM的IP核的使能信号

注意真双口RAM的IP核的使能信号的数据类型,在顶层例化时要注意要只取使能信号第0位的与信号连接的方式。

由于真双口RAM在例化后“wea”“web”为std_logic_vector(0 downto 0),所以要取这两个端口的0位与信号连接。

while循环

在vhdl中不要使用while循环,会出现问题,将while循环换为for循环

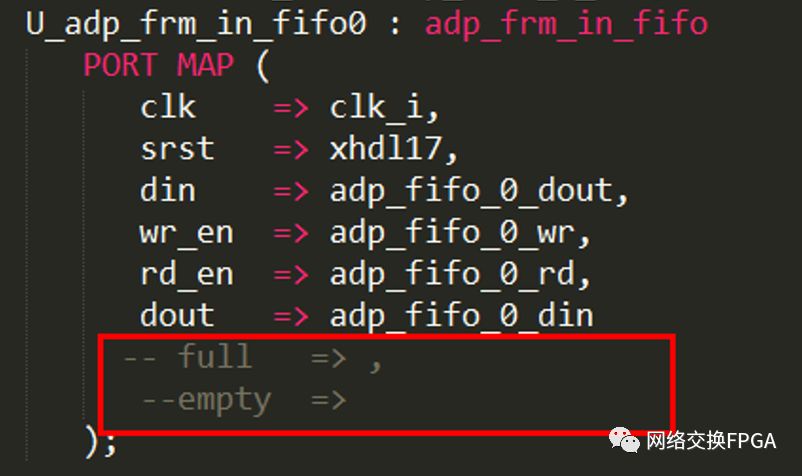

top层输入输出端口不接信号的情况

1、在top层,例化的某个模块输出端口不连信号时,只需要在例化此模块处将此端口删除或注释掉即可,如图:

2、当在top层例化的某一模块的输入端口无信号连接时,必须将此端口处连接“U(未初始化)”状态(理论上讲将“U”换为“Z”也可以,但实际上会报出语法错误,在vhdl语法书上说是连接“open”状态,实际测试也会报错),如图:

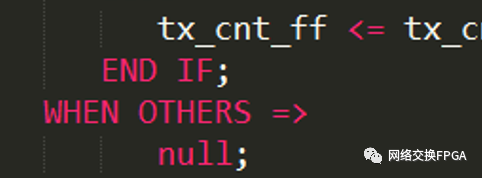

case语句的注意事项

在vhdl的case语句的语法中,只有分支将所有条件都覆盖后才可以不使用“when others =>”(相当于verilog的default),但是实际中几乎不可能包括所有情况(因为必须连高阻,不定态等状态都包含进去),所以需要在case语句分支条件增加“when others =>”。对于原verilog代码中default后没有任何表达式的情况,在vhdl中对应的地方写上“null”,如图:

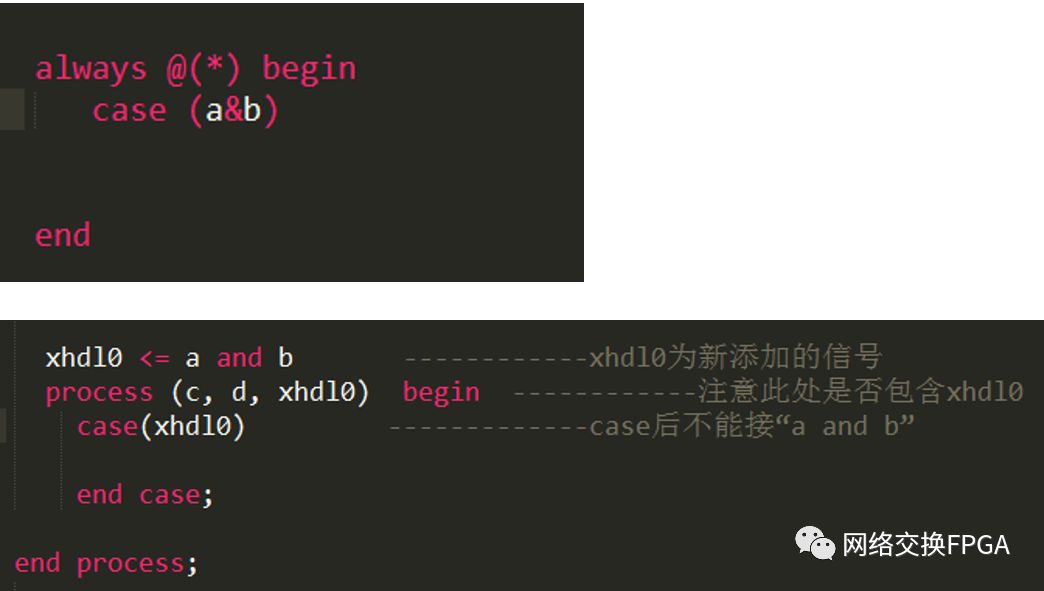

组合逻辑转换时遇到的问题

当含有“always(*)”这类组合逻辑的verilog代码经xhdl软件转换后以下两种情况需要注意:

1、当是三段式状态机中的“always(*)”被转换时,注意去除其中的状态常量。

2、由于vhdl规定case后的判断条件必须是单一信号,所以当原verilog代码中,case后面的判断条件不是单一信号,而是几个信号的组合时,xhdl软件会将这几个信号的组合用组合逻辑赋给一个新的信号,后将新的信号放在case的判断逻辑处,此时需要注意查看组合逻辑块的触发信号是否包含此新生成的信号,具体如图:

仿真时注意时钟的问题(上板不会出现此问题)

在使用modelsim对vhdl代码进行仿真时,会出现如图的情况:

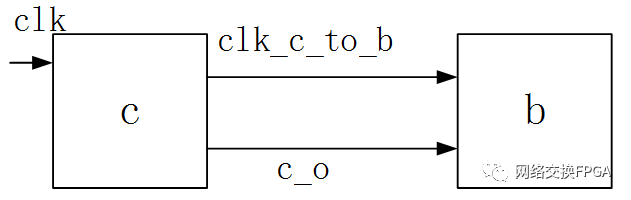

具体的操作就是对c_o信号打拍,可以发现第一拍没有打上(实际是打上了),该测试程序的原理图如图:

C将时钟clk_c_to_b和一个信号c_o传递给b,c_o使用时钟clk生成的,在b内用c给的时钟来给c_o打拍。最后发现仿真之所以会出现上面的情况,主要是因为在模块c内对时钟clk进行了一次处理后赋给b(如在c内部进行了clk_c_to_b <= clk),导致出现了如下的波形情况:

如果你在使用VHDL与Verilog转换过程中遇到了上面没有提到的问题,欢迎留言讨论。或者你有更好的办法完成两种语言之间的转换,也请不吝赐教!

全文完。

扫描下方二维码,感谢您的关注!