- 1【完结】cyの破三之旅(下篇)(20240401~20240421)

- 2使用CRNN-CTC-CenterLoss进行高效文字识别

- 3Git基于master创建新分支_git如何基于master创建自己的分支

- 4只需三步,手把手带你在本地部署运行大模型_本地部署大模型

- 5如何将git的commit进行聚合??一文搞懂如何用rebase将commit合并!!_git rebase合并commit

- 62022春招季,在线招聘新变

- 7Jenkins连接gitlab报错:returned status code 128

- 8Ubuntu20.04安装配置stable diffusion 超详细教程_ubuntu20.04 安装stable diffu

- 9【产品经理】微信小程序隐私保护指引

- 10万字长文:AI产品经理视角的ChatGPT全解析

数字后端面试问答No.16-18_zero wire load model

赞

踩

数字后端面试问答No.16-18

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

今天继续更新三道数字后端设计实现笔试面试题目。第一道题为 CDC 问题及其解决方案。第二道题考察 setup 及 hold check 机制。第三道题考察逻辑综合阶段常用的几种 wire load model。小编目前已经开通知识星球,建立了一个连接你和我私密交流的 IC 圈子,欢迎各位上车,进行深度交流和提问。

1.What is CDC (Clock Domain Crossing)? And how to fix CDC metastability?

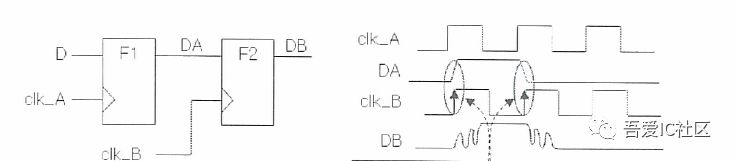

被不同 clock driven 的两个寄存器,进行 timing check 时会导致亚稳的状态,如图 1 所示。左侧为电路图,右侧为对应的波形图。当 clk_ B 在采样时,DA 的数据还在发生变化,F2 采集到的数据就不准确,甚至错误。所以这样的电路设计是存在问题的。

图 1 跨时钟域电路

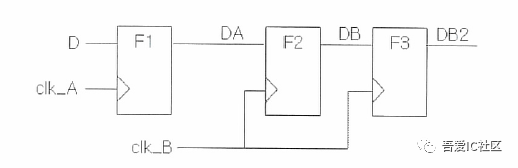

那么,我们如何解决这个问题呢?一般我们常用的方法是 “打一拍做同步处理”(将 F2 和 F3 的时钟连在一起),电路图如图 2 所示。

图 2 异步电路做同步处理的电路设计

2. The period of CLK1 is 10ns, waveform {0 5}. And the period of CLK2 is 25ns,CLK1 and CLK2 are synchronous.Please explain the setup and hold check.

这道题很简单,之前推送过很多道类似的题目。大家自己画画波形图,看看 PT 会选择那个沿做 setup 和 hold 的 check。

深入浅出讲透 set_multicycle_path,从此彻底掌握它

3.What type wire load model are often used during synthesis?

-

zero wire load model

-

基于 fanout 的 WLM

-

基于物理位置的 wire load model

这几天,粉丝越来越多了,提问的人也越来越多了。有的是重复的问题,有的则是新问题。对于之前我回答过的问题,想通过找历史回答记录,似乎很困难(要么去翻群历史消息,要么去翻个人历史消息)。

所以个人觉得这个不是长久之计,知识和解答不容易随着时间的积累而慢慢沉淀下来。所以小编注册了知识星球(原小密圈),建立了一个数字后端技术交流圈(需要付费,志愿加入原则,目前已经有两位星球成员了,在此表示感谢!)。在这里,各位可以提问,小编会在 24 小时内给予解答(也可以发表你对某个知识点的看法,或者职业发展规划等)。反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。

相关文章推荐(不看保证后悔)

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

秒杀数字后端实现中 clock gating 使能端 setup violation 问题

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

Scan chain reordering 怎么用你知道吗?

数字后端实现时 congestion 比较严重,你 hold 得住吗?

Final netlist release 前,你应该做好哪些工作?

深入浅出讲透 set_multicycle_path,从此彻底掌握它

数字后端实现时 congestion 比较严重,你 hold 得住吗?

时钟树综合(clock tree synthesis)基础篇

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击 “在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

-

基于 90nm 项目案例实现教程(ICC 和 Innovus 配套教程)

-

数字 IC 行业百科全书

吾爱 IC 社区知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近八年,拥有55nm,40nm,28nm,22nm,14nm等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有 880 星球成员,感谢这880童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

欢迎关注 “吾爱 IC 社区”

微信号:ic-backend2018