- 1Pandas中explode()函数的应用与实战_pandas explode

- 2java ppt控件_Java版PPT操作控件Spire.Presentation v3.3.5新版来袭!支持转换GroupShape到图片...

- 32024 信息安全毕业设计(论文)选题题目合集 最新版_信息安全专业毕业设计

- 4windows安装cuda 11.8以及tensorflow-gpu 2.6_cuda11.8对应的tensorflow

- 5练习时长 1 年 2 个月的 Java 菜鸡练习生最近面经,期望25K

- 6干货预警,企业级Android车载系统开发手册,开源分享!_android车载开发学习手册 百度网盘

- 7部署Pritunl

- 8机器学习参数寻优:方法、实例与分析

- 9iVX虽然是图形化编程,但“我们不一样”_psivx

- 10关于我用iVX沉浸式体验了一把0代码创建飞机大战这件事_ivx项目实例

STM32时钟系统(韦东山7天物联网智能家居实战训练营 学习笔记)_韦东山智能家居

赞

踩

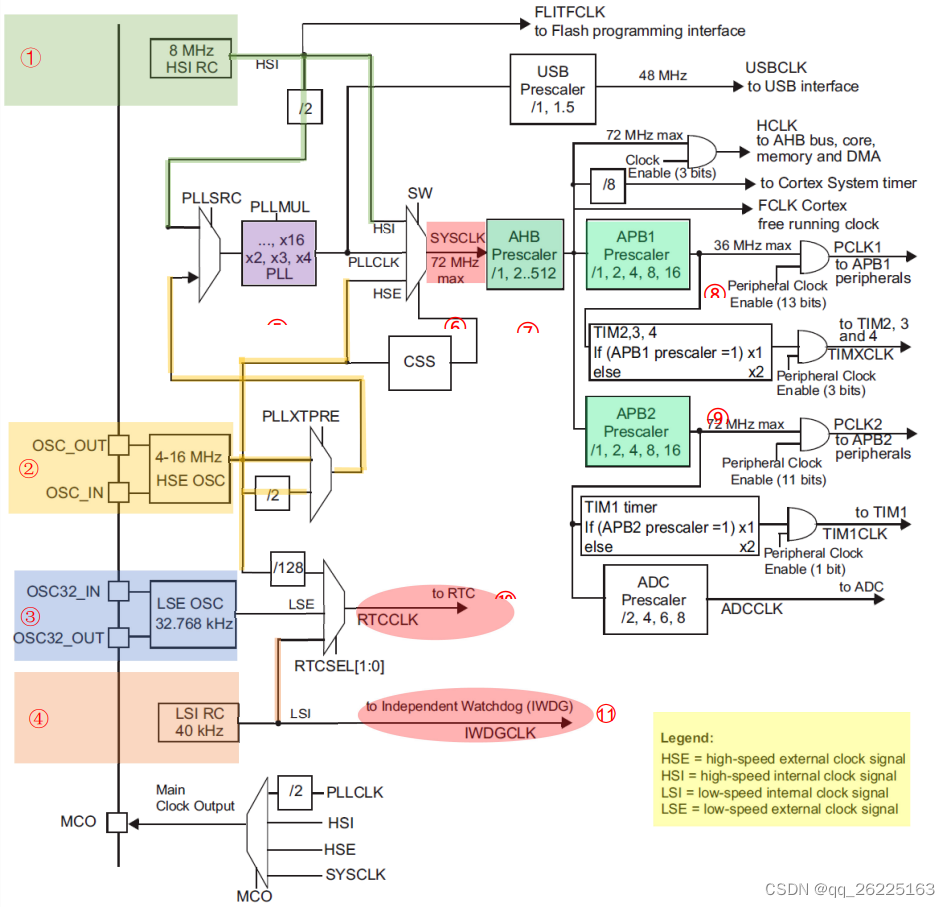

时钟对于一款芯片非常重要,其作用相当于人的心脏,人只有在心率正常稳定的情况下才能健康生活,

同样的,芯片只有工作在合法正常的时钟频率下才能保证程序得到正常的运行

左侧的①HSI(内部高速时钟)、

②HSE(外部高速时钟)、③LSE(外部低速时钟)、④LSI(内部低速时钟)为时钟源,右侧的各种片上外

设。图中矩形框内用“/”加数字表示分频器,如: ,数字表示几分频;矩形框内用“X”加数字表示的为

锁相环,如: ,数字表示几倍频;倒梯形表示选择器,长边表示多个输入,短边表示选择其中一个输出,

如: 。

⑥系统时钟SYSCLK最高为72MHz,从图中左侧的选择器SW可以看到来源有三个,分别是:①内部高速

时钟HSI(绿色)、⑤锁相环时钟PLLCLK(紫色)和②外部高速时钟HSE(黄色),而锁相环时钟PLLCLK

由内部高速时钟HSI和外部高速时钟HSE,经过分频和PLL锁相环倍频而来

系统时钟SYSCLK最高为72MHz,从图中左侧的选择器SW可以看到来源有三个,分别是:①内部高速

时钟HSI(绿色)、⑤锁相环时钟PLLCLK(紫色)和②外部高速时钟HSE(黄色),而锁相环时钟PLLCLK

由内部高速时钟HSI和外部高速时钟HSE,经过分频和PLL锁相环倍频而来。

内部高速时钟HSI可直接经过选择器SW给系统时钟SYSCLK,此时系统时钟SYSCLK为8MHz;内部高

速时钟HSI先2分频,再经过选择器PLLSRC进入锁相环PLLMUL,最大倍频为16倍,得到64MHz的锁相环时

钟PLLCLK给系统时钟SYSCLK;当外部高速时钟HSE(假设外接晶振为8MHz时)直接给选择器SW,则系

统时钟SYSCLK为8MHz;当外部高速时钟HSE(假设外接晶振为8MHz时)直接经过选择器PLLXTPRE给

PLLSRC,再经过PLLMUL 9倍频,得到72MHz的PLLCLK给系统时钟SYSCLK。

⑩RTCCLK(实时时钟)的时钟源也有三个,分别是②外部高速时钟HSE的128倍分频(黄色)、③外

部低速时钟LSE的32.768kHz(蓝色)、④内部低速时钟LSI的40kHz(橙色)。

○11 IWDGCLK(独立看门狗)的时钟来源于④内部低速时钟LSI的40kHz(橙色)。