- 1【ROS2】使用摄像头功能包 usb_cam_ros2 摄像头

- 2何使用 NMAP 命令进行网络扫描(非常详细)零基础入门到精通,收藏这一篇就够了_nmap得到的cpe

- 3Testbench基本入门_testbench入门

- 4回文串问题总结_7-1 回文串问题

- 5从零开始学习CANoe(一)—— 新建工程_canoe新建工程

- 6【文献阅读笔记】之基于Deeplabv3+的图像语义分割优化方法_基于改进deeplabv3+网络的马铃薯根系图像分割方法

- 7Linux c++ onvif客户端开发(1): 根据wsdl生成cpp源文件_libonvif

- 8Flink入门及实战(1)_flink入门与实战

- 9DFI 5.0接口协议_dfi协议

- 10Java设计模式之一:观察者模式_java观察者模式

FPGA基础知识

赞

踩

FPGA是在PAL、PLA和CPLD等可编程器件的基础上进一步发展起来的一种更复杂的可编程逻辑器件。它是ASIC领域中的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能釆用一种易于反复配置的结构,查找表-Look Up Table,LUT,可以很好地满足这一要求。目前,主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash/熔丝/反熔丝工艺的查找表结构。

1 查找表结构及功能

由布尔代数理论可知,对于一个n输入的逻辑运算,最多产生2^n个不同的组合。所以,如果预先将相应的结果保存在一个存储单元中,就相当于实现了与非门电路的功能。

FPGA的原理的实质,就是通过配置文件对查找表进行配置,从而在相同的电路情况下实现了不同的逻辑功能。

1.1 输入查找表结构

LUT本质就是一个RAM。自FPGA诞生以来,多使用4输入的LUT,可以看成一个包含四位地址线的RAM。当设计者通过原理图或HDL描述了一个逻辑电路后,FPGA厂商提供的集成开发工具就会自动计算逻辑电路的所有可能结果,并把真值表事先写人到RAM中。这样,每输入一个信号进行逻辑运算就等于输人一个地址进行查表,找出地址对应的内容,然后输出内容即可。

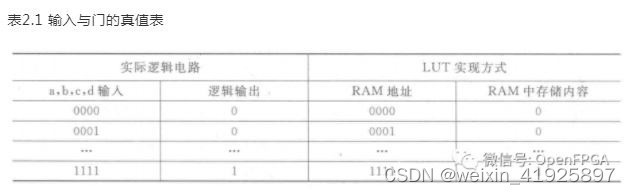

下面用一个4输人逻辑与门电路的例子来说明LUT实现组合逻辑的原理。LUT描述四输入逻辑与关系如表2.1所示。

表2.1 输入与门的真值表

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

二.LUT实现原理

LUT,中文名字叫做查找表,其原理其实也就是一个一个查找表,根据输入去找到相应位置的信号,然后做输出。说白了就好像一个小容量的ROM,把输入当作地址信号,对LUT里面预存的内容进行寻址。

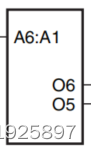

7系列的FPGA的LUT有6个输入端口(A1-6),然后有两个输出端口(O5,O6)。下图是SLICEL里面的LUT。

其可以实现6输入的布尔组合逻辑函数,输入信号为A1,A2,A3,A4,A5,A6,输出端口为O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其实现方式就是将输入(A1,A2…A6)对应的输出在LUT里面预存好(这一步在我们用bit文件配置FPGA时实现),然后把输入信号当作地址信号去把对应的输出信号调出来。

同样其还可以构成两个5输入的布尔组合逻辑函数,其中这两个函数共用5个输入信号(A1,A2,A3,A4,A5),A6被拉高,O5,O6分别是两个布尔逻辑的输出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故这也相当于实现的是一个5输入2输出的逻辑函数。

[O5,O6]=f(A1,A2,A3,A4,A5)

三.总结与提升

总结一下,就好比单个LUT里面可以预存 2^6=64个结果。那么单个LUT可以实现

(1)输入信号最多为6bit,输出信号为1bit的的布尔逻辑函数;

(2)输入信号最多为5bit,输出信号为2bit的逻辑。

一个SLICE里面有四个LUT故最多可以预存的输出信号个数为 26*4=28。

因此在一个SLICE里面,借助选择器将多个LUT进行互连,可以实现输入数,输出数最多为如下所示的逻辑。

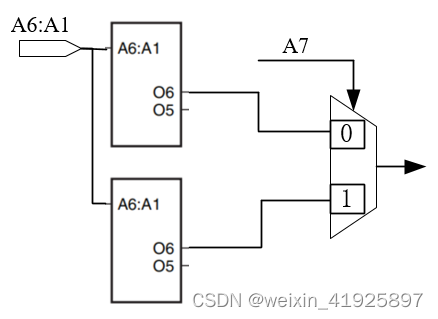

(1)2个LUT通过互连可以构成7bit输入,单bit输出的逻辑。实现方式为两个LUT的输入信号A1,A2,A3,A4,A5,A6接到一起,输出信号经过选择器选择输出,选择器的选择信号也是逻辑函数的一个输入信号。

(2)4个LUT通过互连可以构成8bit输入,单bit输出的逻辑。实现方式大家可以根据上面的实现方式自行推理。

(3)2个LUT通过互连可以构成6bit输入,2bit输出的逻辑。实现方式自行推理。

(4)4个LUT通过互连可以构成7bit输入,2bit输出的逻辑。实现方式自行推理。

超过8输入的布尔逻辑就需要多个SLICE来实现。

从表2.1可以看到,LUT具有和逻辑电路相同的功能,但是LUT具有更快的执行速度和更大的规模。与传统化简真值表构造组合逻辑的方法相比,LUT具有明显的优势,主要表现在:

(1)LUT实现组合逻辑的功能由输入决定,而不是由复杂度决定。

(2)LUT实现组合逻辑有固定的传输延迟。

1.2 输入查找表新结构

在65nm工艺条件下,与其他电路(特别是互连电路)相比,LUT的常规结构大大缩小。一个具有4倍比特位的6输入LUT结构仅仅将所占用的CLB面积增加了15%,但是平均而言,每个LUT上可集成的逻辑数量却提高了40%。当采用更高的逻辑密度时,通常可以降低级联LUT的数目,并且改进关键路径延迟性能。

新一代的FPGA提供了真正的6输入LUT可以将它用作逻辑或者分布式存储器,这时,LUT是一个64位的分布式RAM(甚至双端口或者四端口)或者一个32位可编程移位寄存器。每个LUT具有两个输出,从而实现了五个变量的两个逻辑函数,存储32X2 RAM比特,或者作为6输入16X2比特的移位寄存器进行工作。公众号:OpenFPGA

LUT逻辑结构在每个LUT中融合了更多的逻辑块,使用了较少的局部互连节点或更少的高电容节点(逻辑功能之间),降低了逻辑层次,从而缩短了路径延迟。这种新的对称布线还使相邻逻辑之间的连接更加直接,进一步降低了布线电容。

下面通过采用4和6输入LUT实现多路选择器(MUX)的例子来说明6输入查找表的优势。如图2.16(a)所示,在4输入LUT的结构中实现一个8:1的MUX需要四个4输入LUT和三个MUXF模块;如图2.16(b)所示,在6输入LUT的架构中实现同样的8:1的MUX只需要两个LUT和一个MUX模块。因此,采用6输入LUT结构时,所构造的逻辑 结构性能更高且利用率更好。

58.JPG

1.3可配置的逻辑块

可配置的逻辑块(Configurable Logic Block,CLB)是FPGA内主要的逻辑资源,用于实现时序和组合逻辑电路。7系列的CLB提供了高性能的FPGA逻辑:

真正的6输人查找表:

双LUT5(5输人LUT))选项;

可作为分布式存储器和移位寄存器;

用于算术功能的快速进位逻辑;

宽的多路复用器。

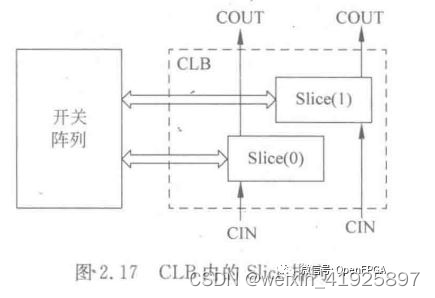

每个CLB连接到一个开关矩阵用于访问通用的布线资源,如图2.17所示。一个CLB包含两个切片(Slice)每个切片中,包含4个6输入的查找表、8个触发器、多路复用器和算术进位逻辑。

57.JPG

注:这两个切片没有直接的相互连接,每个切片以列的形式排列在一起。

在7系列的FPGA中,大约2/3的Slice是SLICEL逻辑(L表示Logic),剩下的是SLICEM逻辑(M表示Memory)对于SLICEM来说,除了实现SLICEL内的逻辑功能外,它也能通过使用它内部的LUT构造出分布式的64位RAM或者32位的移位寄存器(SRL32)或者2个SRL16。

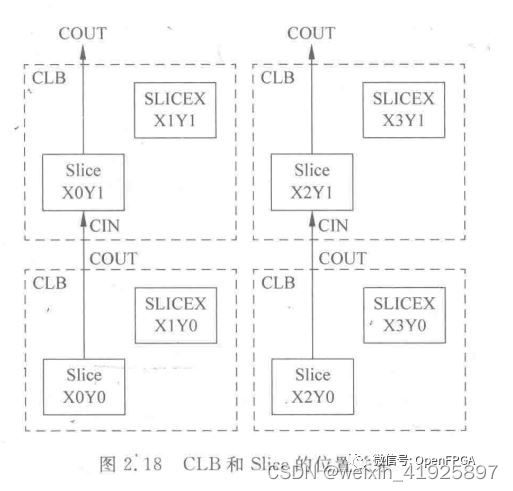

每个CLB由两个Slice构成,如图2.18所示。对于每个CLB来说:

(1)SLICE(0)在CLB的底部和左边一列。

(2)SLICE(1)在CLB的顶部和右边一列。

56.JPG

注:X后面的数字用于标识CLB内每个切片的位置,以及切片所在列的位置。

(1)X编号:切片位置从底部以顺序0,1开始计算(第1列CLB),2、3(第2列CLB)等。公众号:OpenFPGA

(2)Y编号:标识切片所在行的位置。在同一个CLB内Y后面的值是一样的。计算从底部的CLB开始,从一行CLB递增到下一行CLB。

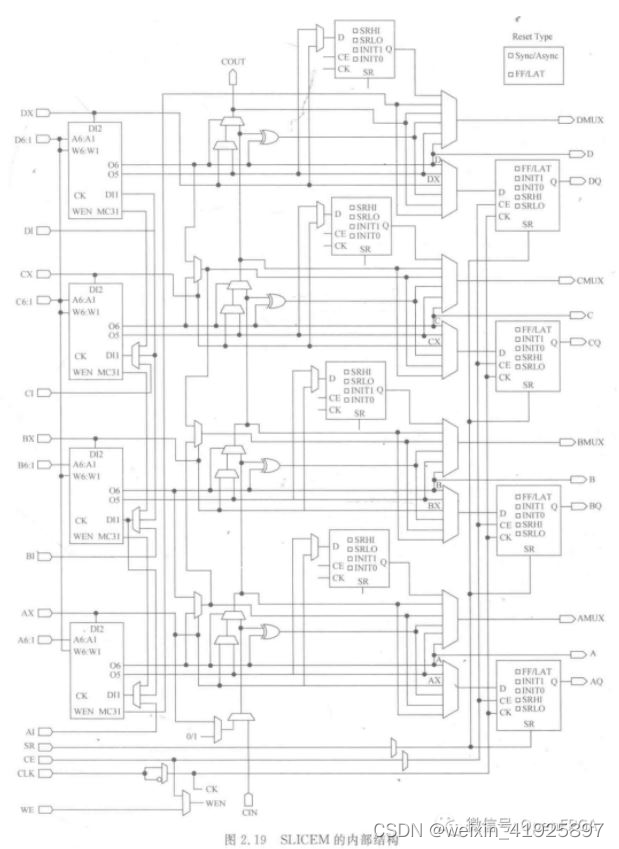

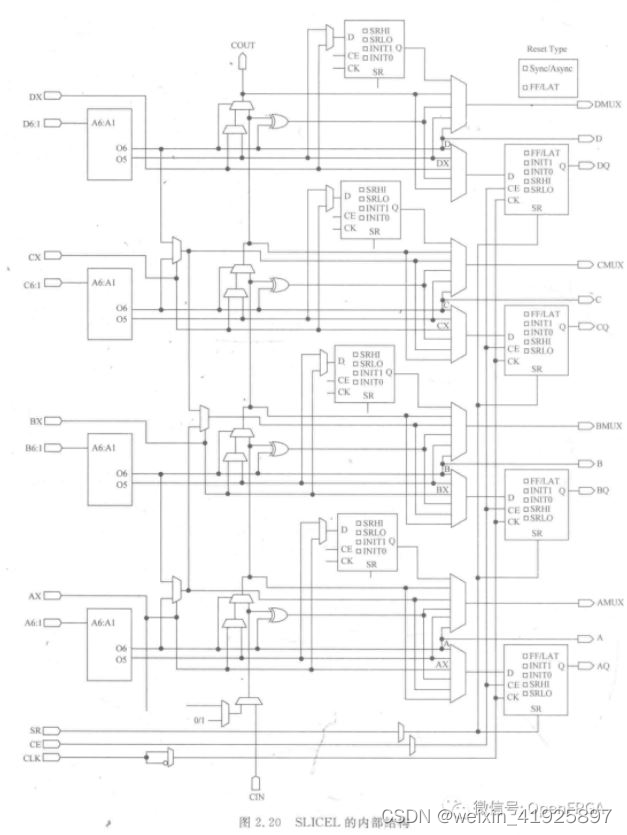

SLICEM的内部结构和SLICEL的内部结构分别如图2.19和图2.20所示。

55.JPG

54.JPG

1.3时钟资源

7系列的FPGA提供了6种不同类型的时钟线,包括BUFG、BUFR、BUFIO、BUFH、BUFMR和高性能的时钟,以此来解决不同的时钟要求,这些要求包括高扇出、短传递延迟和特别低抖动。组和全局时钟的描述如图2.21所示。

53.JPG

1.全局时钟

7系列FPGA提供了最高扇岀的32个全局时钟线,它能到达每个触发器时钟,时钟使能和置位/复位。通过水平时钟缓冲区BUFH驱动在任何时钟域的12个全局时钟线。每个BUFH可以独立地使能/禁止,并且允许关闭一个区域的时钟,因此提供了细粒度控制时钟域功耗的能力。全局时钟缓冲区也能驱动全局时钟线,可以实现无毛刺的时钟复用和时钟使能功能。全局时钟常常由CMT驱动,能完全消除基本时钟分布延迟。

2.区域时钟

区域时钟能驱动其区域内的所有时钟目的。一个区域定义为一个包含50个I/O以及 50个CLB高度和跨越半个芯片宽度的区域 域内,提供4个时钟跟踪。通过4个时钟使能(Clock-capable Clock,CCIO)输入引脚的其中一个引脚,可以驱动每个区域时钟缓冲区。在7系列FPGA中,有两种类型的CCIO:两个多区域(MulTI-region Clock-capable,MRCC)和两个单区域CCIO(Single-region Clock capable CLOCK,SRCC)。

CCIO的输入为差分/单端模式,它用来驱动4个I/O时钟BUFIO、4个区域时钟BUFR以及本区域中任何一个CMT。

7系列FPGA引入了多时钟区域缓冲区BUFMR提供了跨越区域/组的能力。

3.I/O时钟

I/O时钟频率很高,它只用于I/O逻辑和串行/解串行电路。在7系列FPGA中,提供了从MMCM到I/O的直接连接,它为低扭曲和高性能接口提供时钟。

1.4时钟管理模块

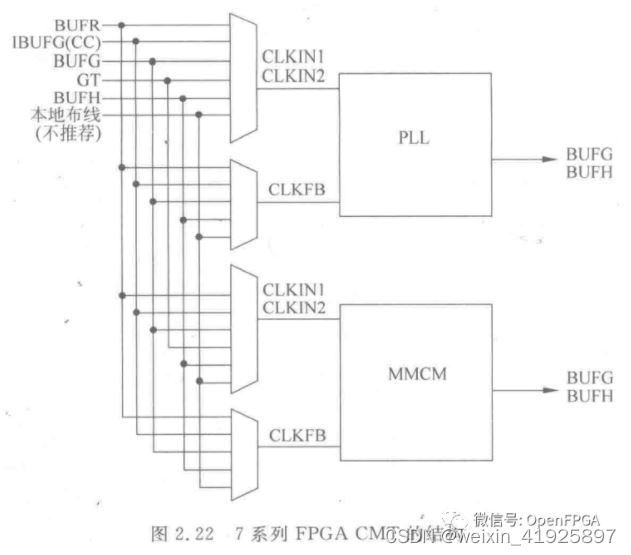

7系列FPGA内的每个时钟管理模块(Clock Management TIle,CMT)包含一个混合模式的时钟管理器(Mixed-mode Clock Manager,MMCM)和一个相位锁相环(Phase Locked Loop,PLL)。PLL包含了MMCM功能的部分。

7系列FPGA内CMT的结构,如图2.22所示,图中给出各种时钟源和MMCM/PLL的连接,输人多路复用器从IBUFG、BUFG、BUFR、BUFH、GT或者本地互联中,选择参考源和反馈时钟。

52.JPG

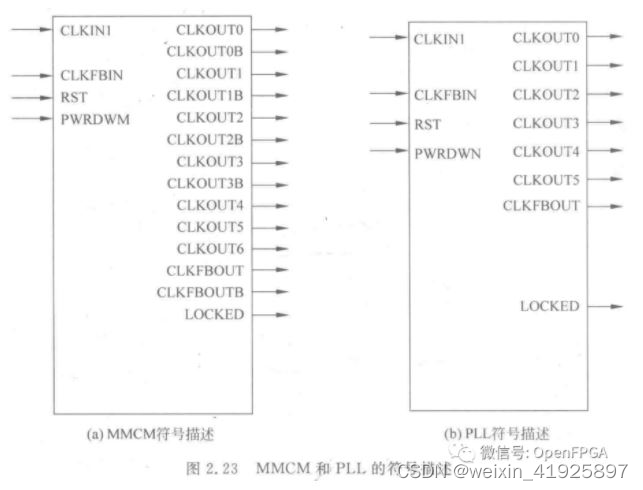

7系列的FPGA提供最多24个CMT。MMCM和Pll用于频率合成器,用于宽范围的频率。MMCM和PLL的符号描述如图2.23所示。

51.JPG

在7系列FPGA内,PLL是MMCM功能的一部分。MMCM支持的额外特性包括:

使用CLKOUT[0…3]实现到BUFR或者BUFIO的直接高性能路径连接;

反相的时钟输出CLKOUT[0…3];

CLK0UT6;

CLK0UT4_CASCADE;

为CLKOUTO_DIVIDE_F行小数分频;

为CLKFBOUT_MULT_F行小数倍频;

细微的相位移动;

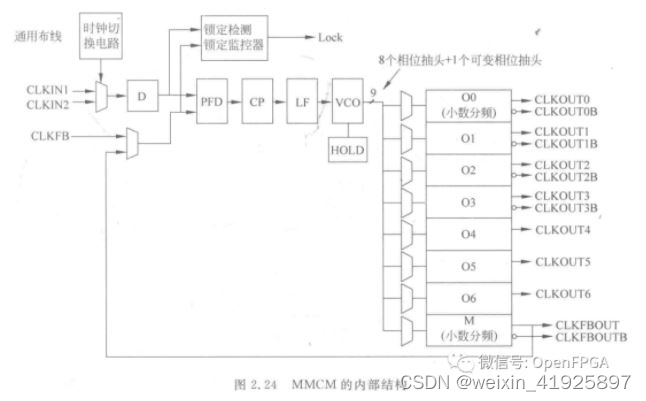

动态的相位移动。MMCM的内部结构,如图2.24所示。MMCM的相位-频率检测器PFD用于比较输入时钟和反馈时钟的上升沿频率和相位。在两个时钟之间,PFD产生与相位和频率成比例的信号,该信号驱动充电泵CP和环路滤波器LF,用于为压控振荡器VCO产生一个参考电压。

50.JPG

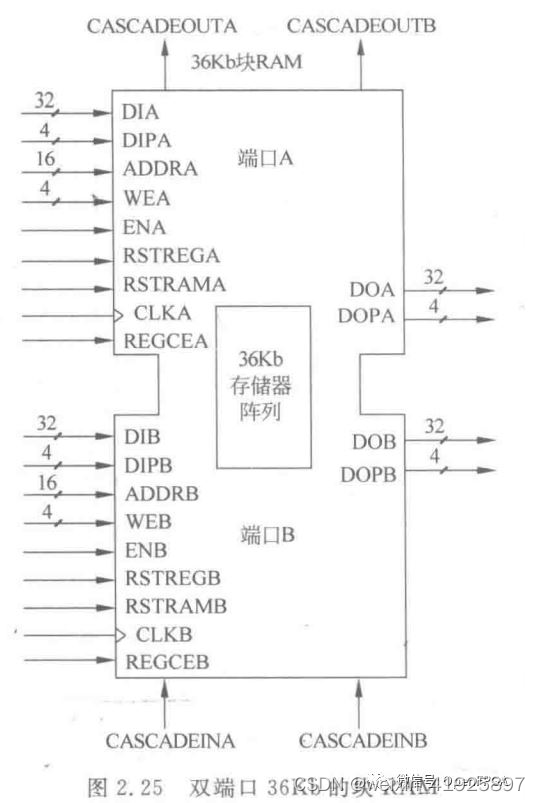

1.5块存储器资源

大多数FPGA都具有内嵌的块RAM,这极大拓展了FPGA的应用范围和灵活性。BRAM用于高效的数据存储或者缓冲,可用于高性能的状态机、FIFO缓冲区、大的移位寄存器、大的LUT或者ROM块。RAM的结构如图2.25所示。

49.JPG

7系列的FPGA提供了20〜1880个双端口的块存储器,每个BRAM的容量为36KB,在7系列FPGA内,BRAM的关键特性包括:

双端口存储器的数据宽度最多为72位;

可编程的FIFO逻辑;

内建可选的纠错电路。

FPGA内的每个BRAM提供了两个可访问的端口,但是它也能配置为单端口RAM。

每个存储器的读/写访问由时钟控制。所有的输入数据、地址、时钟使能和写使能都经过寄存。输人地址总是由时钟驱动,一直保持数据,直到下一个操作。可选的输出数据流水线寄存器,允许以一个额外时钟的代价,产生更高的时钟速率。

1.BRAM的配置

每个端口可以配置成32KX1、16KX2、8KX4、4KX9、2KX18、1KX36或者512X72。

两个相邻的BRAM能级联构成一个64KX1的双端口存储器,且不需要添加任何逻辑。

注:上面的容量以比特计算。

2.检错和纠错

每个64位宽的BRAM可以产生、保存和使用8位额外的海明码。在读过程中,可以纠正单比特错误以及检测两比特错误。在读写外部64〜72位宽的存储器时,也可以使用ECC逻辑。

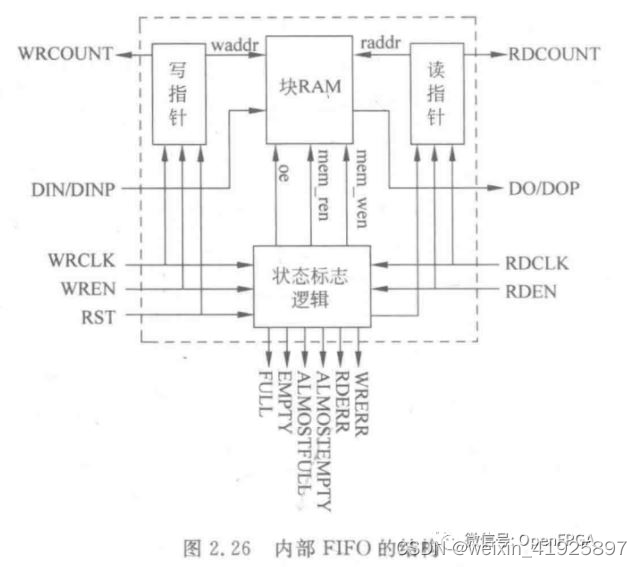

3.UFO控制器

7系列FPGA提供了FIFO结构,内部结构如图2.26所示。

48.JPG

该结构便用单时钟(同步)或双时钟(异步)操作,递增内部的地址,并且提供了4个握手信号线:full(满)、empty(空)、almostfull(几乎满)和almostempty(几乎空)。

注:1、可自由编程几乎满和几乎空标志;2、FIFO的宽度和深度也可以编程,但是读和写端口总是相同的宽度;3、图2.26中的读写指针专用于FIFO。

在首字跌落(First Word Fall-through)模式中,在第一个读操作前,第一个写人的字自动出现在数据输出端。当读取第一个字后,这个模式就和标准模式一样了。

1.6互联资源

互联是FPGA内用于在功能元件,例如IOB、CLB、DSP和BRAM的输人和输出信号提供通路的可编程网络。互联也称为布线以规则的阵列排列,被分段用于最优的连接。

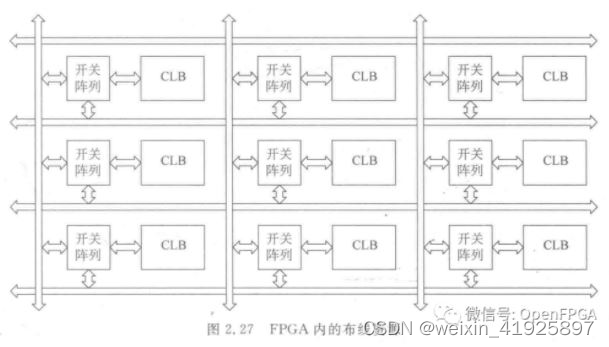

在7系列FPGA中,CLB以规则的阵列排列。每个岛开关矩阵的连接用来访问通用的布线资源,如图2.27所示。

47.JPG

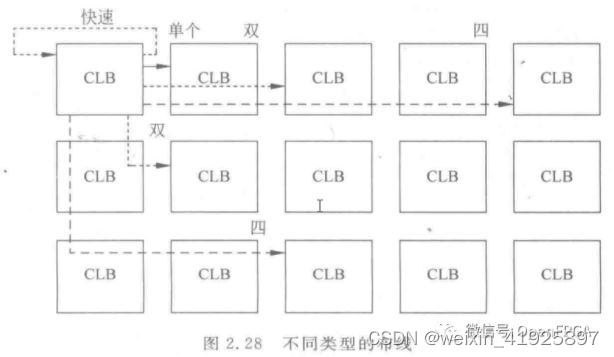

在7系列FPGA中,提供不同类型的布线,如图2.28所示。这些布线通过长度来定义。互联类型有:快速连接、单连接、双连接和四连接。

46.JPG

(1)快速连接:将模块的输出连接到自己模块的输人。

(2)单连接:在垂直和水平方向上,布线连接到相邻的单元。

(3)双连接:在所有四个方向上,水平和垂直连接到所有其他的单元和对角线相邻的单元。

(4)四连接:在水平和垂直方向上,每隔4个CLB连接一个单元或者以对角线方式连接到相隔两行和两列距离的单元。

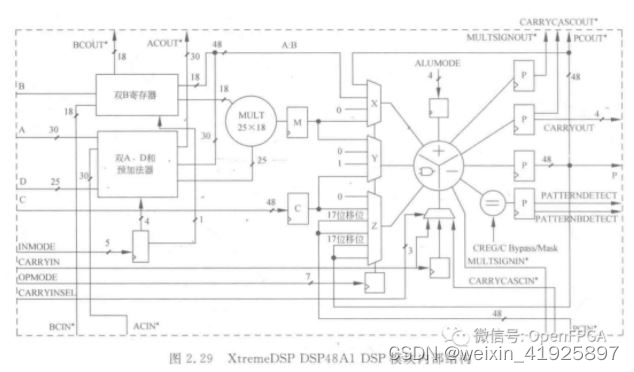

1.7专用的DSP模块

在7系列的FPGA中,集成了专用的、充分定制的低功耗的XtremeDSP DSP48E1 DSP模块,其内部结构如图29所示。其增强的特性主要表现在:

(1)25X18位的补码乘法器/累加器,高分辨率48位信号处理器,其工作频率最高可以达到638MHz;

(2)低功耗的预加法器可用于构建滤波器,它降低了所需的50% DSP Slice资源;

(3)高级的特性包括可选的流水线、可选的ALU以及用于级联的专用总线。

45.JPG

在数字信号处理应用中,会使用大量的二进制乘法器和累加器,因此推荐在专用的DSP Slice中实现数字信号处理算法。在DSP Slice中,设计者可以动态选择旁路掉乘法器。

此外,两个48位的数据可以输人到一个单指令多数据流SIMD算术单元(它可以实现双24位加/减/累加,或者4个12位加/减/累加)操作,或者一个逻辑单元(它可以实现10种不同的逻辑功能运算)。

在DSP Slice中还提供一个48位的模式检测器,用于收敛或者对称的四舍五人操作。当它与逻辑单元一起使用时,模式检测器也可以实现96位宽度的逻辑功能。

DSP Slice所提供的流水线以及扩展功能,显著提高了数字信号处理算法的处理速度和处理效率。

1.8 输入和输出块

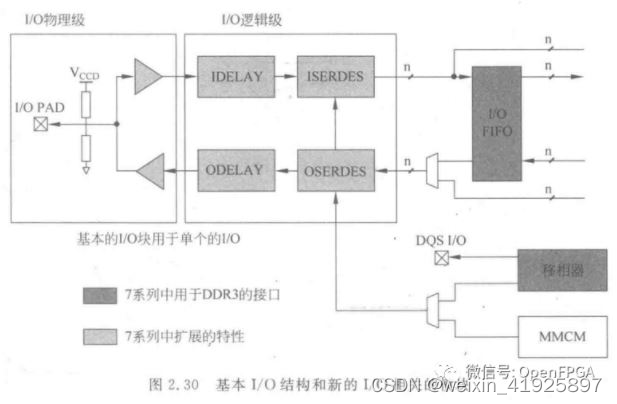

7系列FPGA对输入和输出进行了优化,这样可以在物理级和逻辑级上满足不同的要求,这些要求包括高速存储器、网络、视频平板和传感器接口,高速的ADC/DAC连接,以及传统接口。7系列的FPGA使用了统一的I/O架构。

物理I/O能力和结构提供了一个I/O标准范围、端接和低功耗模式。每个I/O组的I/O数量,它们相对时钟和新I/O资源放置的位置以及I/O在FPGA晶圆上的排列顺序同等重要。此外,I/O绑定逻辑功能,例如输入/输岀延迟和串行化/解串行化功能,它对于支持高带宽应用也非常关键。在I/O上所增加的新功能,如移相器、PLL和I/O FIFO完整接口特性,可用于支持最高性能的DDR3以及其他存储器接口。基本I/O结构和新I/O相关的模 块,如图2.30所示。

44.JPG

1.I/O物理级

在物理级上,I/O要求支持一个给定范围的驱动电压和驱动强度,以及功能接口可接受的不同I/O标准。此外,I/O也支持不同的输入/输出端接特性。在7系列的FPGA中,支持两种不同类型的I/O。

(1)高性能(High Performance,HP)I/O。在I/O组中,将它们称为HP I/O组。

(2)宽范围(High Range,HR)I/O。在I/O组中,将它们称为HR I/O组,它支持宽范围的I/O标准。

在7系列FPGA中,这两种I/O类型被分别绑定到一个包含50 I/O的整个I/O组内。

(1)在ArTIx-7系列的FPGA中,只有3.3V的HR I/O组。

(2)在Virtx-7和Kintex-7系列的FPGA中,既有HP I/O组,也有HR I/O组。

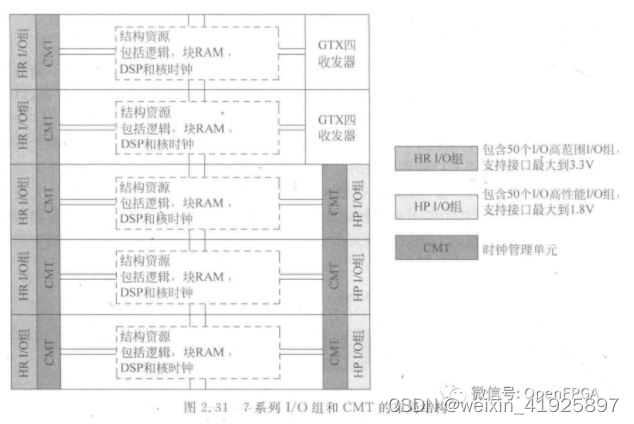

下面详细介绍HP I/O和HR I/O组。Kintex-7 XC7K160T的I/O组和CMT的布局结构如图2.31所示。

43.JPG

用于存储器接口的I/O电源主要有三个元件:

(1)DCI用于匹配PCB布线的阻抗。

(2)参考输入接收器,用于将I/O电压调整到核电压。

(3)IDELAY用于将信号同步到时钟。

2.I/O逻辑级

在7系列FPGA中,所有I/O都能被配置成组合或者寄存方式。所有的输入/输出支持双数据率(Double Data Rate, DDR),通过对IDEALY和ODELAY编程,可以对任何一个输入和某些输出进行延迟。

每个I/O块包含一个可编程的绝对延迟原语IDELAY2。IDELAY可以连接到ILOGICE2/ISERDESE2或者ILOGICE3/ISERDESE2模块。每个HP I/O组包含一个可编程绝对延迟原语称为ODELAY2。

注:

(1)原语(primiTIve)是指FPGA内部的基本功能模块。

(2)对于HR I/O组来说,不提供ODELAY2原语。

此外,对于很多应用而言需要。连接外部高速设备。在这些应用中,往往外部提供高速的串行比特流,然后转换成FPGA内并行低速的宽字节操作。因此,要求在I/O结构内提供一个串行化器和解串行化器。在7系列FPGA的每个I/O引脚中,提供了8位IOSERDES原语,它可以实现串行-并行或并行-串行之间的转换。

注:

7系列内用于精确实现ISERDES的原语是ISERDESE2,精确实现OSERDES的是OSERDESE2。

1.9 吉比特收发器

在7系列FPGA内,提供吉比特收发器,其重要特性包括:

(1)高性能的收发器,其速率最高可以达到6.6Gb/s(GTP)、12.5Gb/s(GTX)、13.1Gb/s(GTH)和28.05Gb/s(GTZ)。

(2)优化的低功耗模式,用于芯片到芯片的接口。

(3)高级的预发送和后加重、接收器线性CTLE以及判决反馈均衡(Decision Feedback Equalization,DFE),包括用于额外余量的自适应均衡。

目前,与光纤和PCB内IC直接、背板、长距离的超高速串行数据发送,变得日益流行,因此,要求专业的专用片上电路和差分I/O能应对这些高数据率的信号完整性问题。

注:Artix-7和Kintex-7系列内提供了0?32个收发器电路。Virtex-7系列提供最多96个收发器。

每个串行收发器是发送器和接收器的组合。不同7系列的串行收发器使用了环形振荡器以及LC谐振的组合。每个收发器有大量用户定义的特性和参数,它们可以在配置设备的时候进行定义,某些参数和特性甚至可以在操作的时候进行修改。

发送器是一个并行-串行的转换器,转换率为16、20、32、40、64或80。此外,GTZ发送器支持最多160位的数据宽度。这些发送器的输出使用差分输岀信号驱动PC板。通过一个可选的FIFO以及额外的硬件,输人数据支持8B/10B、64B/66B和64B/67B编码策略。

接收器是一个串行-并行的转换器,它将接收到的位串行差分信号变成并行的字流,其宽度为16、20、32、40、64或80位。此外,GTZ接收器支持最多160位的数据宽度。接收器将接收的差分数据流送到FPGA内可编程的线性和判决反馈均衡器,使用参考时钟来初始化时钟识别。数据模式使用NRZ编码。

1.11 XADC模块

在“数字化革命”时代,模拟技术的需求依然强劲。严格定义来说,常用于测量真实世界信息的大多数传感器都是模拟电路。电压、电流、温度、压力、流量和重力等均属于连续的时域信号。由于数字技术具有高度的精确性和可重复性,它常用于监控和控制这些模拟信号。数据转换器(包含ADC DAC和模拟多路复用器),为数字世界和模拟世界架起了至关重要的桥梁。

随着模拟传感器市场和数字控制系统市场的不断发展,对连接模拟世界和数字世界的需求持续增长。推动模拟混合信号技术市场发展的因素包括智能电网技术、触摸屏、工业控制安全系统、高可用性系统、先进马达控制器,以及对各种设备更高安全性的需求。

2005年,随着Virtex-5系列FPGA的推出,Xilinx意识到有必要集成名字为System Monitor的子系统以支持模拟混合信号功能。通过System Monitor子系统,设计人员可实现对FPGA关键性指标和外部环境的监控。

在经历两代FPGA产品之后,Xilinx进一步强化了这方面的工作,推出了具备模拟混合信号功能的Artix-7、Kintex-7和Virtex-7 FPGA以及Zynq-7000 SoC通过在7系列FPGA内集成两个独立通用1MHz釆样率的12位分辨率ADC。显著增强了嵌入式模拟子系统的功能。该功能强大的模拟子系统与高度灵活、功能强劲的FPGA逻辑紧密结合,实现了高度可编程混合信号平台—灵活混合信号解决方案。

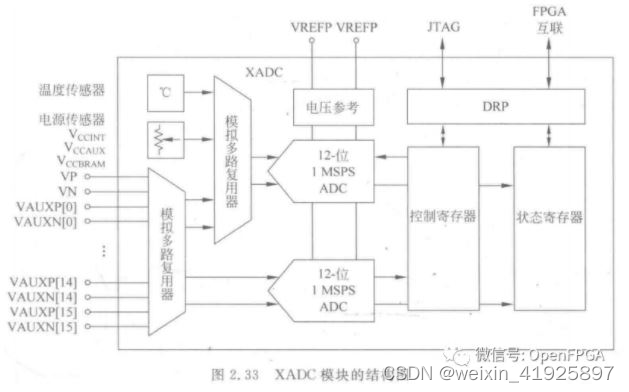

需要注意是,Xilinx的FPGA也在向混合信号处理方向发展。与Xilinx前几代FPGA系列产品相比,采用28nm工艺的7系列FPGA扩展了模拟子系统的功能。在7系列FPGA中,将模拟子系统命名为XADC。在XADC中,包含两路独立的12位1MHz采样率模数转换器(ADC)以及一个17通道模拟多路复用器。这种将模拟系统与可编程逻辑结合的全新技术被XIlinx称为灵活混合信号处理(AMS)技术。

7系列XADC模块的内部结构,如图2.33所示。该ADC(XADC)子系统包括:

42.JPG

(1)17个支持单极性和双极性模拟输入信号的差分模拟输入通道。

(2)可选择片上或者外部参考电源。

(3)提供片上电压和温度传感器。

(4)采样序列控制器。

(5)片上传感器的可配置阈值逻辑及相关告警功能。

其中,控制和状态寄存器为数字可编程逻辑提供了无缝接口。

XADC提供两种类型的接口:JTAG接口和XADC FPGA接口。

XADC的一项独特功能就是能够通过JTAG端口直接访问,因此无需占用FPGA资源源。也不必配置FPGA JTAG访问同时支持数据和控制,可以让JTAG提供另一级功能和系统健康状况监控。负责控制JTAG总线的中央处理器能够采集远程的功率、温度和其他模拟数据,然后执行系统范围内的系统监控。对高可靠性系统,灵活混合信号提供了一种监控系统、控制冗余硬件和报告需求的低成本途径。Vivado提供的分析器为访问片上传感器 的信息以及通过JTAG配置XADC.提供了便利的访问途径。

check syntax(检查语法)

ISE主要包括以下环节:综合 (Synthesize - XST)-> 实现(Implement Design) (翻译(Translate),映射(Map),布局布线(Place & Route))-> 生成比特流(Generate Programming File)

语法正确的代码不一定会产生一个合理的电路(组合逻辑+触发器)。通常的原因是:我们需要考虑在我们指定的情况之外发生了什么?Verilog的回答是:保持输出不变。

保持输出不变这个行为意味着当前状态需要被记住,因此就产生了一个锁存器。组合逻辑(比如逻辑门)不能记住任何状态。注意这条信息:Warning (10240): … inferring latch(es),除非是我们有计划的产生一个锁存器,它通常意味着一个bug。组合电路必须在所有条件下都给输出信号赋一个值,这也就意味着我们必须写else从句,或者是在这个always过程块的第一句也就是case之前,就给输出信号提前赋一个默认值。case语句中同样要注意这个问题。

1、 锁存器是一种对脉冲电平(即0或者1)敏感的电路,而触发器是一种对脉冲边沿(即上升沿或者下降沿)敏感的电路。

2、锁存器对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生,这对于下一级电路是极其危险的。而触发器则不易产生毛刺。

always块内被赋值的变量(左值)都应该为reg类型。

verilog中的数据表示方法。

8’b1000_1000; //2进制表示

4’o10; //8进制表示

4’d8; //10进制表示

4’h8; //十六进制表示

模块内部定义计算过程中用到的寄存器变量作为临时变量。

module calculate( input clk,

input rst_n,

output reg[3:0] result

)

reg [3:0] add; //临时变量

endmodule