热门标签

热门文章

- 1基于51单片机停车RFID一停车扣费充值语音播报系统_基于单片机的自动rfid收费

- 2后端框架-maven-springmvc_xssfcell 不能写入字符串,maven用哪一个

- 3日更2023年6月6日-日签659

- 4文心智能体平台介绍和应用:制作你的智能体(运维小帮手)_如何关闭百度首页的智能体推荐

- 5深入理解Transformer架构的编码器-解码器结构_解码器 自注意力

- 6前端性能提升之 - electorn 结合 vue3 使用webworker 调用go打包的wasm_go打包vue

- 7python OpenCV 图像像素访问 (三)_img.ndim

- 8Redis设计与实现——数据结构(一)_毕设使用redis数据库表结构怎么写

- 9a byte of python中文版_一行Python代码能做什么?

- 10常用技术开发网站记录(firefox版)

当前位置: article > 正文

Verilog综合出来的图_verilog在哪里看逻辑综合结果

作者:在线问答5 | 2024-07-04 15:01:02

赞

踩

verilog在哪里看逻辑综合结果

Verilog写代码时需要清楚自己综合出来的是组合逻辑、锁存器还是寄存器。

甚至,有时写的代码有误,vivado不能识别出来,这时打开综合后的schematic简单查看一下是否综合出想要的结果。

比如:误将一个always模块重复一遍,vivado没有识别出来导致没有生成想要的状态机,打开综合后的schematic一看,被优化掉了。

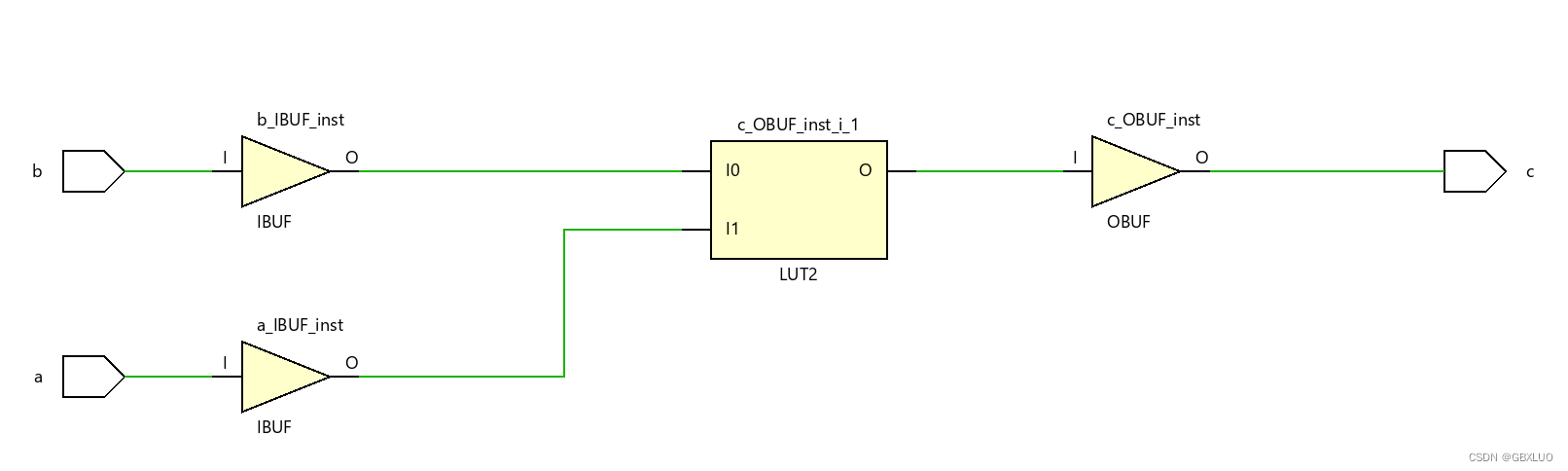

一、部分Verilog语句综合出来的原理图

1.1 综合出组合逻辑

以下四种写法综合出来的schematic一样。

1.2 综合出锁存器-Latch

锁存器容易产生glitch(毛刺),少用。

1.3 综合出寄存器

二、对应的部分原语

IBUF是引脚的输入缓冲器。

Vivado识别到输入引脚后会自动加上IBUFG模块(这里IBUFG与BUFG什么关系呢?)。

OBUF是引脚的输出缓冲器。

LDCE:异步清零的latch。

LDPE:异步置位的latch。

CLR置低位,高有效。

GE使能G控制信号。

G为高,D输入赋值给Q,电平触发。

G为低,Q保持

D Flip-Flop with Clock Enable and Synchronous Set 带时钟使能和同步置位的D触发器。

置位S为高电平时,一个时钟C的上升沿触发导致寄存器置位1;

置位S为低电平,时钟使能CE位为高电平时,一个时钟C的上升沿触发寄存器FDCE的输出端Q装载数据口的数据D 。

三、语法不报错,综合报错

3.1 wire型变量不能使用非阻塞赋值-vivado语法虽未报错,但不能综合

procedural assigment to a non-register c is not permitted

不允许对非寄存器c进行程序赋值

四、参考链接:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/在线问答5/article/detail/787312

推荐阅读

相关标签