- 1mqtt协议的简单实用实例_mqtt连接到broker代码示例

- 2数据结构------最短路弗洛伊德算法(Flody)

- 3带你读懂中国人工智能产业的商业应用现状_投资者看好人工智能行业的发展前景,资本将助力行业更好

- 4解释什么是ElasticSearch,以及它主要用于什么_elasticsearch 能用来做什么

- 5百科荣创——安卓识别(高精度)_百科荣创识别红绿灯

- 6python 地震数据可视化_marmousi model 下载

- 7pytorch深度学习基础快速入门7:完整模型训练套路_模型训练入门

- 8【数据结构】链表:带头双向循环链表的增删查改_试实现带头结点的循环双链表删除操作。

- 9双向循环链表_双向链表头尾相接吗

- 10文档处理新探究成果——前沿技术CCIG文档图像智能分析论坛分享_文字编辑行业的前沿技术

fpga学习day4 开发板到啦~使用viavdo进行管脚约束_vivado查看管脚

赞

踩

拿到开发板后,先检查一下是否可以连接成功,按照教程中的描述连接好板子(电源和JTAG),板子要上电,如下所示:

右键"此电脑"——"管理",弹出如下对话框,点击"设备管理"——"通用串行总线控制器",查看是否能够检测到我们的JTAG。

下面回到Vivado中,将仿真中用到的端口(a,b,sel和out)和板子中的端口对应起来。首先点击"RTL ANALYSIS"——"Run Elaborated Design",此时可以看到这个功能将代码转化成了电路。如果已经进行过这个操作,显示的会是"Open Elaborated Design",直接打开这个文件即可,如下图:

然后点击软件右上角,可以看到如下几个选项:

选择‘I/O Planning’,下面出现了I/O Ports的窗口,就可以开始进行管脚配置了。

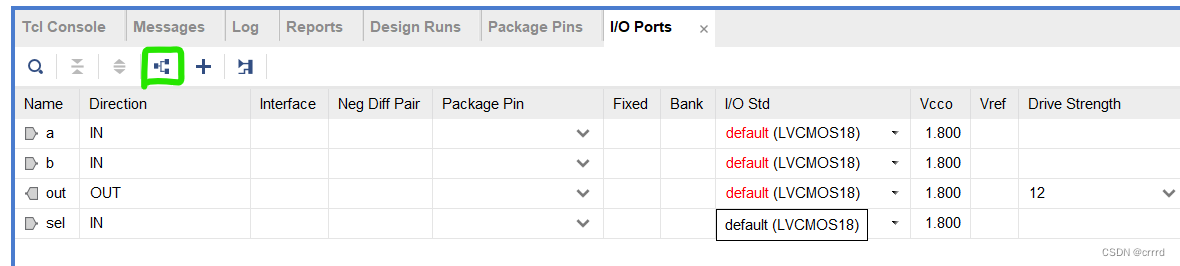

点击下图绿色圈出的按钮,就能显示需要配置管脚的输入和输出信号:

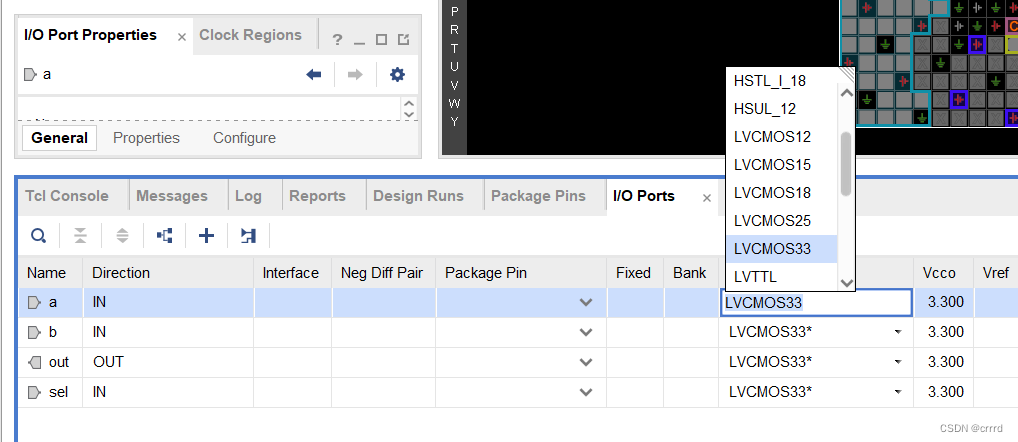

下面需要设置管脚的电平,我用的板子上所有管脚电平都是3.3V,因此做出如下修改:

这是一个二选一编码器,我选择将按键SW0作为选择信号sel的输入端,a,b分别从SW1和SW2中输入,输出out由LED0来体现。根据商家提供的资料,SW0:K14,SW1:L15,SW2:G14,LED0:G17,管脚分配结果如下:

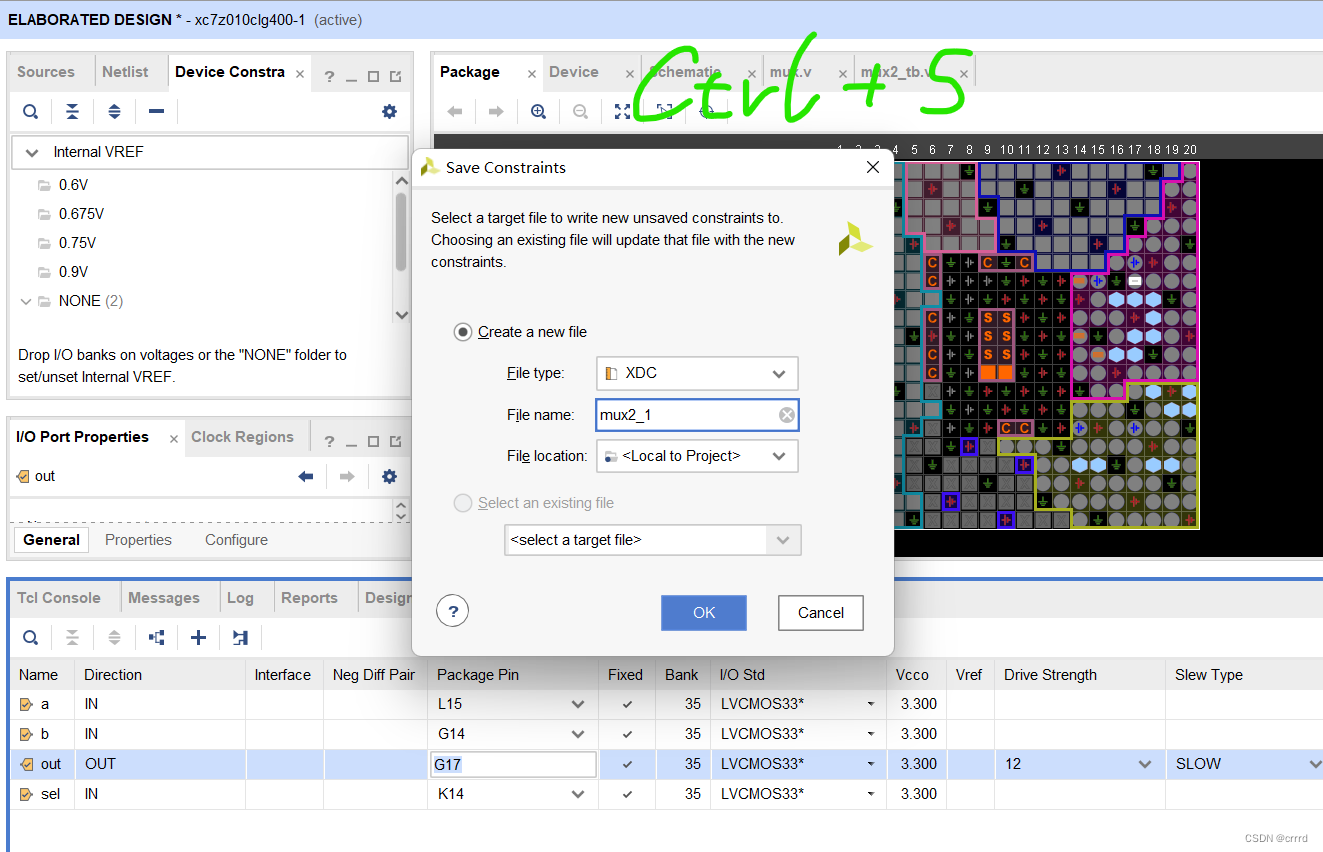

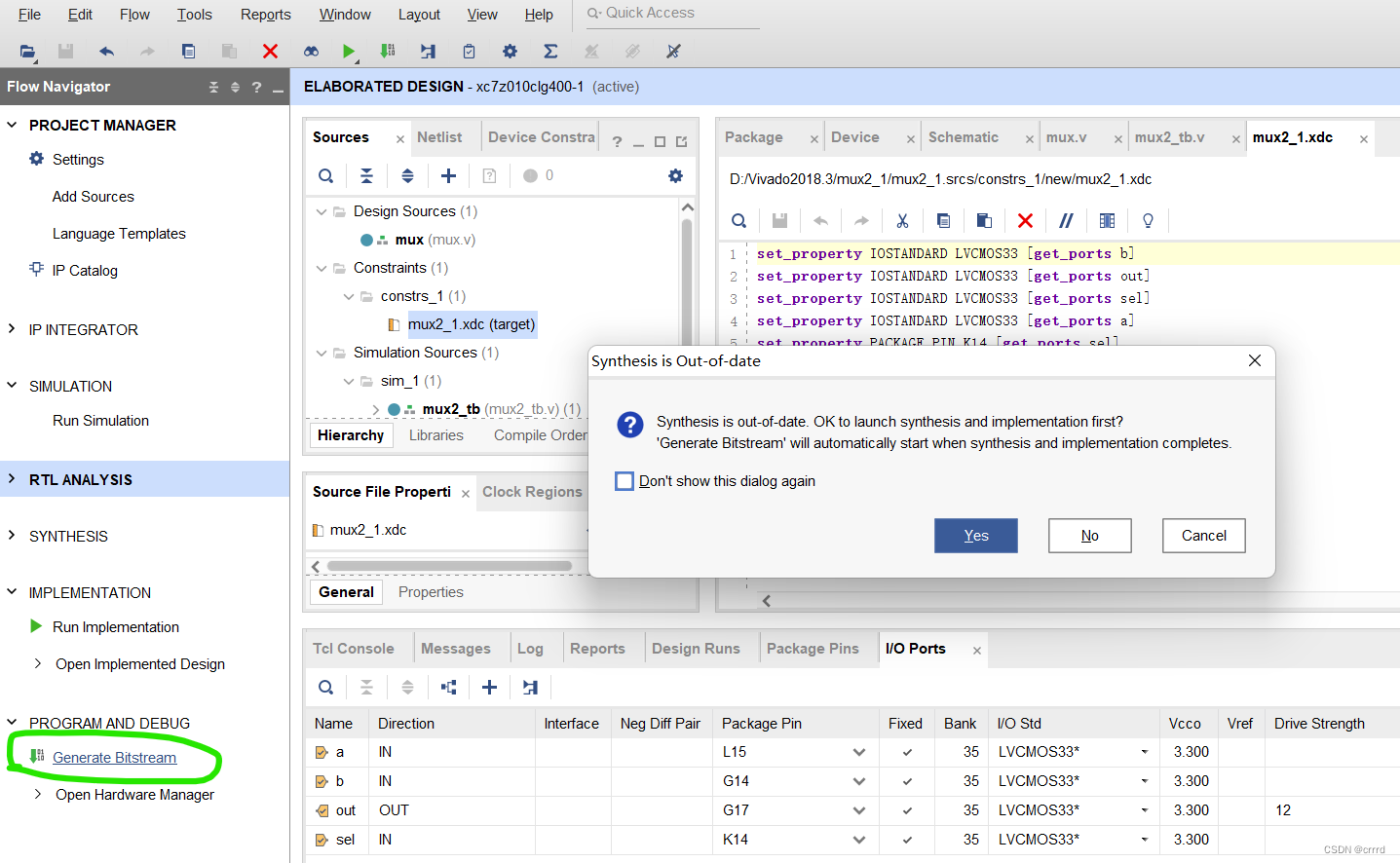

然后,crtl+s,对管脚分配结果进行保存,结果被存储在一个后缀为xdc的文件中:

这可以看到,我们的项目由三个文件组成:1.设计文件,2.仿真测试文件,3.管脚约束文件:

文件3后面会显示一个target,说明这就是在烧录中的目标文件(告诉板子管脚怎么对应),如果一个文件中存在多个xdc文件,我们需要根据实际的情况去我们需要的是哪个文件。

bit文件是FPGA的可执行文件,因此需要先将我们编写的内容转化为bit文件,点击"PROGRAM AND DEBUG"中的"Generate Bitstream",就完成了可执行文件的生成。

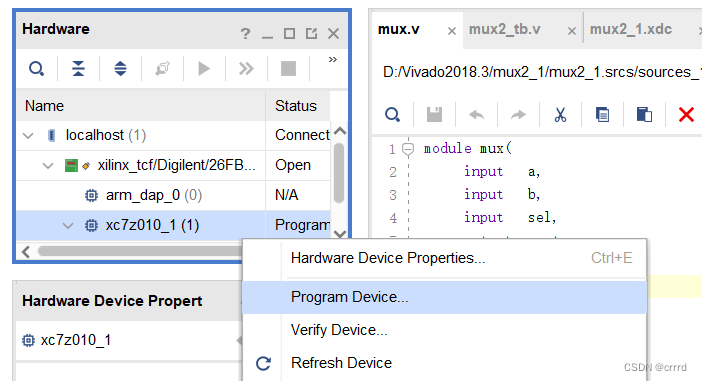

生成执行文件后,点击"Open Hardware Manager",在Hardware栏中可以看到我们使用的板子的型号。

右键,点击"Program Device",就完成了程序的烧录。完成后,点击右键"Open Hardware Manager",选择"Close",软件就自行关闭了烧录功能。下面就可以在板子上观察实验效果了。