热门标签

热门文章

- 1LoRA学习笔记_全量更新和lora

- 2k8s1.28.8版本配置Alertmanager报警方式(邮件,企业微信)

- 3python使用nltk进行中文语料库的词频分布统计_python nltk 中文

- 4学习如何使用NLTK和Spacy库进行文本分词、词性标注、命名实体识别等操作_nltk 中文pos_tag

- 5几本有价值的java提升书

- 6GPT-4 数据分析提示:图表和地图初学者指南 删除“高级”以进行简单有用的数据分析_gpt如何绘制建筑分析图

- 7python输入输出-python 输入输出 - 刘江的python教程

- 8resnet预训练模型_23个系列分类网络,10万分类预训练模型,这是飞桨PaddleClas百宝箱...

- 9一文搞懂 Transformer 工作原理 !!_transformer原理

- 10【折腾笔记】Windows系统运行ChatGLM3-6B模型实验_glm 最低配置

当前位置: article > 正文

Modelsim仿真基本流程-以半加器的设计为例_modelsim仿真测试文件

作者:小丑西瓜9 | 2024-03-28 19:35:27

赞

踩

modelsim仿真测试文件

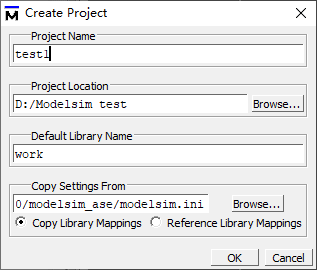

1、打开modelsim,创建新项目,选择项目保存位置,输入项目名称test1,点击OK。注意不要出现中文。

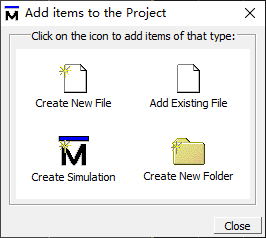

2、弹出对话框,选择新建文件

3、新建源文件,选择文件类型为Verilog,输入文件名half_add,OK。

4、新建测试文件test_bench,以顶层文件名后加_tb命名。

5、双击half_add.v,编辑源文件。

6、双击half_add_tb.v,编辑测试文件。initial中的代码用于初始化信号,只执行一遍,always中的代码则循环执行,用于产生半周期为T的信号b。

7、编译所有文件,并查看错误信息。

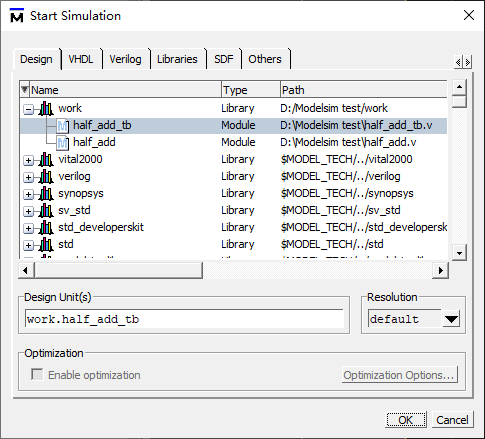

8、点击Simulation,start simulation,启动仿真,选择测试文件half_add_tb,OK。

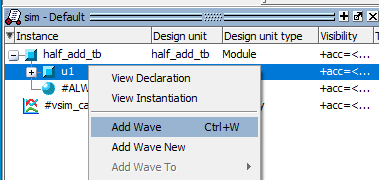

9、右击添加要查看波形的信号。

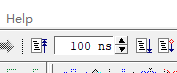

10、设置仿真时间,默认100ns

11、点击运行按钮

![]()

,查看100ns波形,也可多次点击该按钮,查看更长时间的波形,按照_tb代码对照波形。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小丑西瓜9/article/detail/330905

推荐阅读

相关标签