热门标签

热门文章

- 1关于树形结构建立过程中动态申请的节点空间_树的节点如何开辟空间

- 2全新版大学英语综合教程第四册学习笔记(原文及全文翻译)——3B - A Mortal Flower(尘世的花)_尘世的花韩素音

- 3图像检索(Image Retrieval)入门_图像检索 神经网络

- 4Quartus-II 9.0版本实现半加器,1位全加器,4位加法器的设计(数字逻辑课程实验1—半加器设计,1位全加器设计,4位加法其设计)_半加器quartus

- 5升级uniapp后小程序编译提示[ project.config.json 文件内容错误] project.config.json: libVersion 字段需为string

- 6经典网络模型系列——Swin-Transformer详细讲解与代码实现_swin transformer模型

- 7单链表的应用实例(增删改查)_单链表例子

- 8Text-to-SQL任务:SyntaxSQLNet论文笔记_中文数据集cspider

- 9android开发笔记之高通MSM8909编译刷机脚本_高通编译脚本

- 10TCP/IP协议详解_tcpip协议

当前位置: article > 正文

vivado 在硬件中调试逻辑设计

作者:weixin_40725706 | 2024-04-19 22:49:42

赞

踩

vivado 在硬件中调试逻辑设计

在硬件中调试逻辑设计

设计中包含调试核后

,

您可使用运行时间逻辑分析器功能来对硬件中的设计进行调试。

使用

Vivado Logic Analyzer

进行设计调试

Vivado

®

Logic Analyzer

功能可用于与设计中运行的新

ILA

、

VIO

和

JTAG-to-AXI Master

调试核进行交互。要访问

Vivado Logic Analyzer

功能

,

请单击

Flow Navigator

的“编程和调试”部分中的“

Open Hardware Manager

”按钮。

使用

ILA

调试核对硬件中的设计进行调试的步骤如下

:

1.

连接到硬件目标并使用

.pdi

文件对

FPGA

或

ACAP

进行编程。

2.

设置

ILA

调试核触发和采集控制。

3.

装备

ILA

调试核触发器。

4.

在“波形

(Waveform)

”窗口中查看从

ILA

调试核采集的数据。

5.

使用

VIO

调试核来驱动控制信号和

/

或查看设计状态信号。

6.

使用

JTAG-to-AXI Master

调试核来运行传输事务

,

以便与设计中的各种

AXI

从核进行交互。

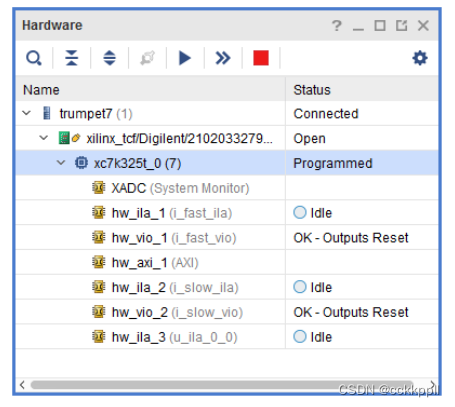

连接至硬件目标并执行器件编程

在调试前对

FPGA

或

ACAP

执行编程的步骤与“对

FPGA

或

ACAP

进行编程”中所述步骤完全相同。使用

.pdi

文件

(

包含新的

ILA

、

VIO

和

JTAG-to-AXI Master

调试核

)

对器件进行编程后

,

“

Hardware

”窗口就会显示在扫描器件时

检测到的调试核

,

并显示

RTL

实例名称

(

以括号括起

)

。

如需了解有关使用

ILA

核的更多信息

,

请参阅“设置

ILA

核以执行测量”。如需了解有关使用

VIO

核的更多信息

,

请

参阅“设置

VIO

核以执行测量”。

重要提示

!

请确保

JTAG

时钟比调试核的时钟输入更慢。您可使用“打开新硬件目标

(Open New Hardware

Target)

”

Wizard

或者使用以下

Tcl

命令来修改

JTAG

频率

:

set_property PARAM.FREQUENCY 250000

[get_hw_targets */xilinx_tcf/Digilent/210203327962A]

Vivado

硬件管理器仪表板

Vivado

硬件管理器仪表板可帮助您管理系统监控器

(System Monitor)

、

ILA

和

VIO

调试核的各个窗口。这些仪表板支

持您在自己的

Vivado Design Suite

工程中创建、修改和保存这些窗口的配置。

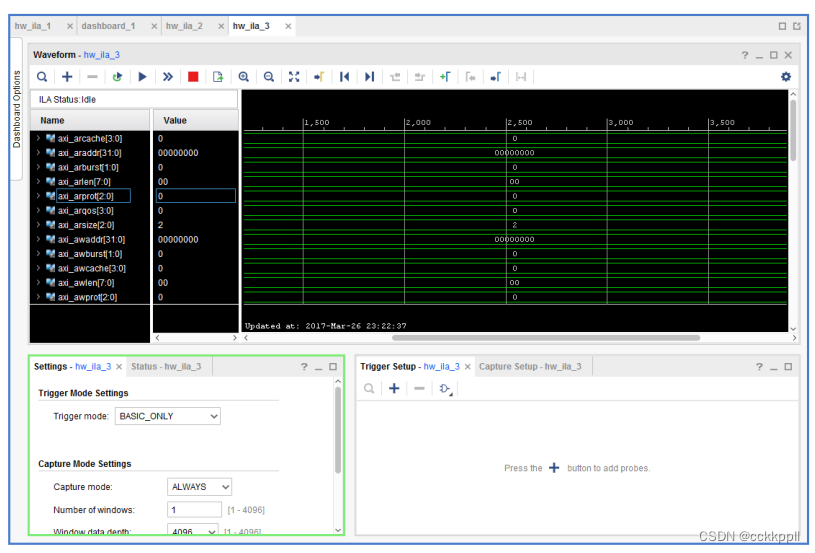

默认仪表板

刷新硬件器件时如果检测到调试核

,

则将自动打开每个调试核的默认仪表板。

默认仪表板窗口

每个默认仪表板都包含与创建的仪表板所对应的调试核相关的窗口。为

ILA

调试核所创建的默认仪表板包含

5

个窗

口。

• “

Settings

”窗口

• “

Status

”窗口

• “

Trigger Setup

”窗口

• “

Capture Setup

”窗口

• “

Waveform

”窗口

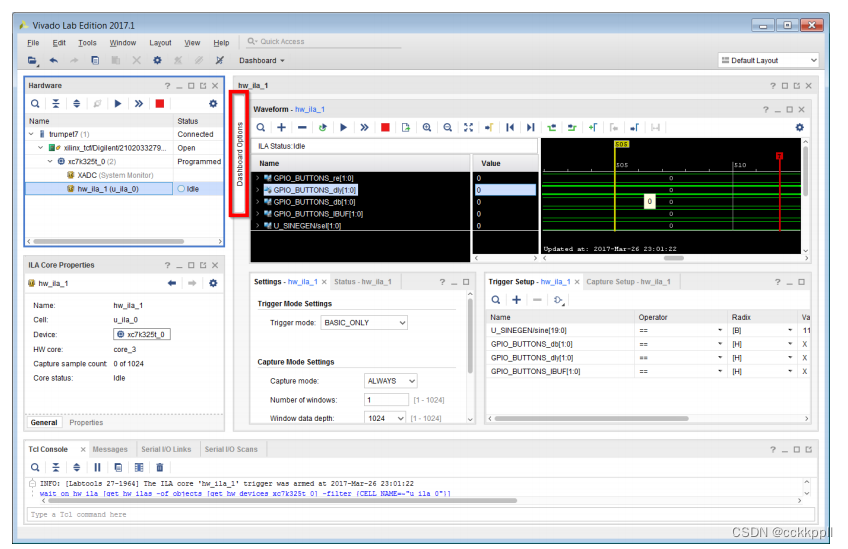

以下显示了默认

ILA

仪表板示例。

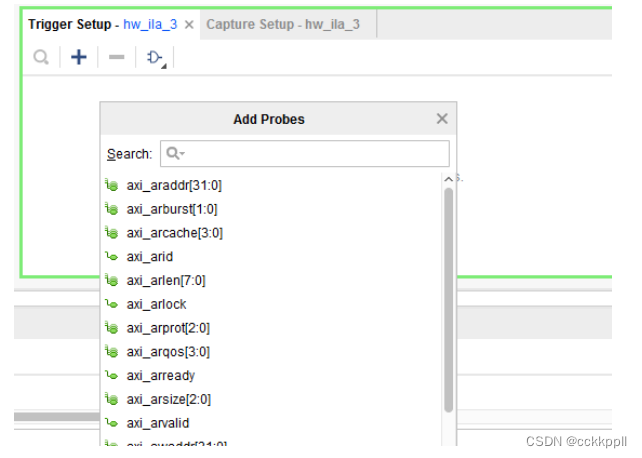

您可通过单击窗口中心的“

+

”按钮并从“添加探针

(Add Probes)

”窗口中选择探针

,

以开始向“触发器设置

(Trigger

Setup)

”窗口添加探针

,

如下图所示。

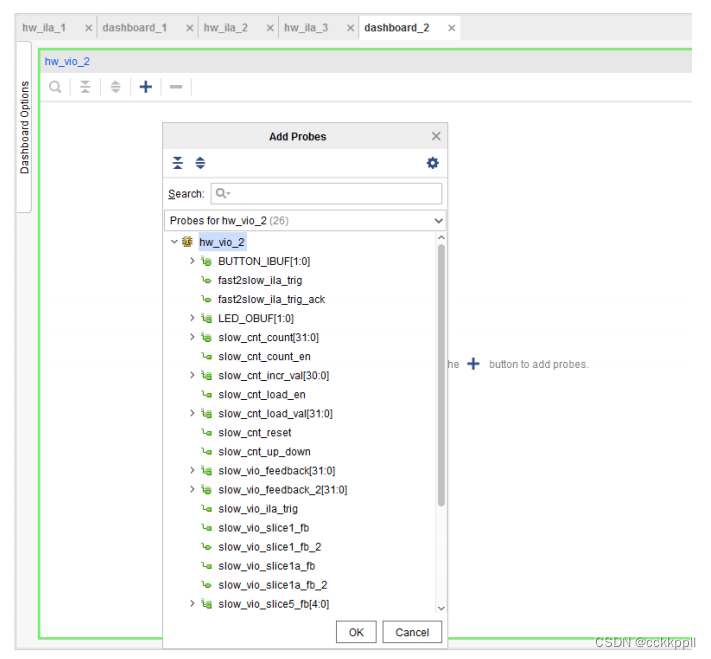

VIO

默认仪表板初始为空

,

您可向其中添加

VIO

探针

,

如下图所示。

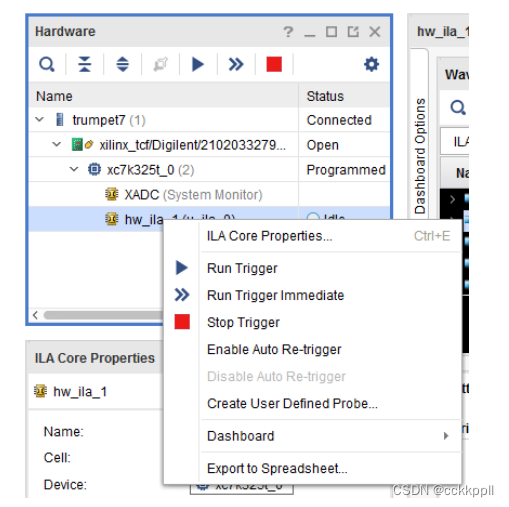

要查看与调试核关联的仪表板

,

请在“

Hardware

”窗口中右键单击调试核对象、选择“

Dashboard

”选项

,

然后单击

仪表板名称。双击“

Hardware

”窗口中的调试核将弹出与该调试核关联的仪表板。

仪表板内部的窗口控件

每个窗口都具有下列标题栏控件

,

以支持您操纵该窗口

:

• 最小化

• 最大化

• 关闭

移动窗口

要移动窗口

,

请执行以下操作

:

1.

选中窗口选项卡或标题栏

,

然后拖动窗口。灰色边框表示移动后的窗口位置。

2.

要将窗口落实到位

,

请松开鼠标。

注释

:

将某个窗口拖到另一个现有窗口上则会将这两个窗口选项卡放置在同一区域内。

重要提示

!

您无法将窗口移入或移出工作空间。但可在工作空间内调整窗口大小和移动窗口。

调整窗口大小

• 要调整窗口大小

,

请单击并拖动窗口边框。

注释

:

光标定位于窗口边框时会变为调整大小光标或拖动手柄

,

表示您可单击并拖动窗口边框以调整窗口大小。

• 要扩展窗口以查看整个环境

,

请单击窗口右上角的最大化按钮。

• 要将窗口复原至原始大小

,

请双击窗口标题栏或选项卡。

关闭窗口

• 要关闭窗口

,

请单击窗口右上角的“关闭

(Close)

”按钮。

注释

:

在某些情况下

,

窗口选项卡中也包含此按钮。

• 右键单击窗口选项卡或标题栏

,

然后从弹出菜单中单击“

Close

”。

窗口选项卡

每个窗口都包含对应选项卡

,

您可选中该选项卡以激活该窗口。该选项卡位于某些窗口底部

,

例如

,

“触发器设置

(Trigger Setup)

”窗口和“采集设置

(Capture Setup)

”窗口。

提示

:

要激活后一个选项卡

,

请按

Ctrl+Tab

键。要激活前一个选项卡

,

请按

Ctrl+Shift+Tab

键。要最大化或最

小化窗口

,

请双击该窗口选项卡。

自定义仪表板

通常默认仪表板中的窗口应足以供您调试设计和查看结果。但有时

,

您可能想要移动窗口

(

即

,

自定义仪表板

)

。例

如

,

您可能想要查看

ILA

状态和“

Waveform

”窗口

,

并在同一仪表板内控制

VIO

探针。在此类情况下

,

赛灵思建议自

定义仪表板以满足您的需求。

仪表板选项

每个仪表板左侧都包含“仪表板选项

(Dashboard Options)

”滑出式菜单。请使用仪表板左侧的“

Dashboard Options

”

按钮来打开其“

Dashboard Options

”设置。“

Dashboard Options

”设置允许您控制特定仪表板中显示的窗口。例

如

,

您可以自定义

ILA

仪表板

,

使其同时包含某个

VIO

窗口。如下所示

,

单击

VIO

窗口以将其包含在“

Dashboard

Options

”中

,

这样此

VIO

窗口就会显示在

ILA

仪表板中。现在

,

您即可添加自己感兴趣的

VIO

探针并触发

ILA

窗

口。

单击仪表板左侧的“

Dashboard Options

”按钮即可打开和关闭“

Dashboard Options

”滑出式菜单。

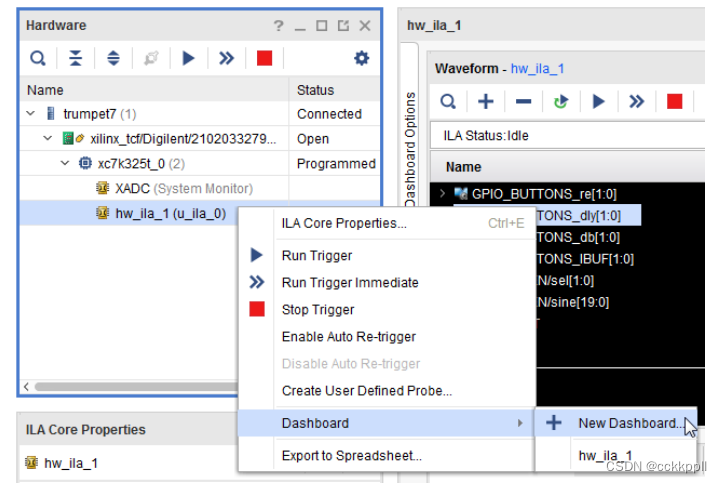

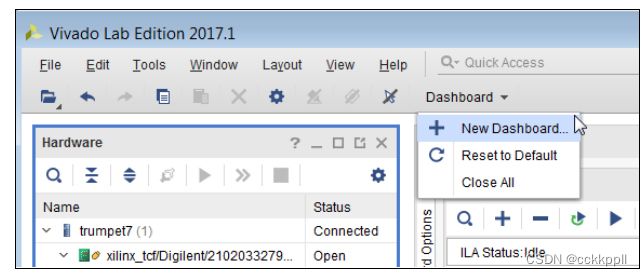

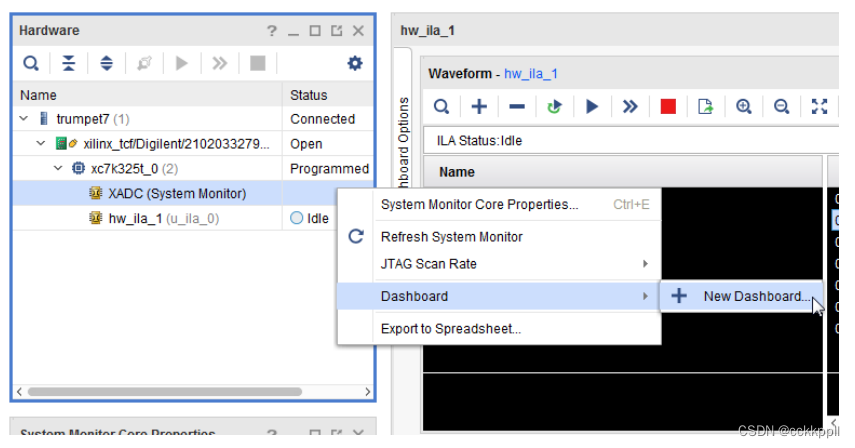

创建新的仪表板

除了使用仪表板选项来自定义默认仪表板外

,

您还可以创建全新的仪表板。要创建新仪表板

,

请在“

Hardware

”窗口

中右键单击调试核对象并选择“

Dashboard

” → “

New Dashboard

”选项

,

如下图所示。

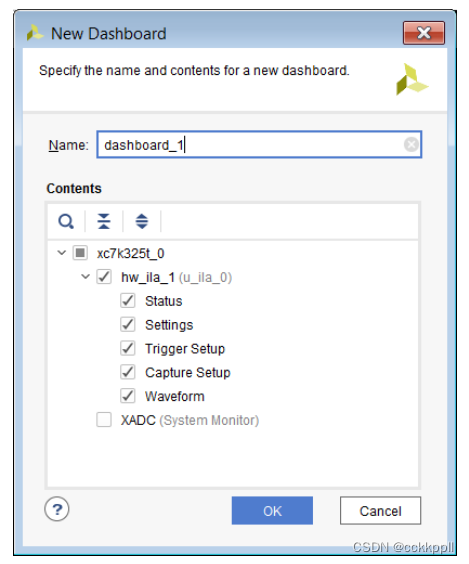

显示“新建仪表板

(New Dashboard)

”对话框时

,

您可根据需要自定义仪表板

,

然后单击“

OK

”。

您也可以使用仪表板工具栏按钮来创建新仪表板

,

如下所示。

提示

:

要查看与调试核关联的所有仪表板

,

请右键单击“

Hardware

”视图中的调试核

,

然后单击

“

Dashboard

”。或者也可以双击“

Hardware

”视图中的调试核

,

这样将弹出与该调试核关联的仪表板列表。

提示

:

要使仪表板上的单一窗口变为浮动

,

赛灵思建议创建仅含该窗口的仪表板

,

并使该仪表板变为浮动状态。

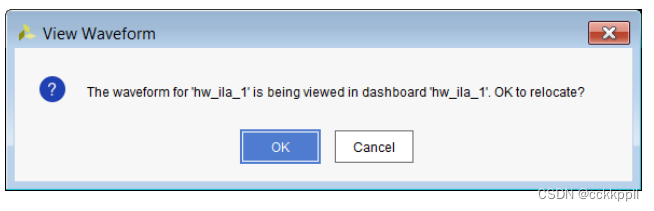

仪表板中的

ILA

波形窗口

每个

ILA

波形窗口都只能显示在单个仪表板中。如果您单击位于另一个仪表板中的“

Waveform

”窗口

,

则将显示通知

称此窗口位置已重定位

,

如下图所示。

单击“

OK

”即可将“

Waveform

”窗口重定位至指定仪表板中。

提示

:

关闭“

Waveform

”窗口时请保存

ILA

数据。

系统监控器仪表板

您可将“

XADC/

系统监控器

(XADC/System Monitor)

”窗口包含在其自己的仪表板中

,

也可将其包含在另一个仪表板

中。

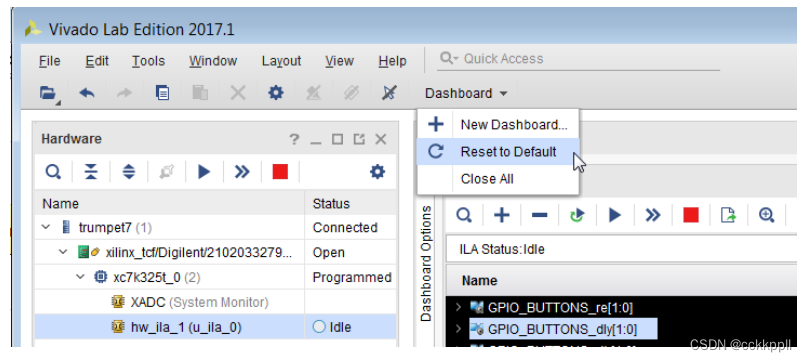

复位至默认仪表板

您可通过单击工具栏上的“

Dashboard

”并选择“

Reset to Default

”来将仪表板复位至默认状态。

关闭仪表板

您可通过单击工具栏上的“

Dashboard

”并单击“

Close All

”来关闭所有仪表板。这将删除所有仪表板及其中的用户设

置。

您也可以通过单击单个仪表板的右上角“

X

”按钮来将其关闭。这将删除该仪表板及其中的所有用户设置。

保存用户仪表板首选项和设置

用户仪表板设置和首选项由

Vivado IDE

自动保存。关闭和重新打开工程时

,

用户设置和首选项将恢复到硬件管理器

中。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/454030

推荐阅读

相关标签