- 1【问题解决】使用uview组件时按官网步骤操作了就是没效果,报了“ReferenceError: uView is not defined”错误_uview使用没有效果

- 2面试两个月!费时一个星期写下万字java面经,希望对大家有帮助!

- 3浅谈质量管理五大工具_新能源厂质量工程师常用工具

- 4Python程序设计作业笔记_python使用input()函数读取输入,输入是字符串,则返回字符串,输入是数值,则返回也

- 5使用ResXmanager实现多语言[转]

- 6使用Opencv-python库读取图像、本地视频和摄像头实时数据_opencv-python 怎么得到csi摄像头实时图像

- 7Kali-Linux-2021.3保姆级安装教程【手把手教你安装Kali】_kali linux 2021.3

- 8vue中配置axios教程-定稿版(三)——页面index.vue中引入和使用接口文件,network查看请求和响应

- 9【Kotlin】函数式编程 ③ ( 早集合与惰性集合 | 惰性集合-序列 | generateSequence 序列创建函数 | 序列代码示例 | take 扩展函数分析 )_kotlin generatesequence

- 10自动驾驶技术:人工智能驾驶的未来

【ZYNQ】从入门到秃头02 ZYNQ硬件介绍和Vivado开发流程_zynq开发

赞

踩

Vivado简介

Vivado设计套件,是赛灵思(Xilinx)公司最新的为其产品定制的集成开发环境,支持Block Design、Verilog、VHDL等多种设计输入方式,内嵌综合器以及仿真器,可以完成从设计输入、综合适配、仿真到下载的完整FPGA设计流程。

Vivado集成了HLS(High Level Synthesis)工具,可以实现直接使用 C,C++ 以及 System C 语言对Xilinx的FPGA器件进行编程。用户无需手动创建 RTL,通过高层次综合生成HDL级的IP核,从而加速IP创建。

Vivado这套开发工具提供了非常方便的套件,即使是开发Linux SDK,也不需要像之前嵌入式Linux开发一样各种查找和修改设备树以及驱动的位置,工具尽可能的将需要用的文件以脚本的方式呈现,或者导出在方便查找的位置。

当然,对于Linux的开发,依然需要修改设备树文件和修改驱动,和嵌入式Linux开发过程保持一致,需要注意在输出时文件可能有所变化。还有一个使用成熟开发套件的好处,就是在开发C语言过程中,可以不需要自己写MakeFile了

安装Vivado

Vivado软件的 Xilinx 官方下载地址: http:// china.xilinx.com/support/download.html

Vivado提供了 Linux 版和 Windows 版,Vivado 要求操作系统必须是 64 位。

-

下载解压 Vivado 软件压缩包, 直接点击 xsetup.exe ,进入安装 ,不过为了更好的安装,请关闭杀毒软件,各种电脑管家, 电脑用户名不要有中文,和空格

-

如果提示版本更新,我们忽略更新,点击“ Con tinue

-

点击“ next ”进行安装,可以看到 Vivado 对系统要求

-

点击“ I Agree ”接受各个条款

-

这里选择安装的器件库,由于我们不需要 UltraScale 和 UltraScale 芯片,可以取消勾选,节省安装空间, 其他 保持默认, 点击“ next

-

安装路径这里没有修改,安装路径不能有中文、空格等特殊字符,同时电脑的用户名不要是中文、带空格的名称。可以看到 Vivado 对硬盘大小的要求,至少要有 80 G 。

-

点击“ Install ”安装

-

等待安装,时间较长,如果没有关闭杀毒软件和电脑管家,安装过程可能会被拦截,导致安装软件后不能使用

-

提示安装成功

-

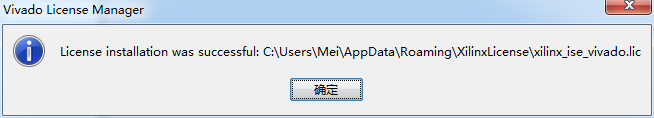

安装 License 文件,点击“ Copy License ”,选择 xilinx_ise_vivado.lic ”文件。

-

可以看到安装成功

重新安装驱动

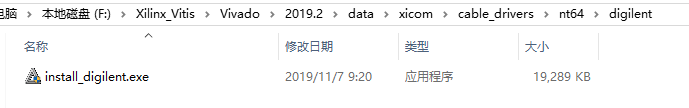

一般安装vivado 时,都会安装下载器驱动。如果需要再次安装下载器驱动,进入 vivado安装路径

“ X XXX Vivado 201 9 2 data xicom cable_drivers nt64 digilent ”

双击install_digilent.exe ”文件安装,安装前先关闭 vivado 软件,如果 vivado 识别不到下载器,请尝试关闭防火墙,杀毒软件,也不能同时打开多个版本的 vivado 、 ise 。

安装完成后,连接下载器 打开设备管理器,在通用串行总线控制器里找到 USB Serial Converter ,说明安装成功

开发板硬件介绍

黑金基于XILINX ZYNQ7000 开发平台的开发板 2016 款正式发布了,型号为: AX7020 。

此款开发平台是 XILINX 的 Zynq7000 SOC 芯片的 解决方案 。

它采用 ARM+FPGA SOC 技术 将 双核ARM Cortex A9 和 FPGA 可编程逻辑 集成在一 颗 芯片上 。 它采用的是 Xilinx 的 Zynq7000 系列XC7Z0 2 0 2 CLG400 I 作为核心处理器, 在 ARM 和 FPGA 上分别 具有丰富的硬件资源和外围接口。

设计上坚持“精致、实用、简洁”的设计理念,它 不但 适合 于软件工作人员的前期的软件验证,也适合于硬件开发人员的硬件设计即软硬件的系统协作,加快项目的开发进程。

此款开发板使用的是Xilinx 公司的Zynq7000 系列的芯片,型号为XC7Z020-2CLG400I,400个引脚的FBGA 封装。ZYNQ7000 芯片可分成处理器系统部分Processor System(PS)和可编程逻辑部分Programmable Logic(PL)。

在AX7020 开发板上,ZYNQ7000 的PS 部分和PL 部分都搭载了丰富的外部接口和设备,方便用户的使用和功能验证。另外开发板上集成了Xilinx USBCable 下载器电路,用户只要用一个USB 线就可以对开发板进行下载和调试。图1-2 为整个AX7020 整个系统的结构示意图:

通过这个示意图,我们可以看到,我们这个开发平台所能含有的接口和功能。

+5V 电源输入,最大2A 电流保护;

Xilinx ARM+FPGA 芯片Zynq-7000 XC7Z020-2CLG400I

两片大容量的4Gbit(共8Gbit)高速DDR3 SDRAM,可作为ZYNQ 芯片数据的缓存,也可以作为操作系统运行的内存;

一片256Mbit 的QSPI FLASH, 可用作ZYNQ 芯片的系统文件和用户数据的存储;

一路10/100M/1000M 以太网RJ-45 接口, 可用于和电脑或其它网络设备进行以太网数据交换;

一路HDMI 图像视频输入输出接口, 能实现1080P 的视频图像传输;

一路高速USB2.0 HOST 接口, 可用于开发板连接鼠标、键盘和U 盘等USB 外设;

一路高速USB2.0 OTG 接口, 用于和PC 或USB 设备的OTG 通信;

一路USB Uart 接口, 用于和PC 或外部设备的串口通信;

一片的RTC 实时时钟,配有电池座,电池的型号为CR1220。

一片IIC 接口的EEPROM 24LC04;

6 个用户发光二极管 LED, 2 个 PS 控制, 4 个 PL 控制

7 个按键, 1 个 CPU 复位按键, 2 个 PS 控制按键, 4 个 PL 控制按键;

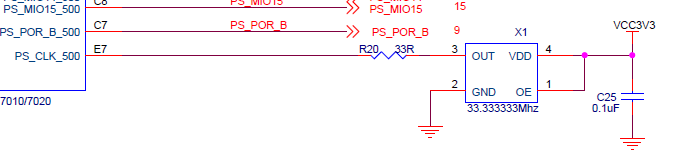

板载一个 33.333 Mhz 的有源晶振,给 PS 系统提供稳定的时钟源,一个 50MHz 的有源

晶振,为 PL 逻辑提供额外的时钟;

2 路 40 针的扩展口 2.54mm 间距 用于扩展 ZYNQ 的 PL 部分的 IO 。可以接 7 寸 TFT

模块、摄像头模块和 AD/DA 模块等扩展模块;

一个 12 针的扩展口 2.54mm 间距 用于扩展 ZYNQ 的 PS 系统的 MIO

一路 USB JTAG 口,通过 USB 线及板载的 JTAG 电路对 ZYNQ 系统进行调试和下载。

1路 Micro SD 卡座 开发板背面),用于存储操作系统镜像和文件系统。

开发板使用的是Xilinx 公司的 Zynq7000 系列 的 芯片 ,型号为 XC7Z0202 CLG400-I 。

芯片的PS 系统 集成了两个 ARM Cortex™ A9 处理器, AMBA® 互连,内部存储器,外部存储器接口和外设。这些外设主要包括 USB 总线接口,以太网接口, SD/SDIO 接口, I2C 总线接口, CAN 总线接口, UART 接口, GPIO 等。 PS 可以独立运行并在上电或复位下启动。 ZYNQ7000 芯片的总体框图如图 4 1 所示

其中PS 系统部分的主要参数如下:

- 基于 ARM 双核 CortexA9 的应用处理器

- 每个 CPU 32KB 1 级指令和数据缓存, 512KB 2 级缓存 2 个 CPU 共享

- 片上 boot ROM 和 256KB 片内 RAM

- 外部存储接口,支持 16/32 bit DDR2 、 DDR3 接口

- 两个千兆网卡支持:发散 聚集 DMA GMII RGMII SGMII 接口

- 两个 USB2.0 OTG 接口,每个最多支持 12 节点

- 两个 CAN2.0B 总线接口

- 两个 SD 卡、 SDIO 、 MMC 兼容控制器

- 2 个 SPI 2 个 UARTs 2 个 I2C 接口

- 4 组 32bit GPIO 54 32+22 )作为 PS 系统 IO 64 连接到 PL

- PS 内和 PS 到 PL 的高带宽连接

其中PL 逻辑部分的主要参数如下:

- 逻辑单元 Logic Cells 85 K

- 查找表 LUTs: 53,200

- 触发器 (flip flops) 106,400

- 乘法器 18x25MACCs 220

- Block RAM 4.9 Mb

- 两个 AD 转换器 可以测量片上电压、温度感应和高达 17 外部差分输入通道, 1MBPS

XC7Z02 0 2 CLG400 I 芯片为 BGA 封装, 400 个引脚,引脚间距为 0.8mm 。再次说明一下 BGA管脚,当我们使用 BGA 封装的芯片以后,引脚名称变为由 字母 数字 的形式,比如 E3 G3 等等,因此我们在看原理图的时候,看到的 字母 数字 这种形式的,就是代表了 BGA 的引脚。

ZYNQ启动配置

AX702 0 开发平台支持三种启动模式。这三种启动模式分别是 JTAG 调试模式 ,QSPI FLASH 和SD卡启动模式。 ZYNQ 70 2 芯片上电后会检测响应 MIO 口的电平来决定那种启动模式。用户可以通过核心板上的 J13 的跳线 来选择不同的启动模式。 J13 启动模式配置如下表 4 1 所示。

时钟配置

AX7020开发板上分别为 PS 系统和 PL 逻辑部分提供了有源时钟,是 PS 系统和 PL 逻辑可以单独工作。

PS系统时钟源

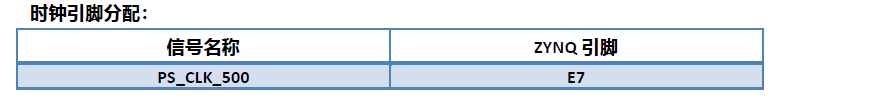

ZYNQ芯片通过开发板上的X1晶振为PS部分提供33.333MHz的时钟输入。时钟的输入连接到ZYNQ芯片的BANK500的PS_CLK_500的管脚上。

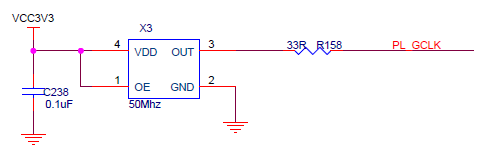

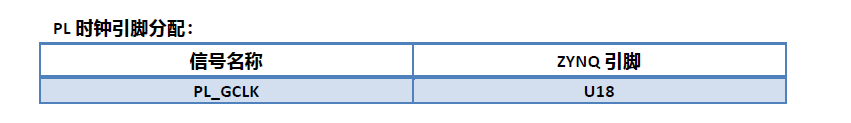

PL系统时钟源

AX7020开发板上提供了单端50MHz的PL系统时钟源,3.3V供电。晶振输出连接到FPGA的全局时钟(MRCC),这个GCLK可以用来驱动FPGA内的用户逻辑电路。

PS端的外设

因为ZYNQ是由ARM系统PS部分和FPGA逻辑PL部分组成,开发板上有些外设是连接到PS的IO上,有些外设是连接到开发板的PL的IO上,首先我们先对PS部分连接的外设做介绍。

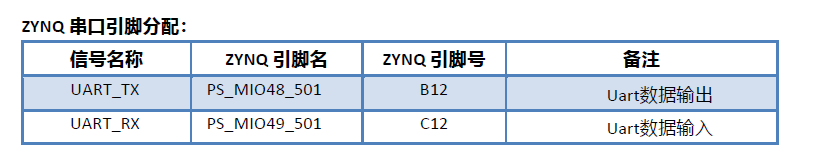

USB转串口

AX7020开发板采用Silicon Labs CP2102GM的USB转UART芯片, USB接口采用Micro USB接口,用户可以用一根Micro USB线连接到PC上进行串口通信。

UART的TX/RX信号与ZYNQ EPP 的PS BANK501的信号相连,因为该BANK的VCCMIO设置为1.8V,但CP2102GM的数据电平为3.3V, 我们这里通过TXS0102DCUR电平转换芯片来连接。

Silicon Labs为主机 PC 提供了虚拟 COM 端口( VCP )驱动程序。这些驱动程序允许CP2102GM USB UART 桥接设备在通信应用软件(例如, TeraTerm 或超级终端)显示为一个COM 端口。 VCP 设备驱动程序必须在 PC 主机与 AX7020 开发板板建立通信前进行安装。

SD卡槽

AX7020开发板包含了一个Micro型的SD卡接口,以提供用户访问SD卡存储器,用于存储ZYNQ芯片的BOOT程序,Linux操作系统内核, 文件系统以及其它的用户数据文件。

SDIO信号与ZYNQ的PS BANK501的IO信号相连,因为该BANK的VCCMIO设置为1.8V,但SD卡的数据电平为3.3V, 我们这里通过TXS02612电平转换器来连接。

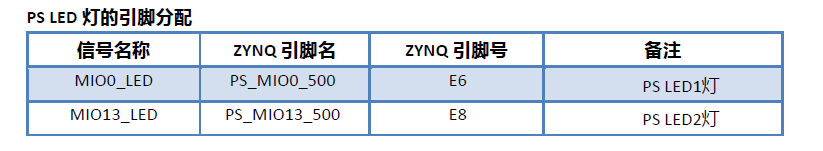

用户LED

AX7020开发板上, PS 部分的 BANK500 IO 上连接了 2 个 LED 发光二极管,用户可以使用这两个 LED 灯来调试程序。 当 BANK500 IO 电压为高时, LED 灯熄灭,当 BANK500 IO 电压为低时, LED会被点亮

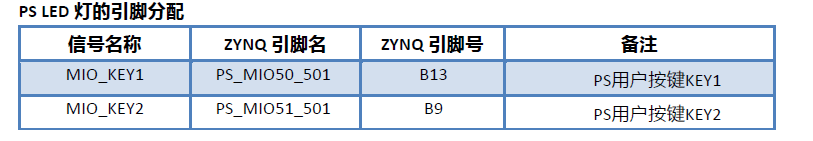

用户按键

AX7020开发板上, PS 部分的 BANK501 IO 上连接了 2 个用户按键,用户可以使用这两个用户按键来测试输入信号和中断触发。设计中按键按下,输入到 ZYNQ BANK501 IO 上的信号电压为低,没有按下时,信号为高。

PL端的外设

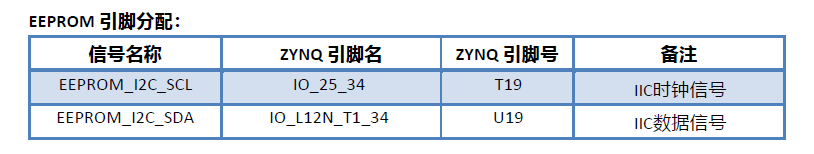

EEPROM 24LC04

AX7020开发板板载了一片 EEPROM ,型号为 24LC04, 容量为: 4Kbit 22568bit ),由 2 个256byte 的 block 组成 通过 IIC 总线进行通信。板载 EEPROM 就是为了学习 IIC 总线的通信方式。 EEPROM 的 I2C 信号连接的 ZYNQ PL 端的 BANK34 IO 口上。

扩展口J10

扩展口J10 为 40 管脚的 2.54mm 的双排连接器,为用户扩展更多的外设和接口,目前ALINX 黑金提供的模块有: ADDA 模块,液晶屏模块,千兆以太网模块 音频输入输出模块矩阵键盘模块,500W 双目视觉摄像头模块 。扩展口上包含 5V 电源 1 路, 3.3V 电源 2 路,地 3路, IO 口 34 路。

IO 口 的信号 连接到 ZYNQ PL 的 B ANK35 和 B ANK35 上,电平默认为 3.3V 扩展口 J10 的部分 IO 可以 通过 更换开发 板上 电源芯片 SPX3819M5 3 3 改变 IO 的电平 。 切勿直接跟 5V 设备直接连接,以免烧坏 FPGA 。如果要接 5V 设备,需要接电平转换芯片。

扩展口J11

扩展口J11 也为 40 管脚的 2.54mm 的双排连接器,为用户扩展更多的外设和接口,目前ALINX 黑金提供的模块有: ADDA 模块,液晶屏模块,千兆以太网模块 音频输入输出模块矩阵键盘模块, 500W 双目视觉摄像头模块 。扩展口上包含 5V 电源 1 路, 3.3V 电源 2 路,地 3路, IO 口 34 路。

IO 口 的信号 连接到 ZYNQ PL 的 B ANK35 上,电平默认为 3.3V 扩展口 J11 的全部 IO 可以 通过 更换开发 板上 电源芯片 SPX3819M5 3 3 改变 IO 的电平 。 切勿直接跟 5V 设备直接连接,以免烧坏 FPGA 。如果要接 5V 设备,需要接电平转换芯片。

用户LED

AX7020开发板的 PL 部分连接了 4 个 LED 发光二极管。 4 个用户 LED 部分的原理图如图 6-1 LED 灯的信号连接到 PL 部分 BANK35 的 IO 上。 当 PL 部分 BANK35 的 IO 引脚输出为逻辑 0时,LED会被点亮,出为逻辑 1时,LED会被熄灭。

用户按键

AX7020开发板的 PL 部分板载了 4 个用户按键 (KEY1~KEY4), 按键的信号连接到 ZYNQ 的BANK34 和 BANK35 的 IO 上。 按键 都 为低电平有效 , 没有按下时,信号为高;按键按下时,信号为低。

Vivado开发流程

由于ZYNQ 将 CPU 与 FPGA 集成在了一起,开发人员既需要设计 ARM 的操作系统应用程序和设备的驱动程序,又需要设计 FPGA 部分的硬件逻辑设计。

开发中既要了解 Linux 操作系统,系统的构架,也需要搭建一个 FPGA 和 ARM 系统之间的硬件设计平台。

所以 ZYNQ 的开发是需要软件人员和硬件硬件人员协同设计并开发的。这既是 ZYNQ 开发中所谓的 软硬件协同设计”。

ZYNQ系统的硬件系统和软件系统的设计和开发需要用到一下的开发环境和调试工具:Xilinx Vivado 。

Vivado设计套件实现 FPGA 部分的设计和开发,管脚和时序的约束,编 译和仿真,实现RTL 到比特流的设计流程。

Vivado 并不是 ISE 设计套件的简单升级,而是一个全新的设计套件。它替代了ISE 设计套件的所有重要工具,比如 Project Navigator 、 Xilinx Synthesis Technology 、 Implementation 、 CORE Generator 、 Constraint 、 Simulator 、 Chipscope Analyzer 、FPGA Editor 等设计工具。

Xilinx SDKSoftware Development Kit SDK 是 Xilin x 软件开发套件 ( 在 Vivado 硬件系统的基础上,系统会自动配置一些重要参数,其中包括工具和库路径、编译器选项、 JTAG 和闪存设置,调试器连接已经裸机板支持包 (BSP) 。

SDK 也为所有支持的 Xilinx IP 硬核提供了驱动程序。 SDK 支持 IP 硬核( FPGA 上)和处理器软件协同调试,我们可以使用高级 C 或 C++ 语言来开发和调试 ARM 和 FPGA 系统,测试硬件系统是否工作正常。

SDK 软件也是 Vivado 软件自带的,无需单独安装。

ZYNQ的开发也是先硬件后软件的方法。具体流程如下:

-

在 Vivado 上新建 工程,增加一个嵌入式的源文件。

-

在 Vivado 里添加和配置 PS 和 PL 部分基本的外设,或需要添加自定义的外设。

-

在 Vivado 里生成顶层 HDL 文件,并添加约束文件。再编译生成比特流文件( (*.bit )。

-

导出 硬件信息 到 SDK 软件开发环境,在 SDK 环境里可以编写一些调试软件验证硬件和软件,结合比特流文件单独调试 ZYNQ 系统。

-

在 SDK 里生成 FSBL 文件。

-

在 VMware 虚拟机里生成 u boot.elf 、 bootloader 镜像。

-

在 SDK 里通过 FSBL 文件 , 比特流文件 system.bit 和 u boot.elf 文件生成一个 BOOT .bin文件。

-

在 VMware 里生成 Ubuntu 的内核镜像文件 Zimage 和 Ubuntu 的 根 文件系统。另外还需要要对 FPGA 自定义的 IP 编写驱动。

-

把 BOOT 、内核、设备树、根文件系统 文件放入到 SD 卡 中,启动开发板电源, Linux操作系统会从 SD 卡里启动。

对于约束输入,主要是两方面,一个是IO的约束,来制定映射和控制的引脚,另一个是时序的约束,告诉我们工具时钟频率多少。

以上是典型的ZYNQ 开发流程,但是 ZYNQ 也可以单独做为 ARM 来使用,这样就不需要关系 PL 端资源,和传统的 ARM 开发没有太大区别。

ZYNQ 也可以只使用 PL 部分,但是 PL 的配置还是要 PS 来完成的,就是无法通过传统的固化 Flash 方式把只要 PL 的固件固化起来。

手把手教你使用Vivado软件——LED

创建工程

有了这些了解,通过一个控制LED灯的历程使用,来学习软件基本的流程

勾中后,这个是询问是否添加设计文件,因为我们是先创立一个工程,然后在空白的工程中添加设计文件,会进入到一个选择芯片的界面

在“ Part ”选项中,器件家族 Family ”选择 Zynq 7000 A X7020 开发板 封装类型Package ”选择 clg 400 Speed 选择 2 减少选择范围。在下拉列表中选择x c7z020clg400-2

“-2 ”表示速率等级,数字越大,性能越好,速率高的芯片向下兼容速率低的芯片。

如果添加设备时添加错误,可在这个位置进行修改

Add Source

三个选项依次是:

添加约束

添加设计文件

添加仿真文件

//****************************************Copyright (c)***********************************// //原子哥在线教学平台:www.yuanzige.com //技术支持:www.openedv.com //淘宝店铺:http://openedv.taobao.com //关注微信公众平台微信号:"正点原子",免费获取ZYNQ & FPGA & STM32 & LINUX资料。 //版权所有,盗版必究。 //Copyright(C) 正点原子 2018-2028 //All rights reserved //---------------------------------------------------------------------------------------- // File name: led_twinkle // Last modified Date: 2019/4/14 10:55:56 // Last Version: V1.0 // Descriptions: LED灯闪烁 //---------------------------------------------------------------------------------------- // Created by: 正点原子 // Created date: 2019/4/14 10:55:56 // Version: V1.0 // Descriptions: The original version // //---------------------------------------------------------------------------------------- //****************************************************************************************// module led_twinkle( input sys_clk , //系统时钟 input sys_rst_n, //系统复位,低电平有效 output [1:0] led //LED灯 ); //reg define reg [25:0] cnt ; //***************************************************** //** main code //***************************************************** //对计数器的值进行判断,以输出LED的状态 assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ; //assign led = (cnt < 26'd5) ? 2'b01 : 2'b10 ; //仅用于仿真 //计数器在0~5000_000之间进行计数 always @ (posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) cnt <= 26'd0; else if(cnt < 26'd5000_0000) // else if(cnt < 26'd10) //仅用于仿真 cnt <= cnt + 1'b1; else cnt <= 26'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

RTL ANALYSIS

有了Verilog代码,下面就是对引脚的映射

这一个步骤其实和Quartus II软件也都很像,编写好代码之后需要把引脚IO进行映射

首先是对时钟引脚进行配置,对应IO需要参考原理图

原理图文件搜索 CLK,找到PL_GCLK,可以看到对应的引脚编号是 U8

然后时钟的第二个引脚,复位信号的约束,这里 是N16,也就是PL_RESET

对于LED灯的引脚

这里我们就选择M14和M15

填写好之后

保存后就可以关闭这个界面了

刚才图形化界面完成的操作可以从Constraints这个文件下看到IO约束信息

Generate Bitstream

然后直接选择生成比特流

编译完成后,取消弹窗界面就可以了,弹窗的选项都可以在其他位置打开

选择自动连接,要提前打开开发板和连接好JTAG线缆

可以看到,自动查找到了我们的开发板型号

点击Program Device,会自动匹配比特流的名称路径

直接点击Program就可以看到开发板的程序跑了起来

配置完成指示灯常亮,LED1 LED2交替闪烁,说明本次实验验证成功!