热门标签

热门文章

- 1错误代码 ILLEGAL_EXTERFACE 电脑网站支付宝提示2018年2月

- 2【python】将文件夹下图片随机抽取一定数量或比例,并复制到新文件夹

- 3每日一题42:最小化字符串长度

- 4App已损坏你应该将它移到废纸篓解决方案_“app uninstaller”已损坏,无法打开。 您应该将它移到废纸篓。

- 5Win系统如何下载安装使用cpolar内网穿透工具?_cpolar下载

- 6小红书算法sign php,签名算法

- 7OpenCV基础入门系列基本操作——壹_( 5分 ) 定义一个容量为256的float型数组,遍历图像的每个像素,并计算直方图,

- 8通过Spring官方教程创建SpringBoot项目_spring官网创建springboot项目

- 9DMDSC部署实践(脚本部署2节点)_dmdsc脚本搭建

- 10Git分支合并操作指南_git合并远程分支

当前位置: article > 正文

【FPGA入门九】状态机实验_fpga第一次实验

作者:小桥流水78 | 2024-07-02 16:33:46

赞

踩

fpga第一次实验

一.实验任务

1、根据以下描述功能用verilog编写一段代码,并用状态机来实现该功能。

(1)状态机:实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程;

(2)描述状态跳转时间;

(3)编码实现。2、画出可以检测10010串的状态图, 并用verilog编程实现之。

二.实验过程

1.测试过程状态机

思路:

由题意可知,该状态机共有6种状态,属于有限状态机,需要在90s内完成6个状态的切换,平均给每个状态15s时间。通过一个计时器,每到15s,状态机的状态就切换一次,利用case语句实现。

①新建工程

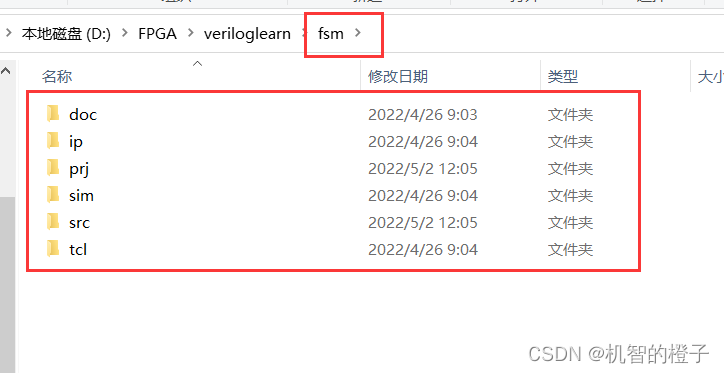

新建一个fsm文件夹,该文件夹下包含以下文件夹

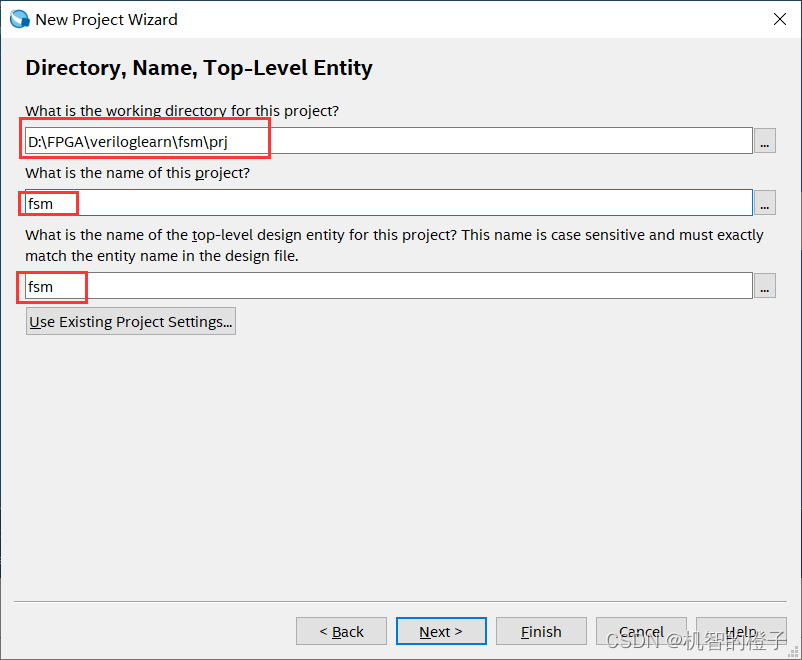

打开Quartus软件,新建工程,将该工程保存在新建的fsm的prj文件夹下

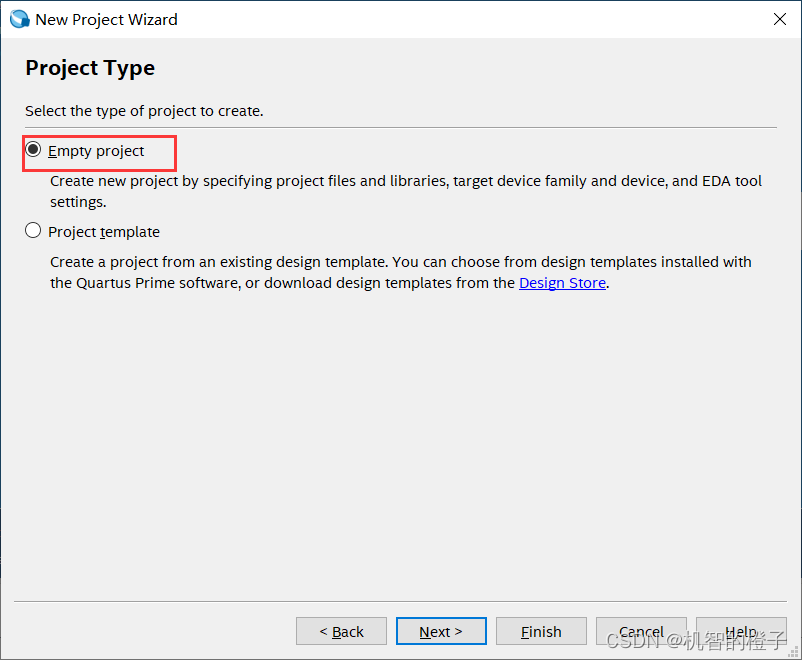

选择空项目

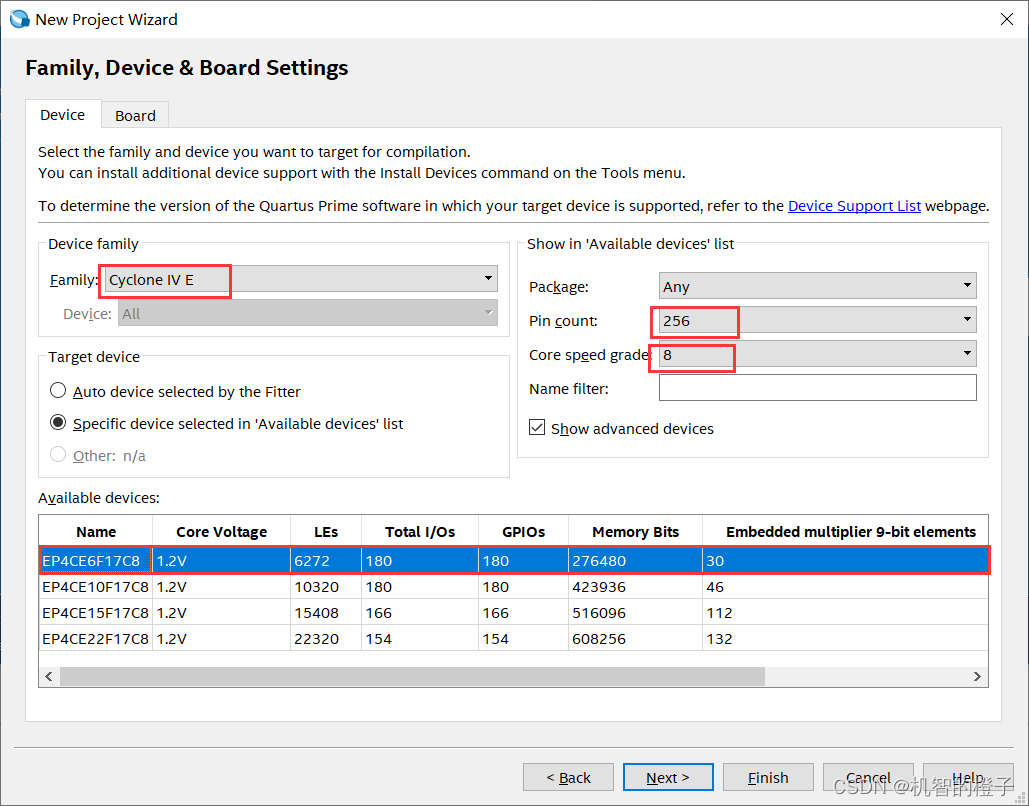

选择芯片

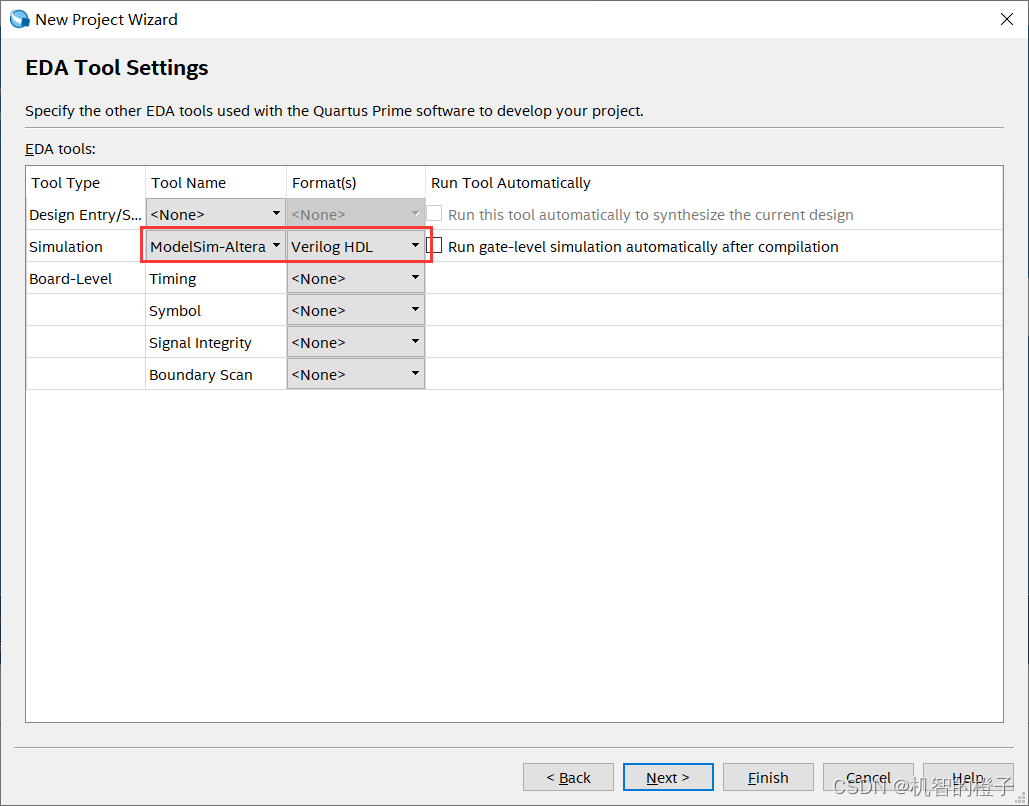

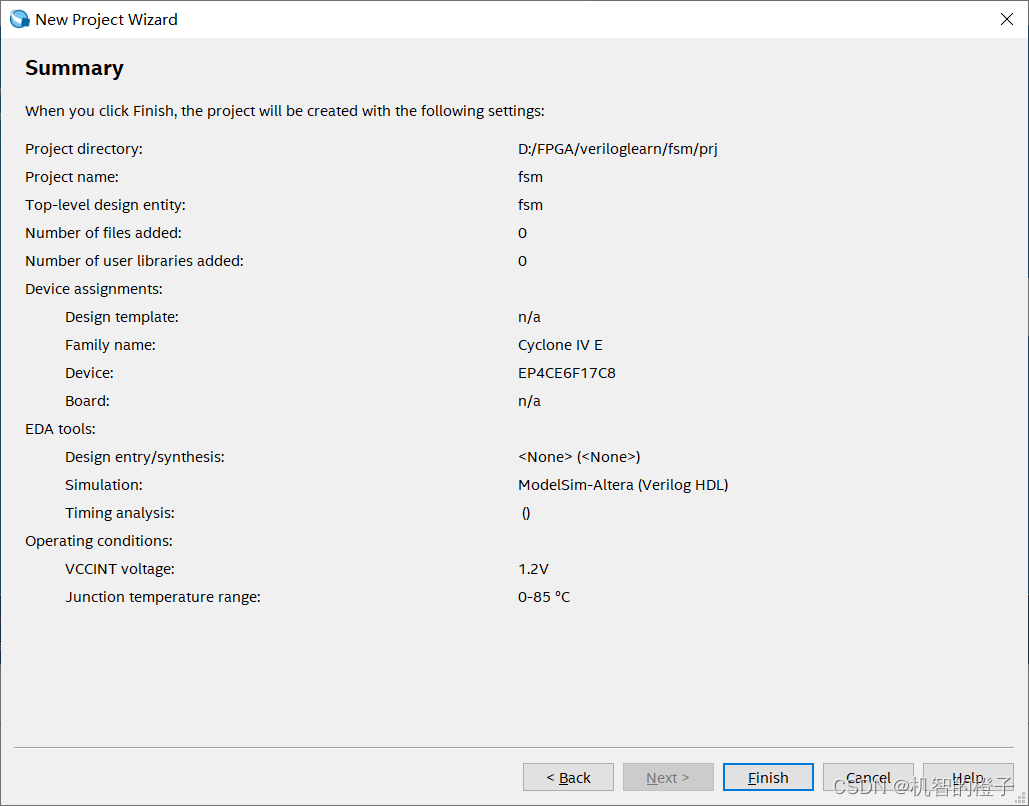

选择仿真工具

工程信息如下:

②设计计时器模块Verilog HDL文件

time_count.v

//15s脉冲信号 module time_count( input wire clk, //时钟,50MHZ input wire rst_n, //复位信号,下降沿有效,negative output wire sec_15//15s输出一个脉冲信号 ); parameter MAX_NUM = 30'd749_999_999;//记最大数15s,750_000_000次 reg [29:0] cnt_15;//计数寄存器 reg sec_15_r; //0.5s计时器 always@(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_15 <= 25'd0; end else if(cnt_15 == MAX_NUM)begin cnt_15 <= 25'd0; end else begin cnt_15 <= cnt_15 + 1'd1; end end //0.5s脉冲信号 always@(posedge clk or negedge rst_n)begin if(!rst_n)begin sec_15_r <= 1'b0; end else if(cnt_15 == MAX_NUM)begin sec_15_r <= 1'b1; end else begin sec_15_r <= 1'b0; end end assign sec_15 = sec_15_r;//当右边改变,立马赋值给左边 assign和always并行 endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

③设计状态机切换模块Verilog HDL文件

module fsm( input clk, input rst_n, input wire sec_15 ); reg [2:0] cstate; //现态 reg [2:0] nstate; //次态 //状态划分 localparam state_ready = 0; //启动准备状态 localparam state_start = 1; //启动测试 localparam state_stop = 2; //停止测试 localparam state_query = 3; //查询测试结果 localparam state_display = 4; //显示测试结果 localparam state_initialize = 5; //初始化 //第一段:现态跟随次态,时序逻辑,非阻塞赋值 always@(posedge clk or negedge rst_n)begin if(!rst_n) cstate <= state_initialize;//复位键被按下,当前状态设置为初始化 else cstate <= nstate; //下一次状态赋值给当前状态 end //第二段:组合逻辑,阻塞赋值 always@(*)begin if(!rst_n) begin nstate = state_initialize; end else case(cstate) state_initialize: begin if(sec_15 == 1'b1) //该状态持续时间为1s,1s后,下一次状态更改为led1亮 nstate = state_ready; else nstate = state_initialize; end state_ready: begin if(sec_15 == 1'b1) nstate = state_start; else nstate = state_ready; end state_start:

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小桥流水78/article/detail/780218

推荐阅读

相关标签