热门标签

热门文章

- 1mysql编写函数_mysql函数编写

- 2chatgpt赋能python:Python虚拟环境virtualenv_virtualenv 退出

- 3Web3系列之1-MERLIN链Airdrop[BianXian]_web3撸空投

- 42024软件测试自动化面试题(含答案)_下单测试

- 5记录一次壮烈牺牲的阿里巴巴面试

- 62022起重机司机(限门式起重机)试题及模拟考试_关于门式、桥式起重机,下列说法正确的是()。【多选】 a.起重机路基和轨道的铺设应

- 7Java多线程并发编程技术详解_java多线程并发代码

- 8java面试题_2019 最新 200 道 Java 面试题

- 9硕果累累 IBM与高校在人工智能落地方面的那些事

- 10python马尔可夫链_3阶马尔可夫链 自然语言处理python

当前位置: article > 正文

基于FPGA的波形信号发生器设计Verilog代码Quartus仿真_基于fpga的波形发生器设计

作者:小桥流水78 | 2024-07-18 21:32:01

赞

踩

基于fpga的波形发生器设计

名称:基于FPGA的波形信号发生器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

利用FPGA可以使用软件编程的方法设计硬件电路,可以方便调整波形的优点,设计一种能够提供正弦波、方波、三角波,脉冲等多种波形的多功能信号发生器。它是一种常用的信号源,可以广泛应用电子测量、自动控制、电子电路等领域。

该设计为多功能信号发生器的设计,主要需要实现以下功能:

基于FPGA设计信号产生模块,可生成幅度可调,频率可调的正弦波,方波、三角波;之后可对波形进行选择,即选取某种波形输出。设计输出脉冲波,输出模式可分为连续触发和单次手动触发。

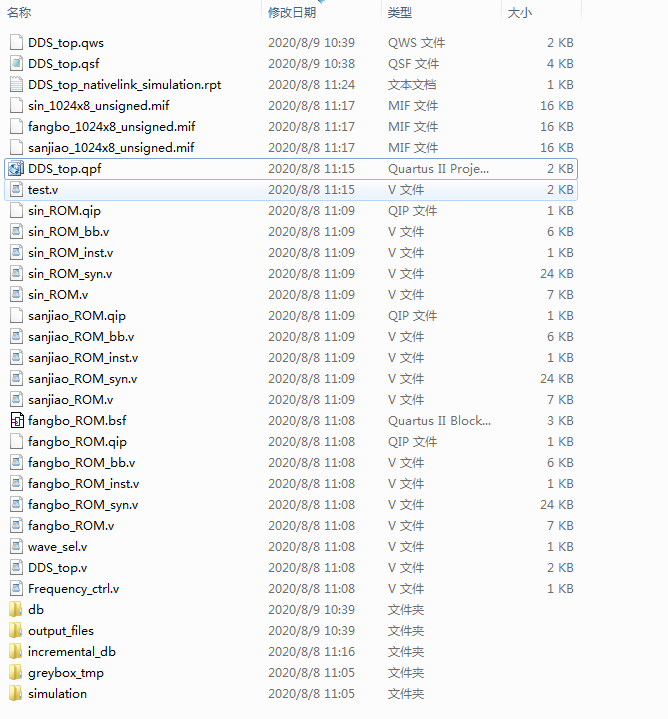

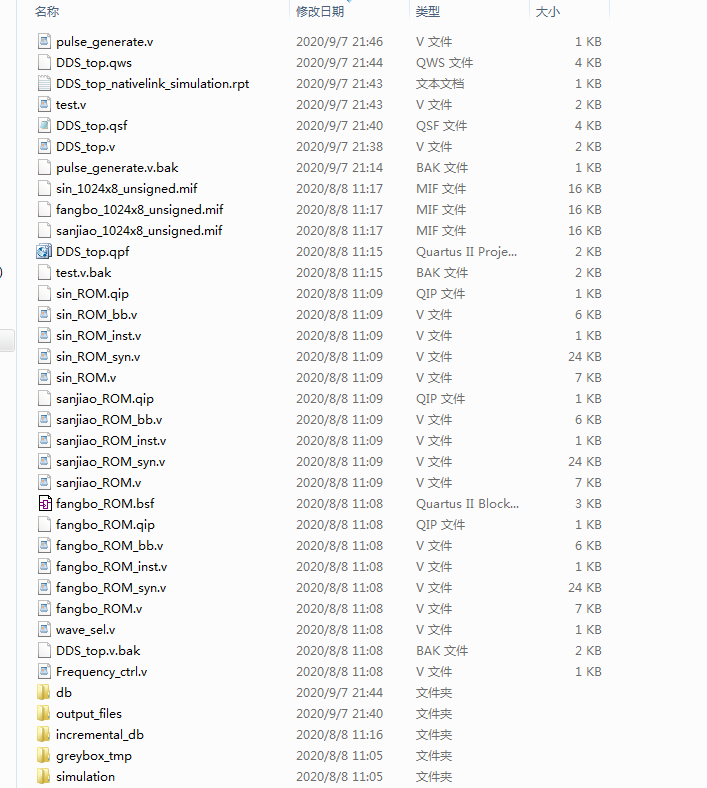

1. 工程文件

2. 程序文件

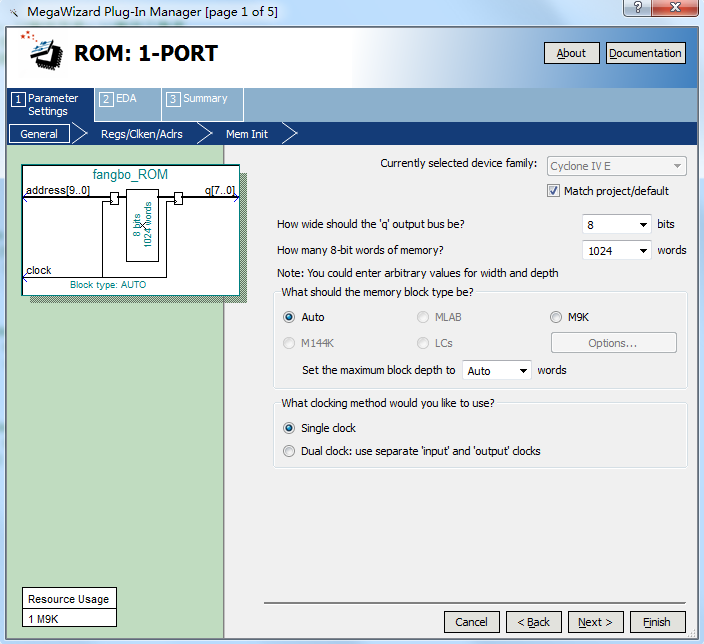

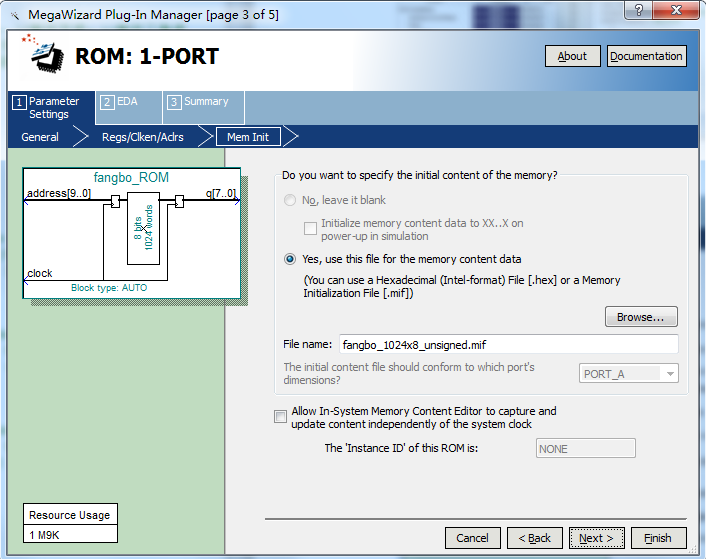

ROM IP

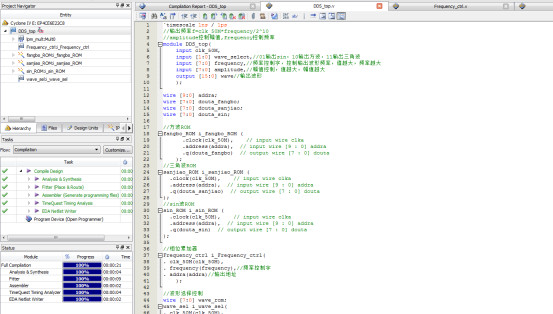

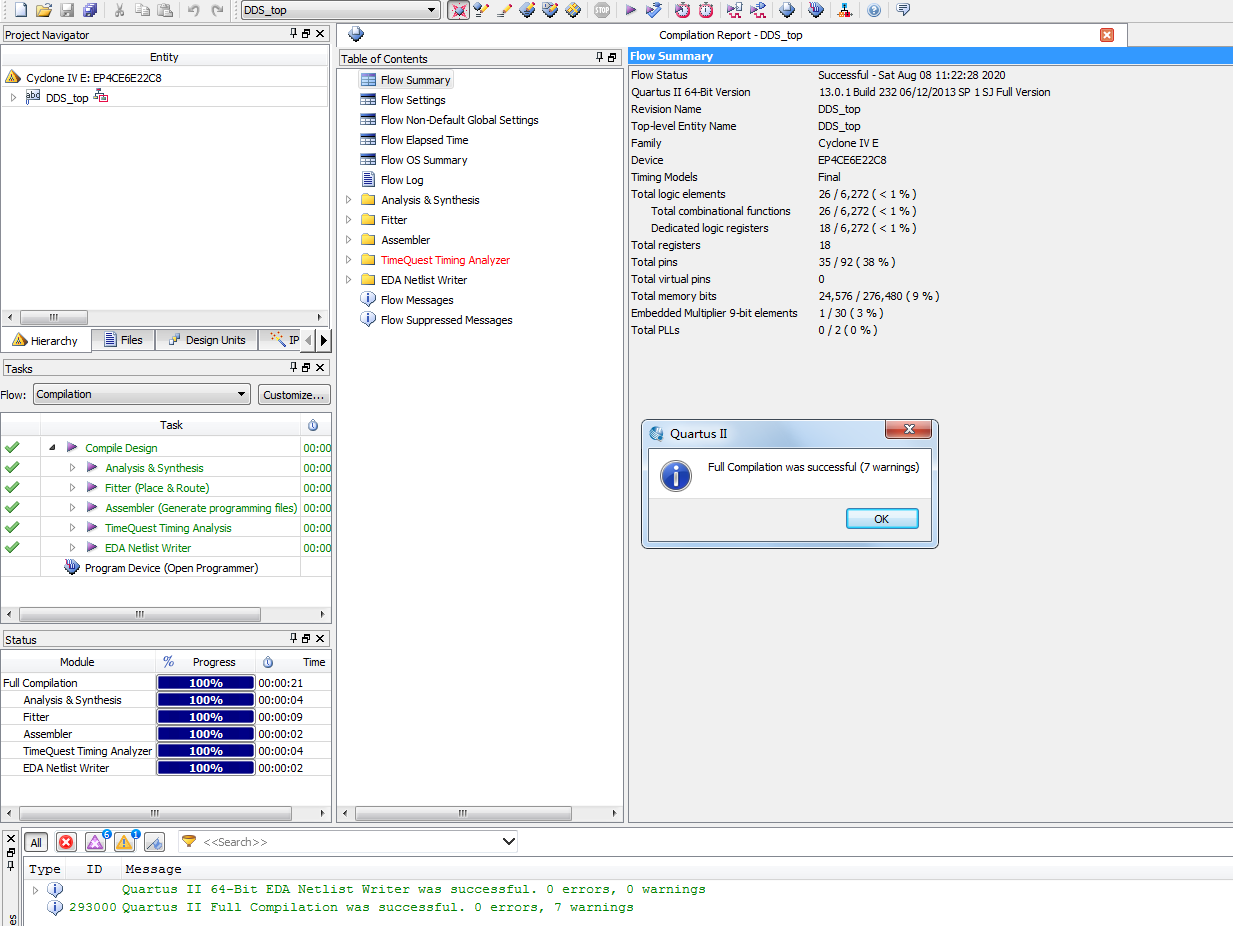

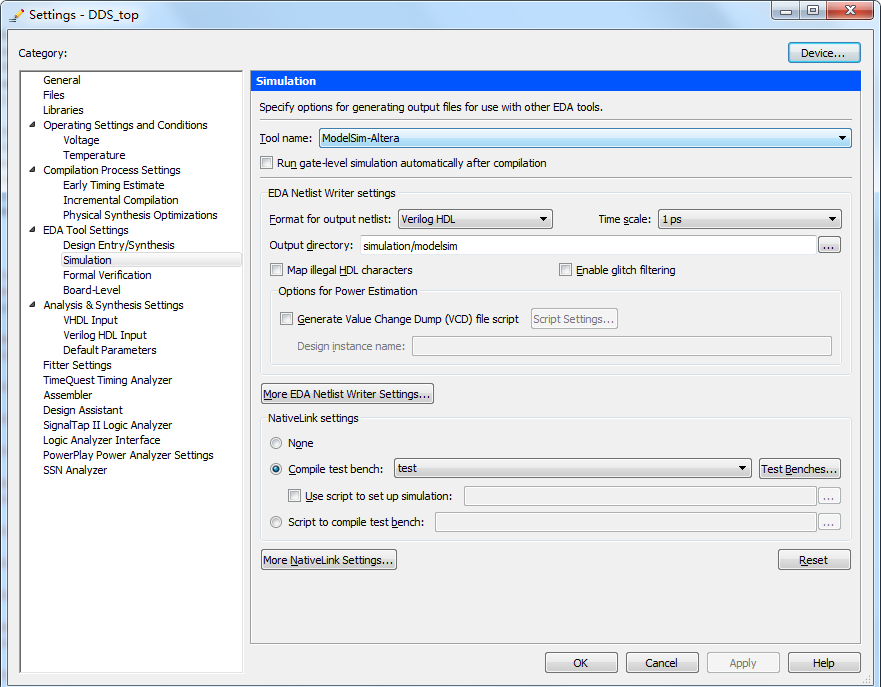

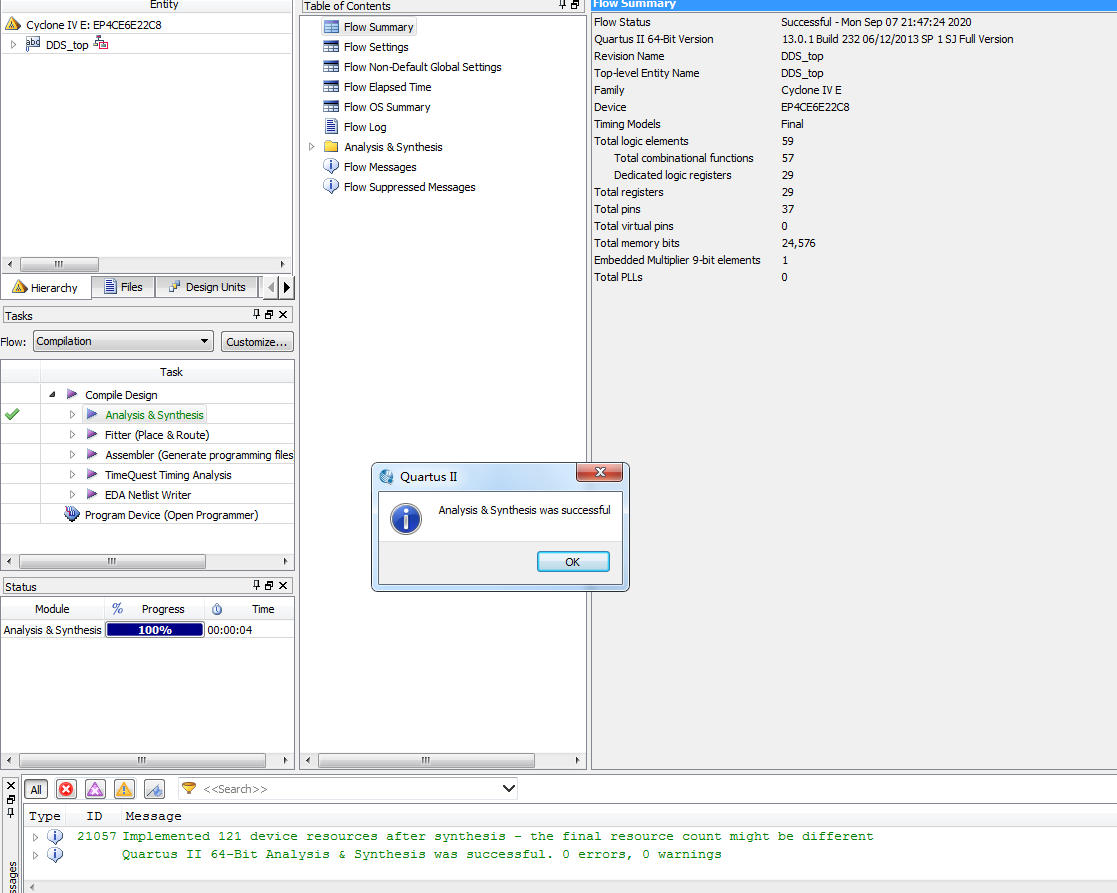

3. 程序编译

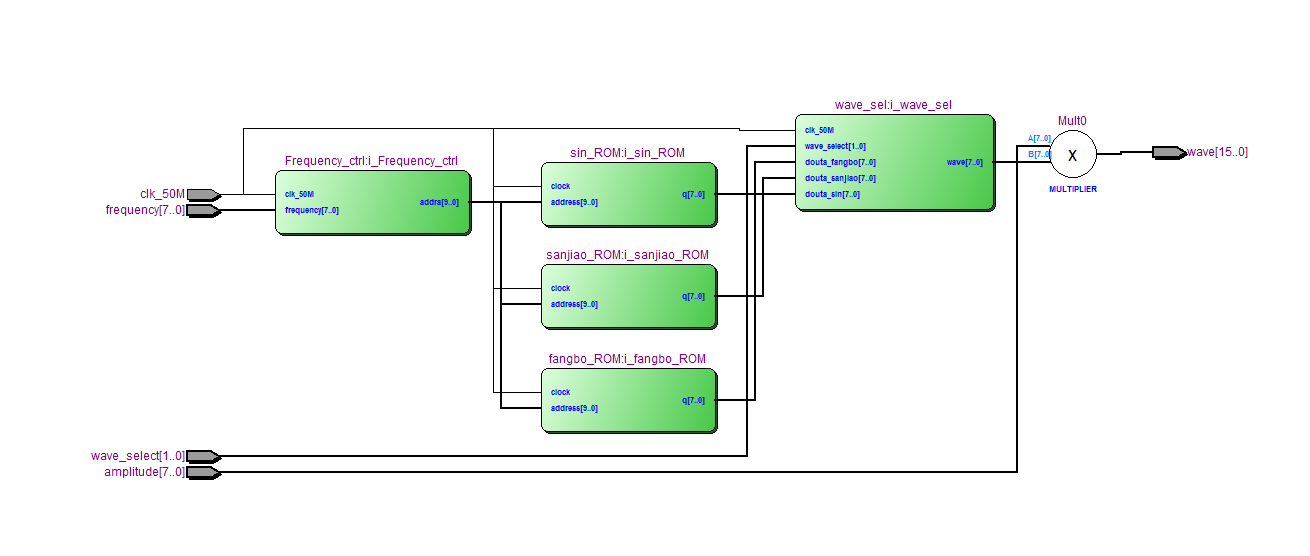

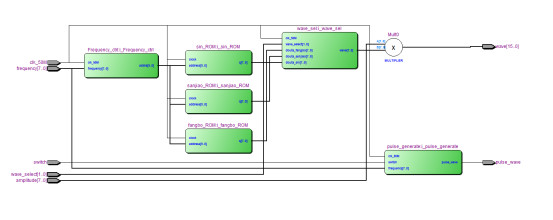

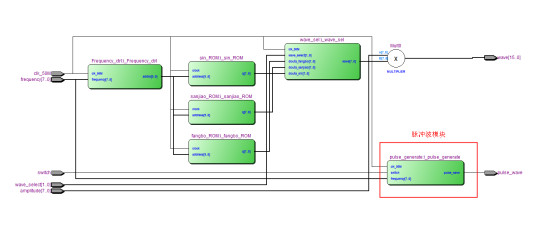

4. RTL图

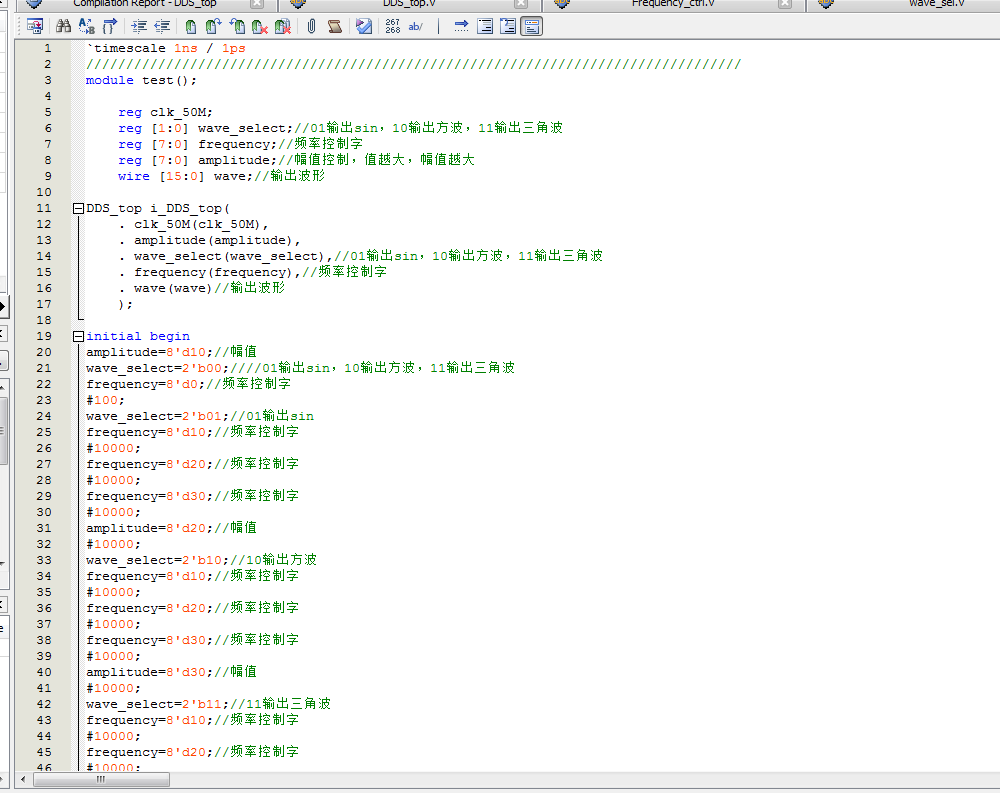

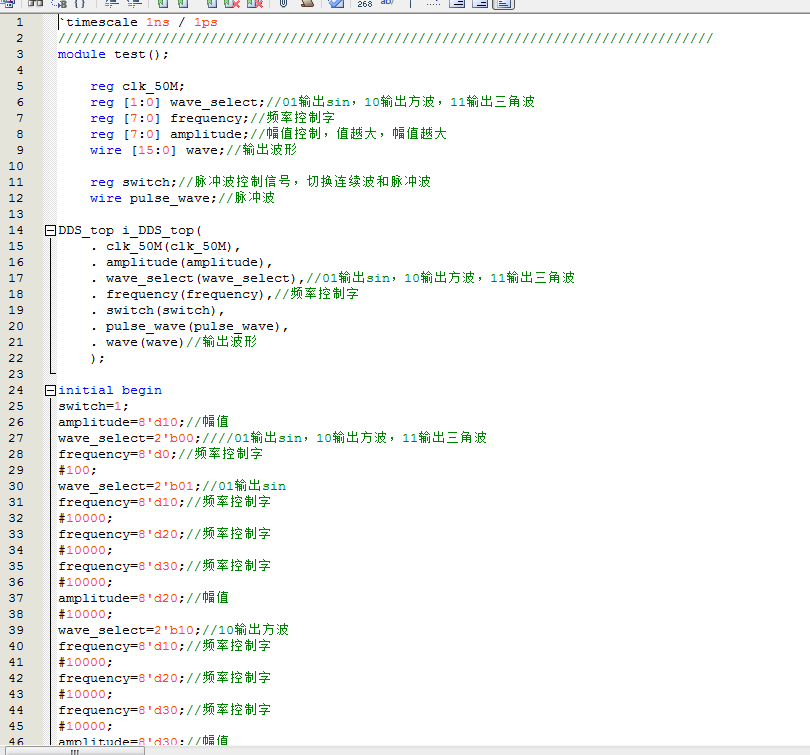

5. Testbench

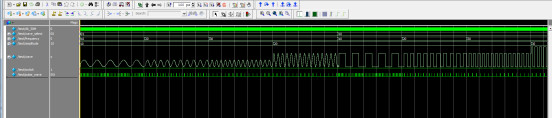

6. 仿真图

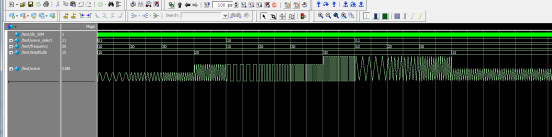

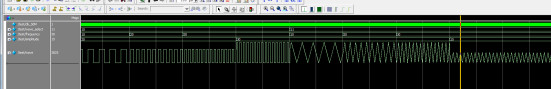

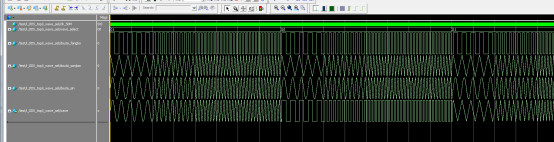

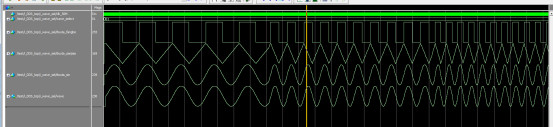

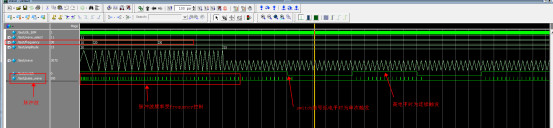

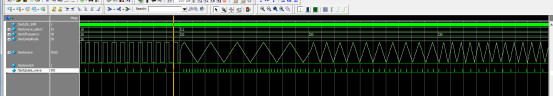

整体仿真图

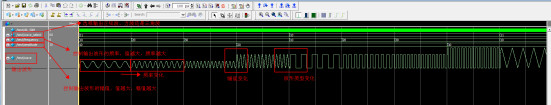

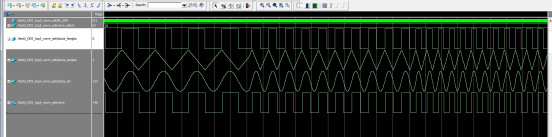

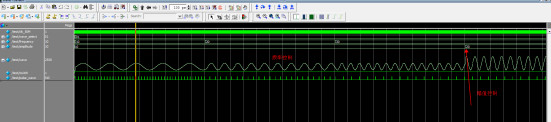

相位累加器模块

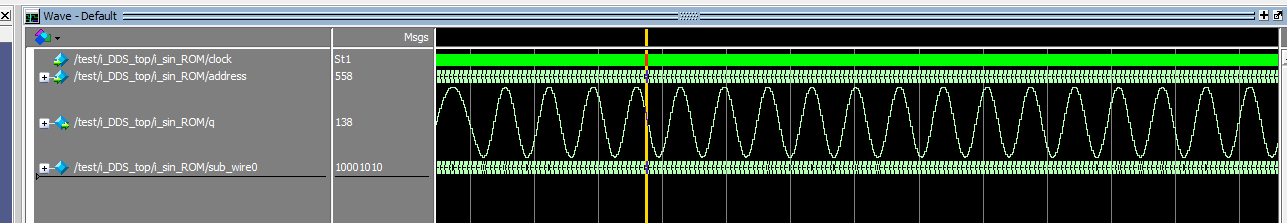

正弦波ROM模块

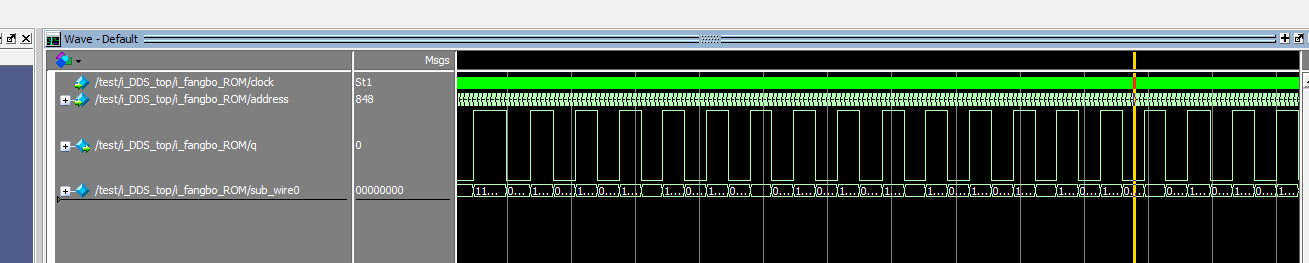

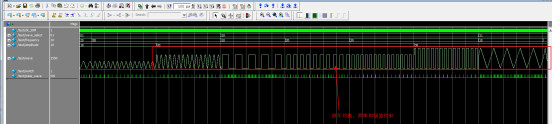

方波ROM模块

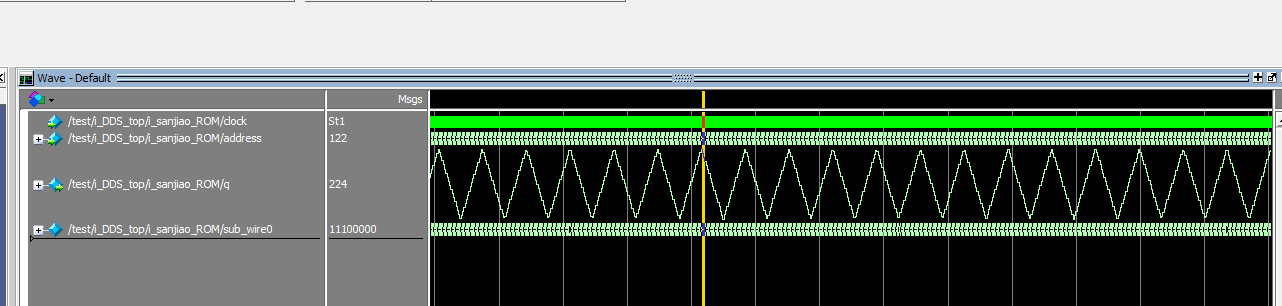

三角波ROM模块

波形选择模块

工程文件

程序编译

RTL图

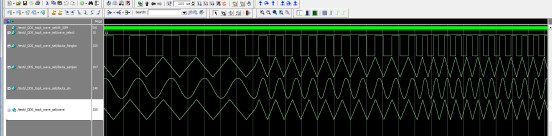

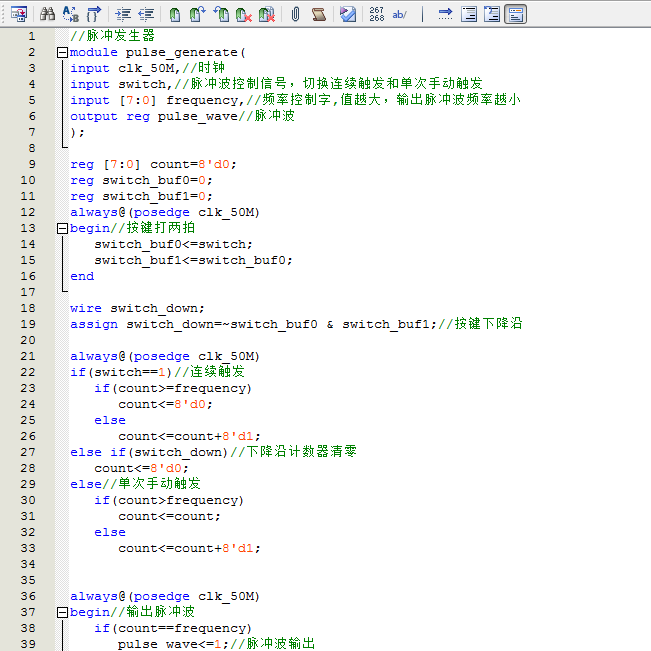

脉冲波模块

Testbench

仿真图

部分代码展示:

`timescale 1ns / 1ps //输出频率f=clk_50M*frequency/2^10 //amplitude控制幅值,frequency控制频率 module DDS_top( input clk_50M, input switch,//脉冲波控制信号,切换连续波和脉冲波 input [1:0] wave_select,//01输出sin,10输出方波,11输出三角波 input [7:0] frequency,//频率控制字,控制输出波形频率,值越大,频率越大 input [7:0] amplitude,//幅值控制,值越大,幅值越大 output [15:0] wave,//输出波形 output pulse_wave//脉冲波 ); wire [9:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; //方波ROM fangbo_ROM i_fangbo_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_fangbo) // output wire [7 : 0] douta ); //三角波ROM sanjiao_ROM i_sanjiao_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM ( .clock(clk_50M), // input wire clka .address(addra), // input wire [9 : 0] addra .q(douta_sin) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_50M(clk_50M), . frequency(frequency),//频率控制字 . addra(addra)//输出地址 ); //波形选择控制 wire [7:0] wave_rom; wave_sel i_wave_sel( . clk_50M(clk_50M), . wave_select(wave_select),//01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_sin(douta_sin), //正弦 . wave(wave_rom)//输出波形 ); //脉冲发生器 pulse_generate i_pulse_generate( . clk_50M(clk_50M),//时钟 . switch(switch),//脉冲波控制信号,切换连续触发和单次手动触发 . frequency(frequency),//频率控制字 . pulse_wave(pulse_wave)//脉冲波 ); //输出波形幅值控制 assign wave=amplitude*wave_rom; endmodule

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签