- 1代码随想录刷题Day59 | 503. 下一个更大元素 II | 42. 接雨水_go实现给定一个循环数组 nums ( nums[nums.length - 1] 的下一个元素是

- 2振动分析-12-轴承数据库之深度学习一维故障分类CNN-Transformer

- 3数据集成与大数据技术:如何处理海量数据

- 4基于STM32居家加湿器控制仿真系统设计-毕设课设_stm32智能加湿器毕设

- 5Keras【Deep Learning With Python】逻辑回归·softmax多分类与交叉熵_keras 多分类交叉熵

- 6程序员创业5年,做了1000多个项目

- 7公司出现这些“高危”征兆,不离职留着过国庆?赶紧走!_一键在防火墙写入阻止规则,用记事本打开可以直接修改做需要阻止的端口

- 8秋招Java后端开发冲刺——MyBatisPlus总结

- 9文本表示(Representation)_文本表示向量的英文

- 10基于packet tracer的网络vlan配置、路由器配置、IP包解析 文档+任务书+拓扑图及配置文件_使用packet tracer实现ip数据包的解析

基于FPGA的交通灯控制系统设计Verilog代码ISE仿真_fpga交通信号灯控制器的设计仿真

赞

踩

名称:基于FPGA的交通灯控制系统设计Verilog代码ISE仿真(文末获取)

软件:ISE

语言:Verilog

代码功能:

一、交通灯控制系统设计实验目的

巩固利用FPGA设计电路的方法

巩固状态机和计数器的设计方法。

二、实验内容

交通灯是城市交通监管系统的重要组成部分,对于保证机动车辆的安全运行,维持城市

道路的顺畅起到了重要作用。本实验在EDA技术的基础上,利用FPGA的相关知识设计了

交通灯控制系统。

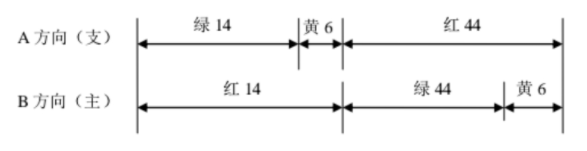

所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路

口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。灯亮时序如下图所示,当B

方向的红灯亮时,A方向对应绿灯亮,由绿灯转换成红灯的过渡阶段黄灯亮,即B方向红

灯亮的时间等于A方向绿灯和黄灯亮的时间之和。同理,当A方向的红灯变亮时,B方向

的交通灯也遵循此规则。各干道上安装有数码管,以倒计时的形式显示本道各信号灯闪亮的时间。

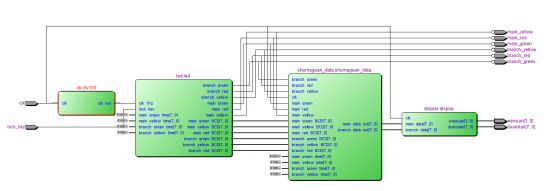

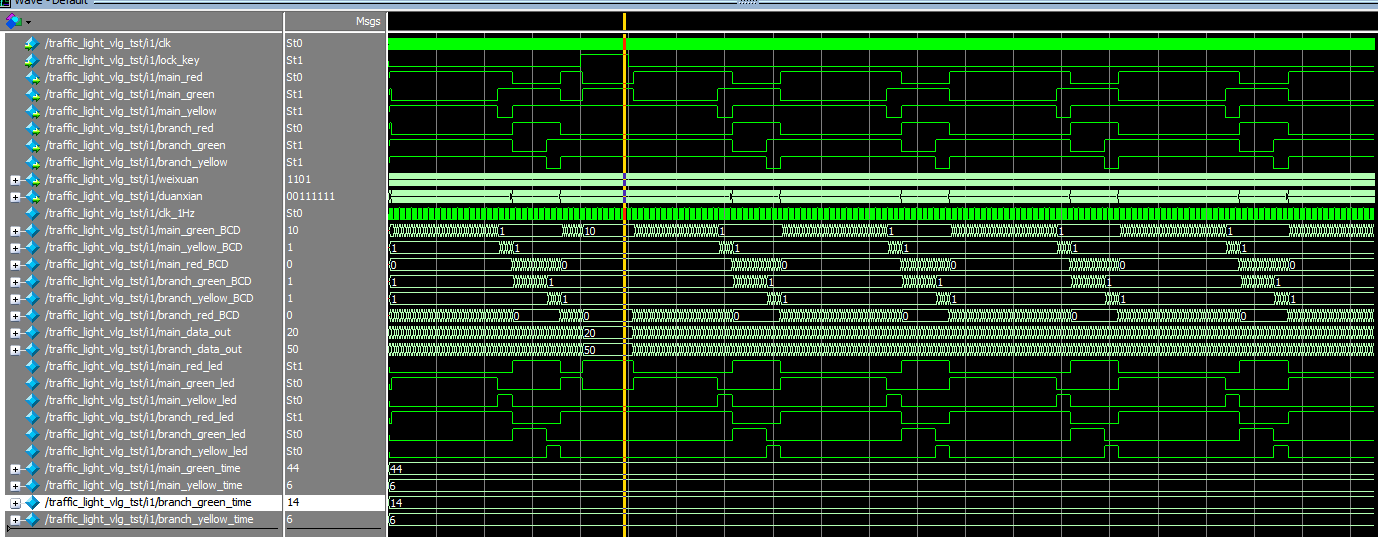

整个系统主要由分频模块、计数模块、显示模块组成。其中分频模块主要将系统输入的基准时钟信号转换为1Hz的激励信号和相应的扫描显示驱动时钟,驱动计数模块和显示模块工作。主干道绿灯和支干道红灯同时亮44秒;黄灯闪6秒;支干道绿灯和主干道红灯同时亮14秒:状态表示黄灯闪6秒。

主干道灯:LEDI:红 LED2绿 LED3:黄

支干道灯:LED5:红 IFD6:绿 IED7:黄

主干道红灯亮的时间=支干道绿灯亮的时间14s+支干道黄灯闪烁的时间6s

支干道红灯亮的时间=主干道绿灯亮的时间44s+主干道黄灯闪烁的时间6s

将SW1拨上,表示出现紧急情况,两条道上的红灯均亮,暂时禁止通行,将SW1拨下

后,恢复正常。

1. 工程文件

2. 程序文件

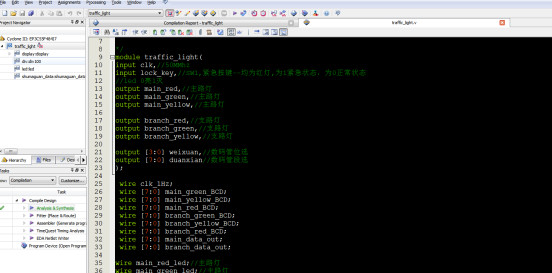

3. 程序编译

4. RTL图(电路结构图)

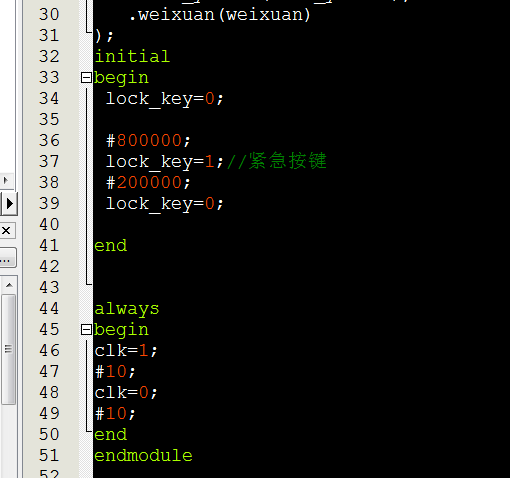

5. Testbench

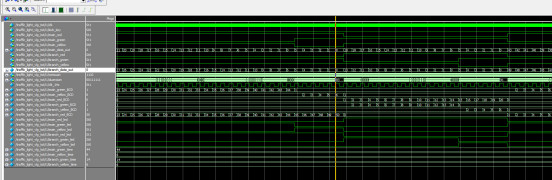

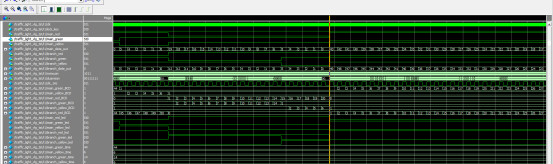

6. 仿真图

Led灯低电平亮

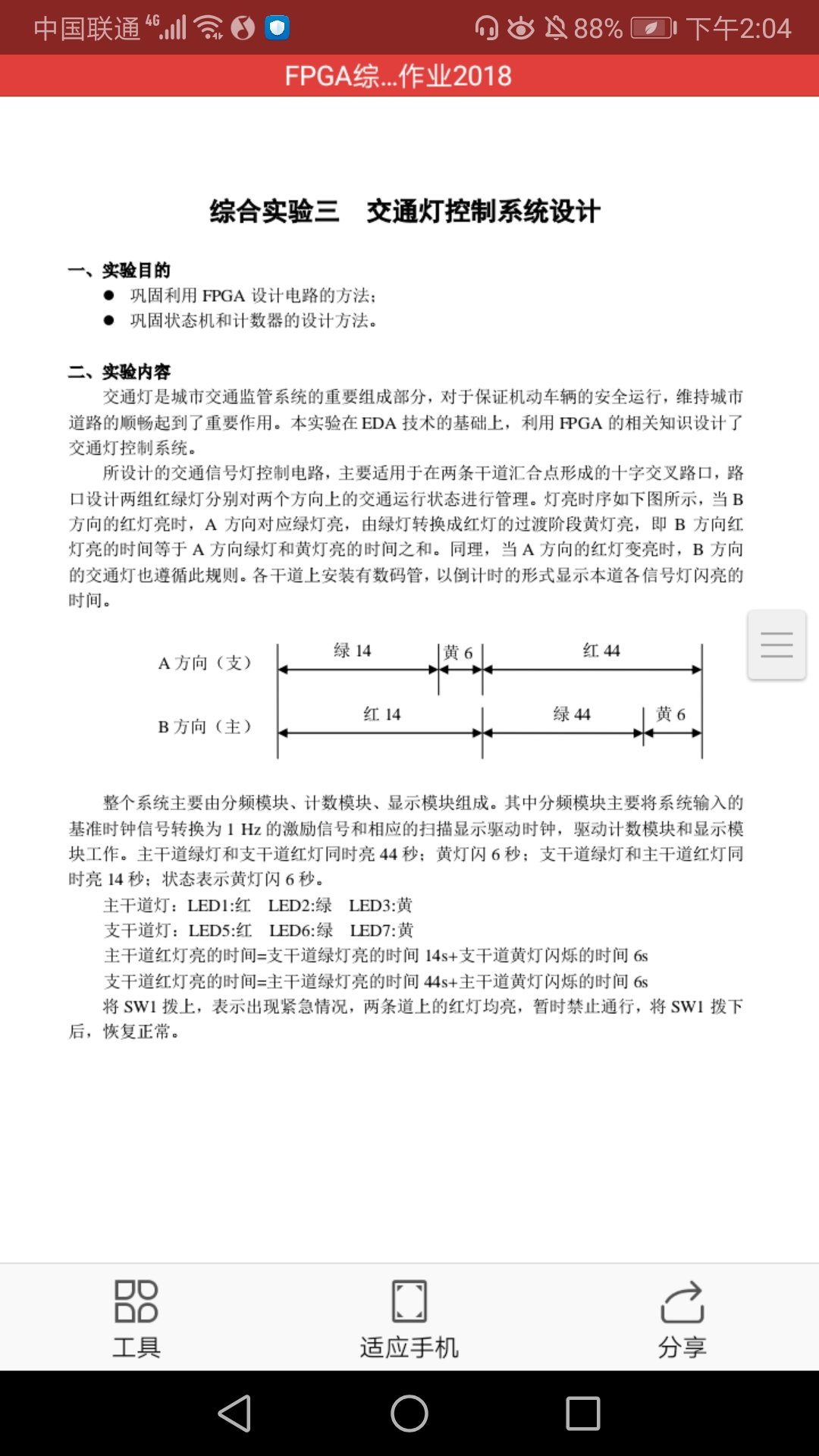

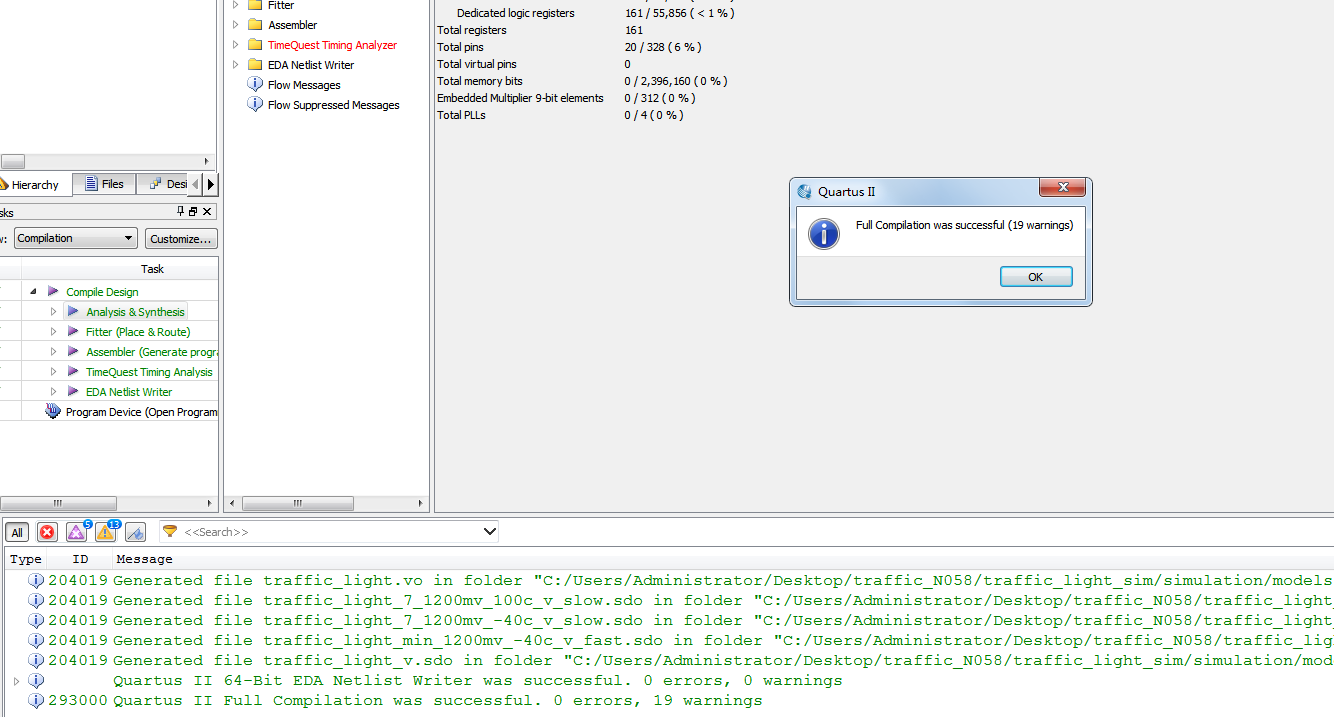

部分代码展示:

//. clk(clk), //. main_data(main_data),//输入总金额,两个数码管 //. branch_data(branch_data),//找零金额,两个数码管 // //. weixuan(weixuan),//位选,高电平亮 //. duanxian(duanxian)//段选,高电平亮 module display ( input clk, input [7:0] main_data,//主路,两个数码管 input [7:0] branch_data,//支路,两个数码管 output reg [3:0] weixuan,//位选,高电平亮 output reg [7:0] duanxian//段选,高电平亮 ); wire [3:0] main_data_ten;//十位 wire [3:0] main_data_one;//个位 wire [3:0] branch_data_ten;//十位 wire [3:0] branch_data_one;//个位 assign main_data_ten=main_data/10; assign main_data_one=main_data%10; assign branch_data_ten=branch_data/10; assign branch_data_one=branch_data%10; reg[15:0]jishu='d0; always@(posedge clk) begin jishu<=jishu+16'd1; end reg [3:0] display_data=4'd0; always@(posedge clk) begin case(jishu[15:14])//显示 2'd0:display_data<=branch_data_ten; 2'd1:display_data<=branch_data_one; 2'd2:display_data<=main_data_ten; 2'd3:display_data<=main_data_one; default:; endcase end always@(posedge clk) begin case(jishu[15:14])//位选,低亮 2'd3: weixuan<=4'b1110; 2'd2: weixuan<=4'b1101; 2'd1: weixuan<=4'b1011; 2'd0: weixuan<=4'b0111; default:weixuan<=4'b0111; endcase case(display_data)//段选,高亮 0 : duanxian= ~(8'hc0); 1 : duanxian= ~(8'hf9); 2 : duanxian= ~(8'ha4); 3 : duanxian= ~(8'hb0); 4 : duanxian= ~(8'h99); 5 : duanxian= ~(8'h92); 6 : duanxian= ~(8'h82); 7 : duanxian= ~(8'hf8); 8 : duanxian= ~(8'h80); 9 : duanxian= ~(8'h90); endcase end endmodule

源代码

扫描文章末尾的公众号二维码