热门标签

热门文章

- 12022年数字IC设计提前批笔试面试全流程分享(前期海投,后期顺利拿到Offer)_联发哥2022-数字ic

- 2Hadoop HDFS 读写流程 | 图文详解_hdfs进行数据读写的过程代码

- 3旅游评论情感分析(1)---爬虫(json篇)

- 4c# mvc如何搭建简单的导航框架_博客园头条推荐!六千字长文,深入思考技术本质,跨平台开发框架AspNetCore的简单实践杂谈...

- 5抖音短视频流量密码:打造强IP,普通人如何抢占红利,快速获得财富

- 6Android [USB]如何开关默认USB调试功能_rk3566 android11 默认关闭usb调试

- 7Git笔记--Win11上传本地项目到github_win11 github

- 8语音质量指标Python(PESQ、STOI、SegSNR、LLR、WSS、CD、LSD、CSIG、CBAK、COVL)_python计算pesq

- 9华为交换、路由器常见命令

- 10git本地分支如何与远端分支关联_git 分支和远程分支关联

当前位置: article > 正文

实验2 组合逻辑电路与时序逻辑电路设计

作者:小蓝xlanll | 2024-04-26 19:35:13

赞

踩

实验2 组合逻辑电路与时序逻辑电路设计

实验目的:

1.构建基于verilog语言的组合逻辑电路和时序逻辑电路;

2.掌握verilog语言的电路设计技巧。

3.完成如下功能:加法器、译码器、多路选择器、计数器、移位寄存器等。

实验内容及步骤:

一、实验原理

原理图文件《数字系统设计_sch.pdf》,找到如下两个部分:

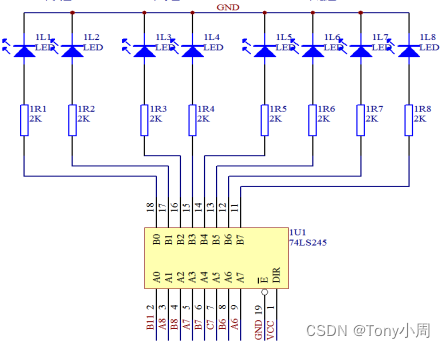

图2.1 Led驱动以及引脚配置

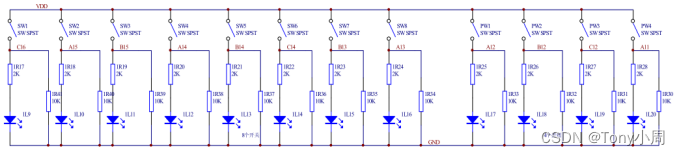

图2.2开关和按键

如图2.1所示,发光二极管1L1到1L8连接到FPGA的引脚号依次为: PIN_B11、 PIN_A8、PIN_B8、PIN_A7、PIN_B7、PIN_C7、PIN_B6、PIN_A6。

如图2.2所示,开关SW1到SW8 连接到FPGA的引脚号依次为PIN_C16、PIN_A15 、PIN_B15、PIN_A14、PIN_B14、PIN_C14、PIN_B13、PIN_A13 。 按键PW1-PW4连接到FPGA的引脚号依次为 A12、B12、C12、A11。

计数器

一般的计数器有 清零、置数、计数等功能。

真值表如下:

| 输入 |

输出 |

功能 |

|||||

| R0 |

R9 |

CLK |

QD |

QC |

QB |

QA |

|

| H |

L |

X |

L |

L |

L |

L |

清0 |

| X |

H |

X |

|||||

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/492763

推荐阅读

相关标签