热门标签

热门文章

- 1【语音转换:客观评价MCD如何计算?】

- 2机器学习运用-民宿价格

- 3OFDM信道估计误码率仿真:LS、LMMSE、LRMMSE、DCT和DFT算法比较_lsmmselmmse信道估计算法

- 4GIT提交命令之git-commit_git commit -s

- 5大数据笔记_海量数据如何存储和计算

- 6Matlab plot画图坐标字体、字号、范围等设置_matlab怎么设置横纵坐标字体

- 7如何将 PyTorch 模型移植到 Tensorflow-第 1 部分

- 8U盘节点变化_disabled by hub (emi?), re-enabling...

- 9嵌入式系统概论-3-嵌入式软件系统_目前嵌入式系统的主流微处理器是

- 10【探索Linux】P.30(序列化和反序列化 | JSON序列化库 [ C++ ] )

当前位置: article > 正文

vitis下测试zynq硬件平台_vitis使用ila

作者:很楠不爱3 | 2024-04-12 03:04:42

赞

踩

vitis使用ila

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。导出硬件平台

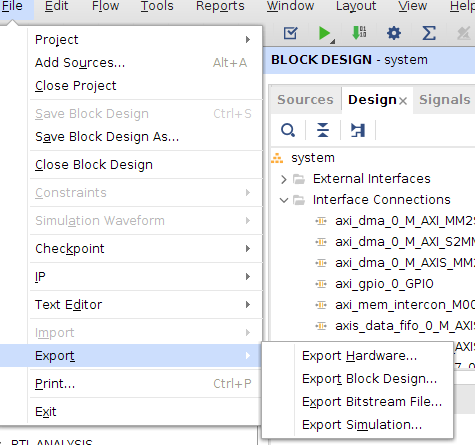

在完成硬件平台搭建后,File-> Export->Export Hardware,选择Fixed,include bitstream,导出.xsa文件。

在Vitis中新建工程

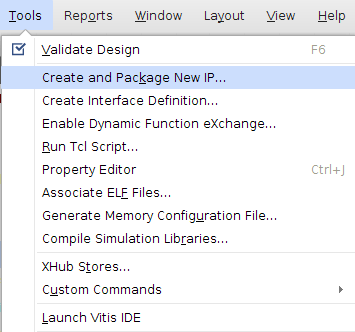

在Vivado中打开Vitis,Tool->Launch Vitis IDE,在Workspace中输入Vitis工作目录。

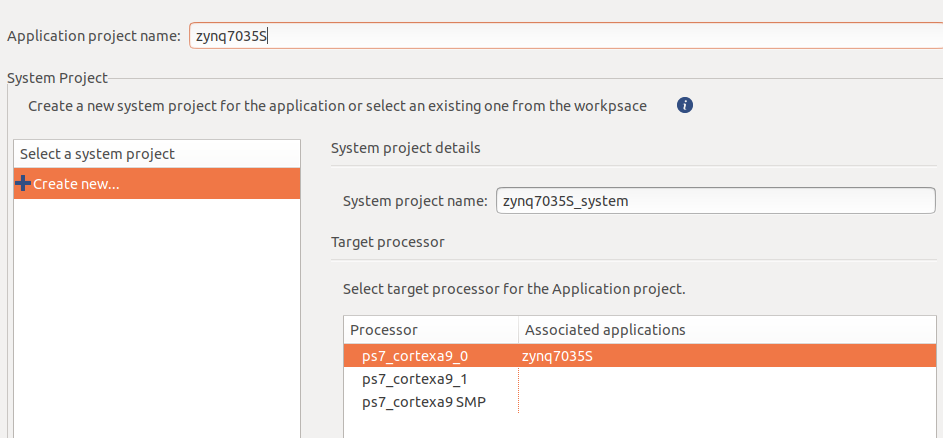

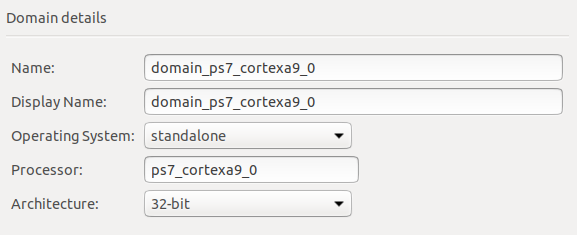

点击Create Application Project,选择Create a new platform from hardware(XSA),选择之前生成的.xsa文件,新建工程zynq7035。

新建Empty Application,Finish。

编写裸机软件代码

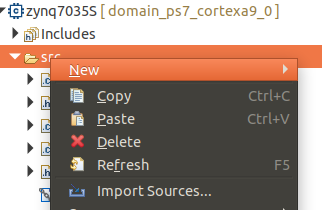

建立好工程后,在src中加入软件代码,点击Import Sources,选择编写好的代码。

编译代码,Build Project。

Vivado和Vitis联合调试

使用Vivado和Vitis联合调试分为以下步骤:

- 在vitis中运行调试程序

- 在vivado中下载程序,设置ila触发条件

- 在vitis中单步运行程序

- 在vivado中查看ila输出结果,在vitis中查看调试结果

在vitis中运行调试程序

右击工程文件,Debug as->1,进入调试界面

在vivado中下载程序

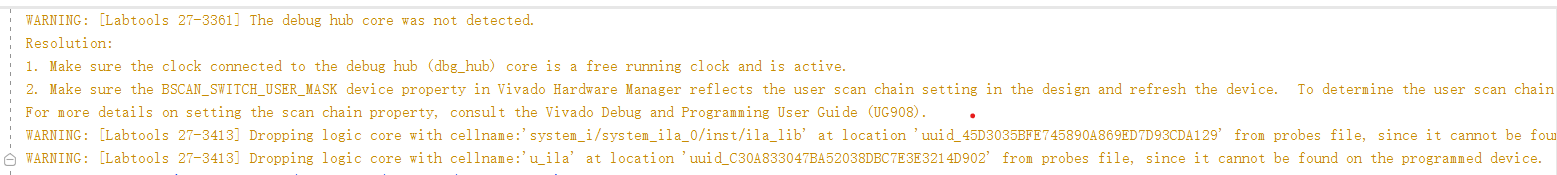

同时下载.bit和ltx文件,下载后遇到如下问题:

在Vitis中运行一下软件代码,然后refresh device可以解决。原因也很好理解,ila时钟使用PS输出,PS先运行后才能输出时钟。

在vitis中单步运行程序

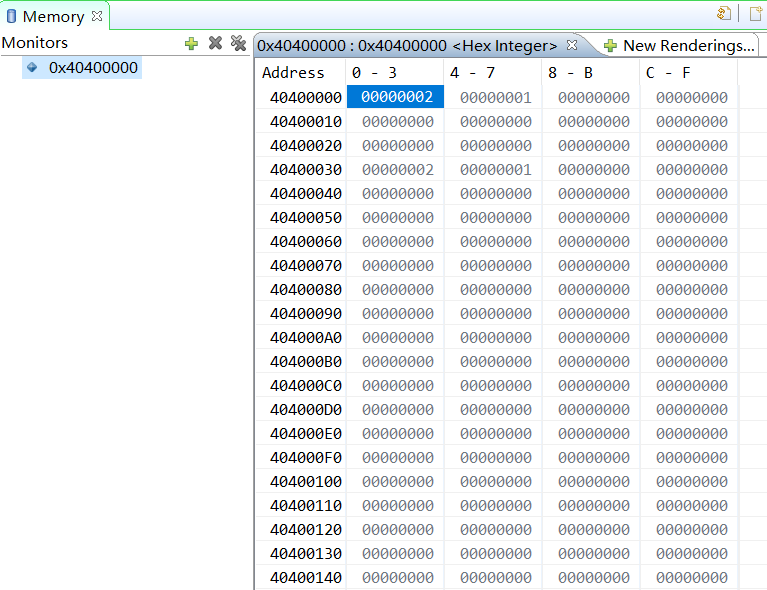

在Window中点击Memory,输入要查看数据在内存中的地址,在Memory中查看数据。

单步运行程序程序

重复上述过程,完成代码调试。

公众号 硬码农二毛哥

推荐阅读

相关标签