- 1VTK读取DCM保存成png_vtk dcm 保存

- 2Python基于季节性自回归移动平均模型(SARIMA模型)进行时间序列分析建模项目实战

- 3全网最详细中英文ChatGPT接口文档(六)30分钟快速入门ChatGPT——使用策略和API数据使用策略_chatgpt api接口规范 pdf 下载

- 4JAVA前后端时间格式的转化_java 后端获取前段时间戳格式转换注解

- 5超详细SQLMap使用攻略及技巧_sqlmap使用教程

- 6python安装包管理插件setuptool/pip/wheel_setuptool修改镜像源

- 7高级工具 zeppelin 整合hive教程_zeppelin hive

- 8刚问世的ChatGPT聊天机器人如何带你把握蔚来Android车载面试_car framework定制

- 9Linux 进入不了图形化界面的终极解决办法_linux开机进不去图形界面

- 10介绍一下MAX30102

【S055】verilog 乘法、除法和取余_verilog 取余

赞

踩

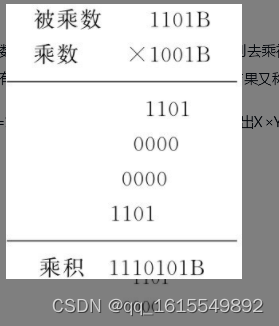

乘法硬件原理

结论

可以将乘法A x B转为A的移位相加。

利用

乘

2

n

就是左移

n

位的特性

乘2^n就是左移n位的特性

乘2n就是左移n位的特性,将数拆分为

2

n

2^n

2n表示

思路1

思路2

B总是可以拆分为:

B

=

(

a

n

2

n

+

a

n

−

1

2

n

−

1

+

.

.

.

+

a

1

2

1

+

a

0

2

0

)

B=(a_n2^n+a_{n-1}2^{n-1}+...+a_12^1+a_02^0)

B=(an2n+an−12n−1+...+a121+a020)

例如:B=4’d10=

1

∗

2

3

+

0

∗

2

2

+

1

∗

2

1

+

0

∗

2

0

1*2^3+0*2^2+1*2^1+0*2^0

1∗23+0∗22+1∗21+0∗20=4’b1010

举例

3 ∗ 10 = 3 ∗ ( 4 ′ b 1010 ) = 3 ∗ ( 2 3 + 2 1 ) = 3 < < 3 + 3 < < 1 = 24 + 6 = 30 3*10=3*(4'b1010)=3*(2^3+2^1)=3<<3+3<<1=24+6=30 3∗10=3∗(4′b1010)=3∗(23+21)=3<<3+3<<1=24+6=30

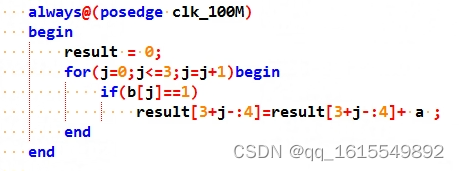

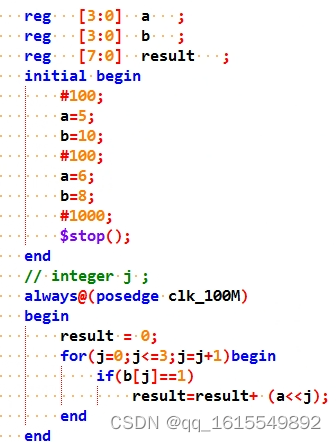

编码

思路1采用原始手算,列竖式思路

思路2采用移位思路:

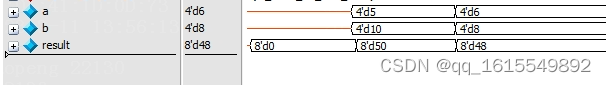

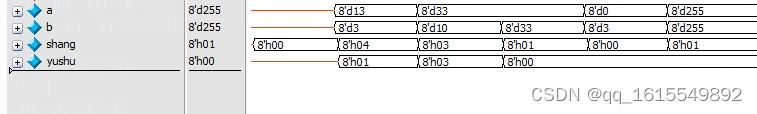

仿真

综合

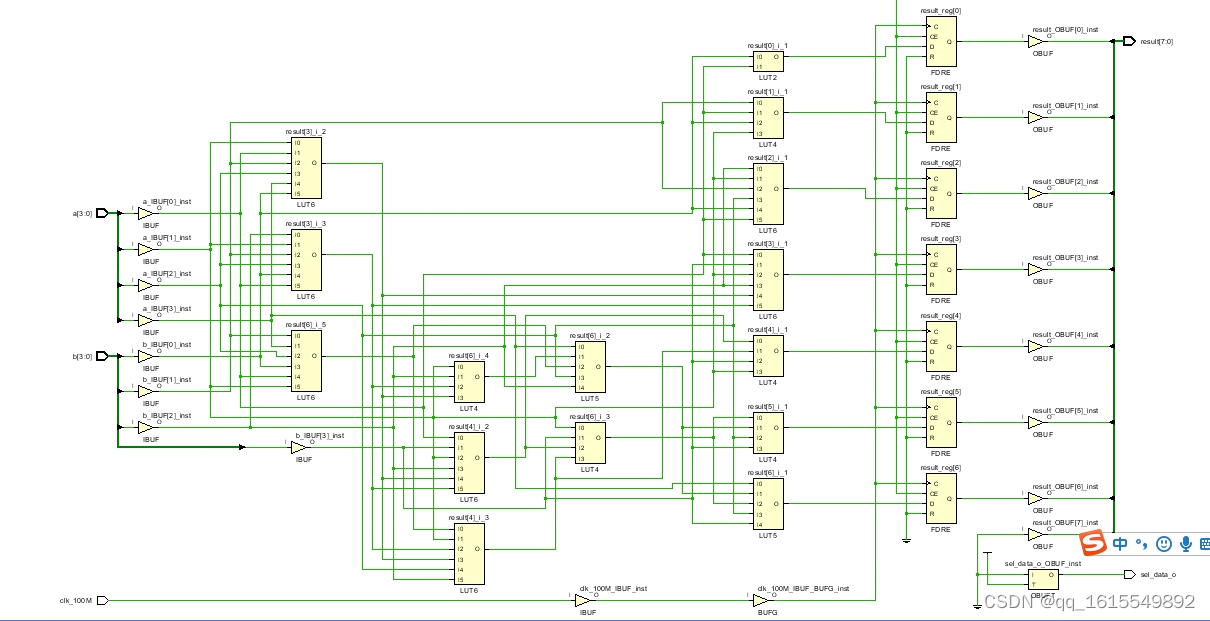

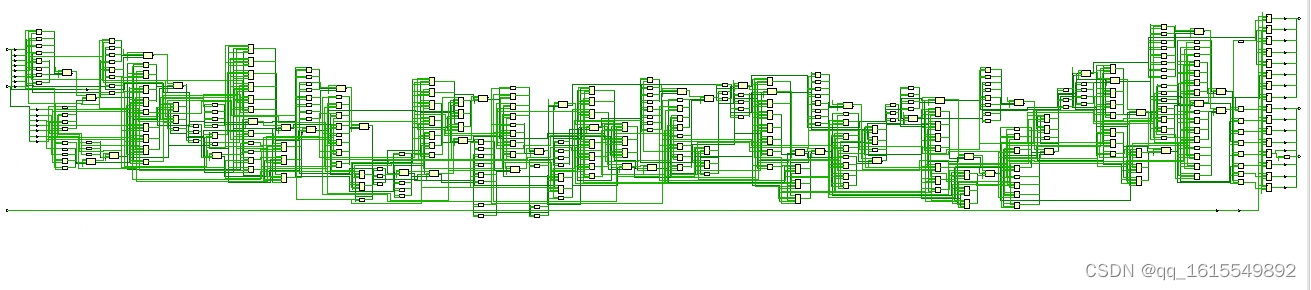

思路1综合如下:

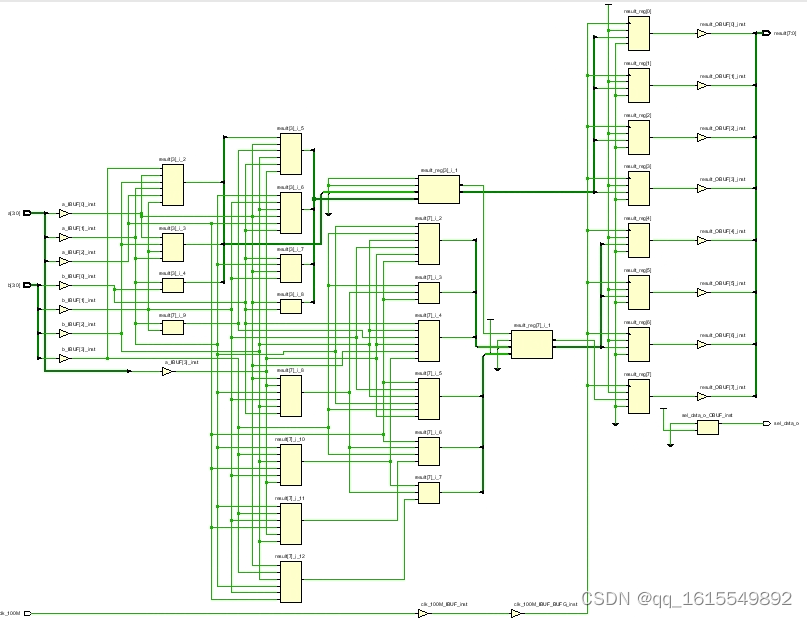

思路2综合如下:

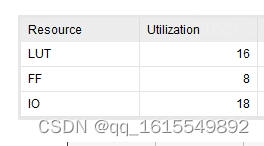

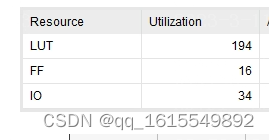

思路1原始竖式方法的资源:

思路2移位方法的资源:

搞半天,原始的方法占资源还少,离谱。

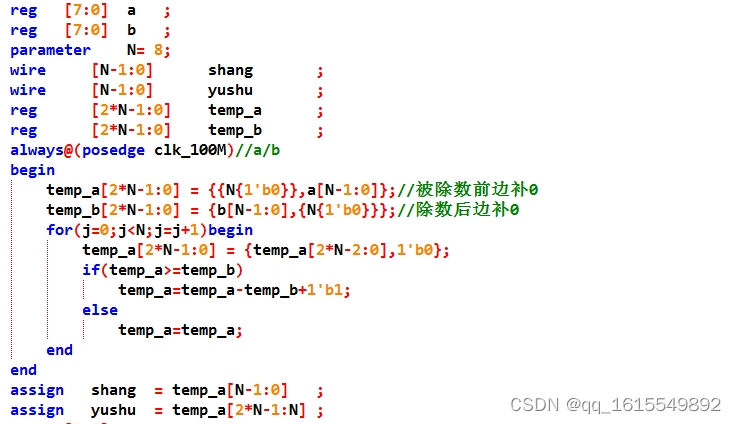

除法硬件原理

我是参考这这个博主的这篇,他写的很好可以先看。

就是手算的思路,改成了硬件方便的实现。移位相减。

verilog代码

仿真结果

资源占用

可以看到资源占不少啊!并且时序也不好。