热门标签

热门文章

- 1cJSON详解

- 22023金九银十Java基础-中级-高级面试题汇总(涵盖所有Java核心面试知识点)_java中级面试题

- 3jenkins插件管理提示“update information obtained:不可用ago”

- 4【Git】error: The following untracked working tree files would be overwritten by checkout

- 5Ubuntu系统下如何使用scp进行远程拷贝文件文件夹?_ubuntu开启远程scp

- 6Midjourney的一些学习心得:如何图生图_midjourney图生图指令

- 7LR 录制Web(HTTP/HTML)脚本的模式选择_lrjs

- 87大必备应用推荐,为你的 Nextcloud 实例增添更多效率功能_nextcloud应用插件

- 9Navicat Premium15的安装_navicat premium 15百度网盘

- 100代码,不用app esp32cam 视频小车 后续升级:开灯,微信配网

当前位置: article > 正文

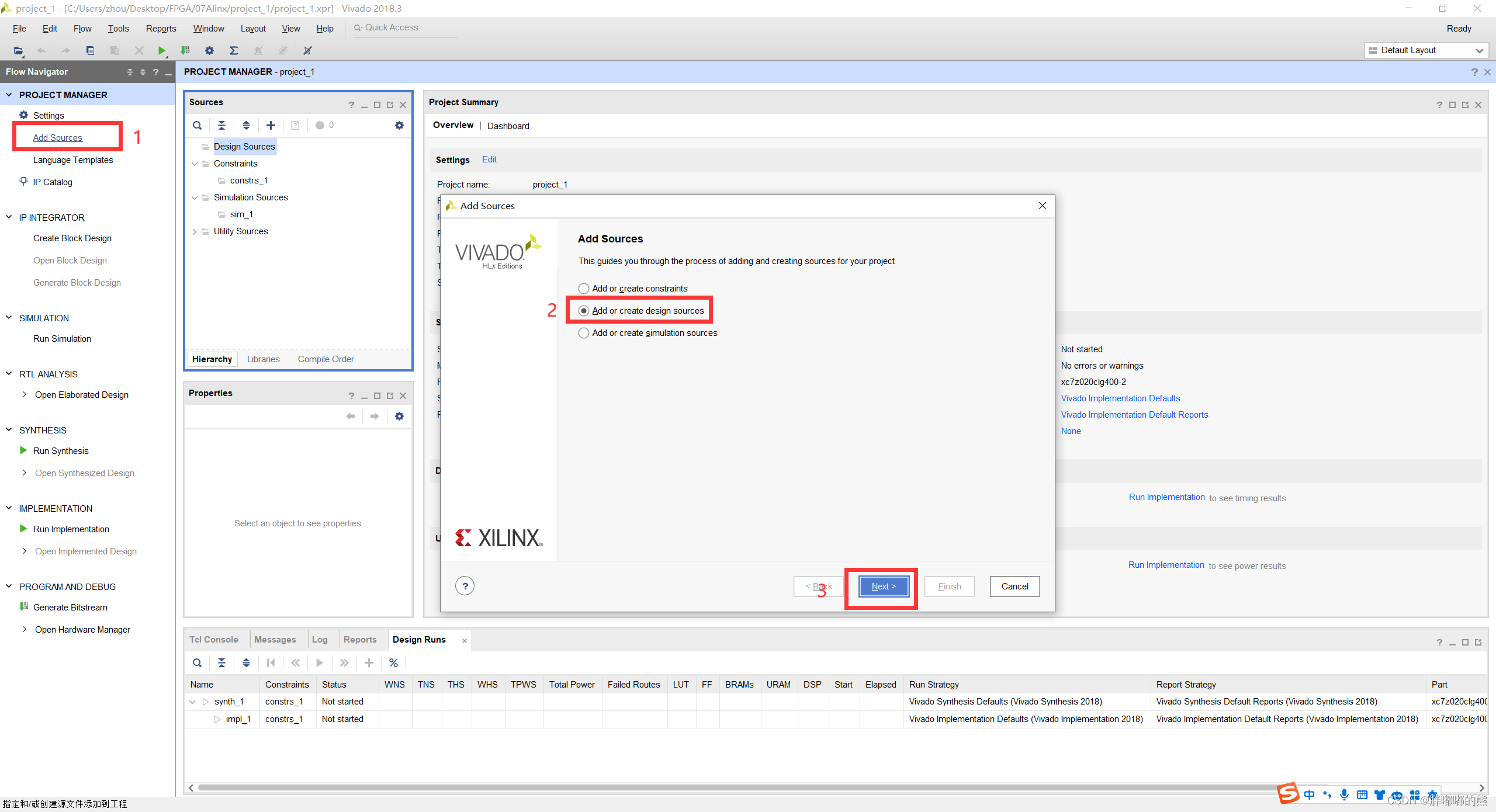

入门篇1-如何用Vivado写verilog代码_vivado怎么打代码

作者:我家自动化 | 2024-04-16 01:08:03

赞

踩

vivado怎么打代码

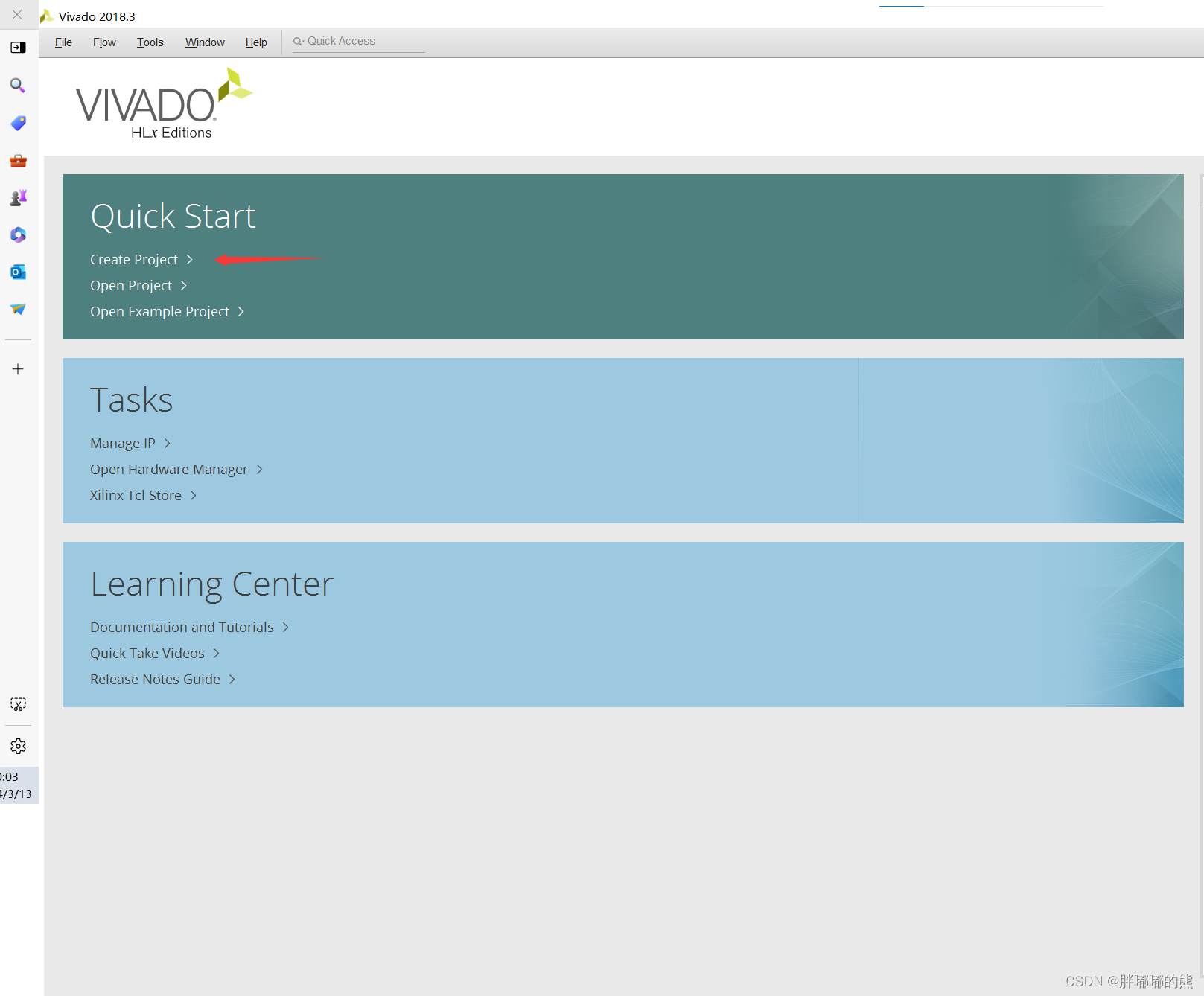

1.打开Vivado软件

2.创建工程项目

1.选择create Project

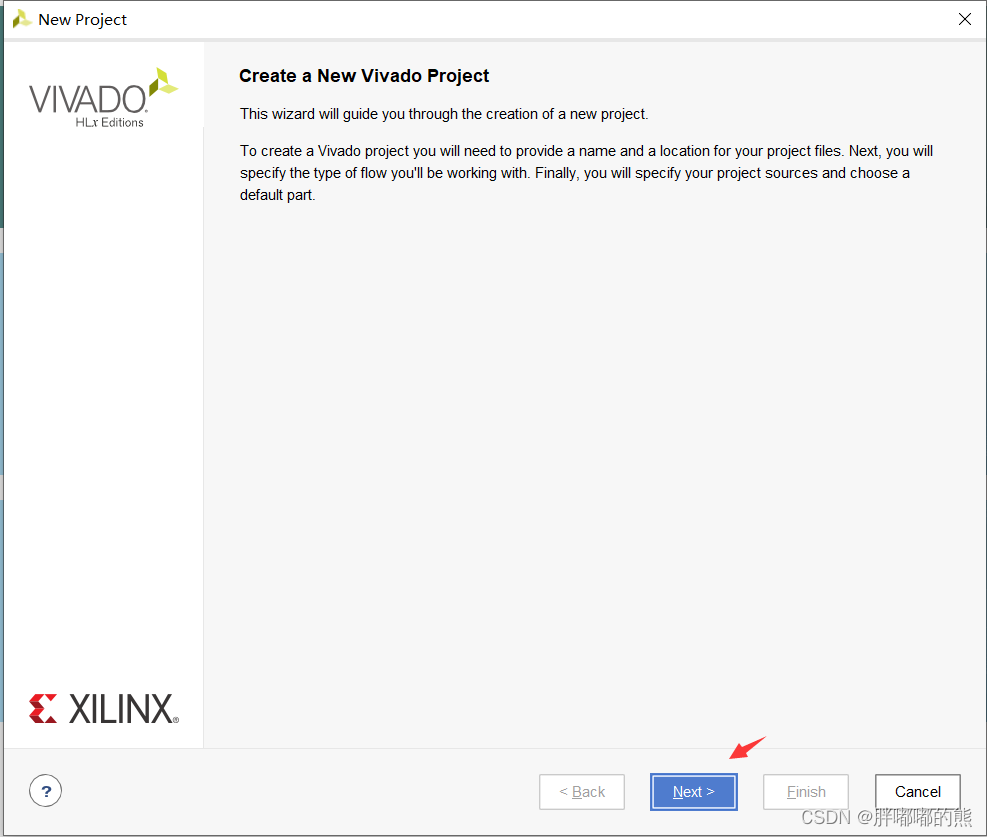

2.点击Next

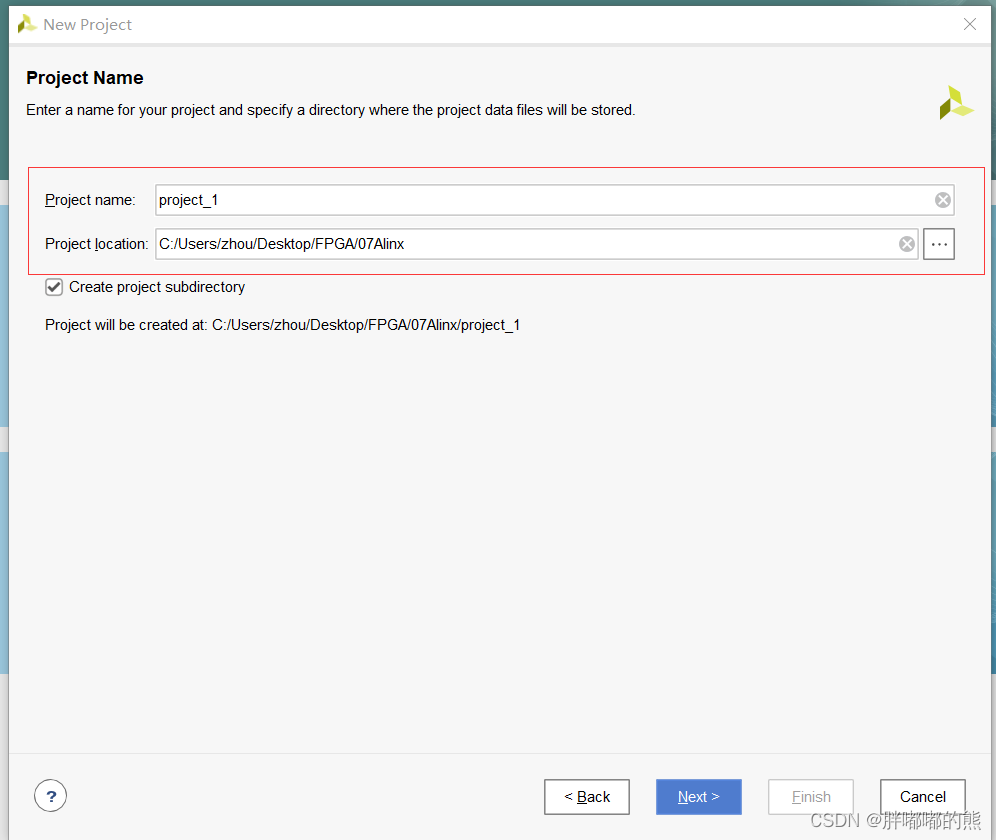

3.设置工程文件名称和文件保存路径设置

这里推荐文件保存在其他盘,尽量减少C盘占用率

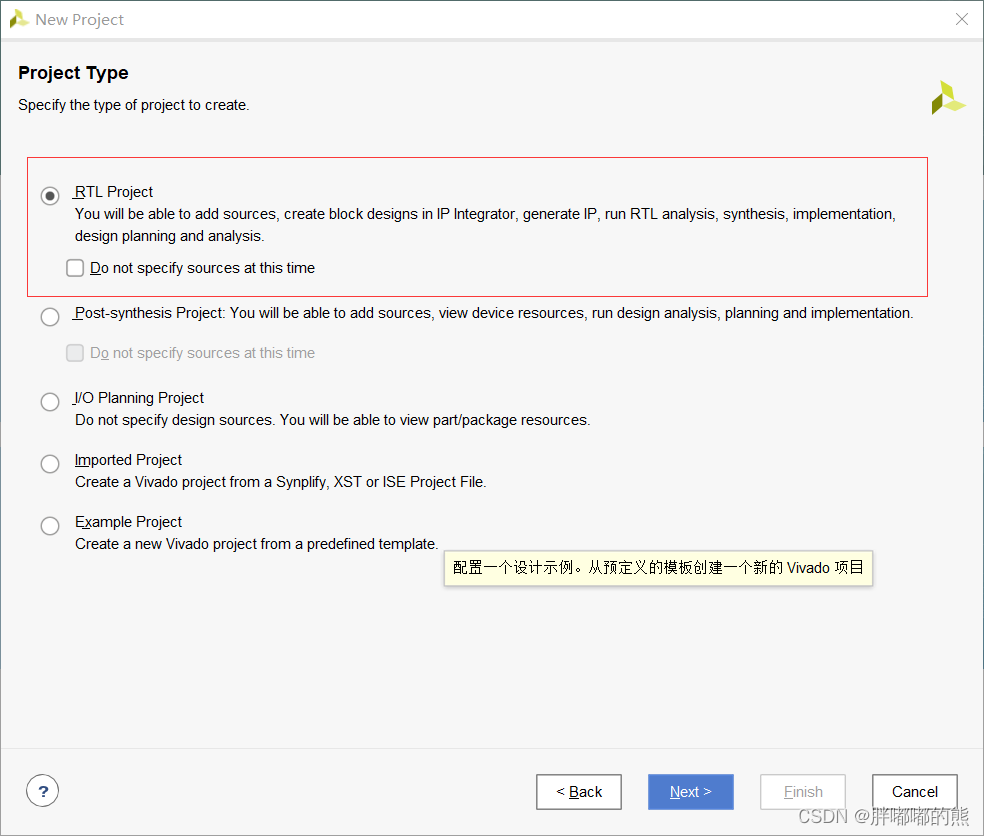

4.文件类型选择

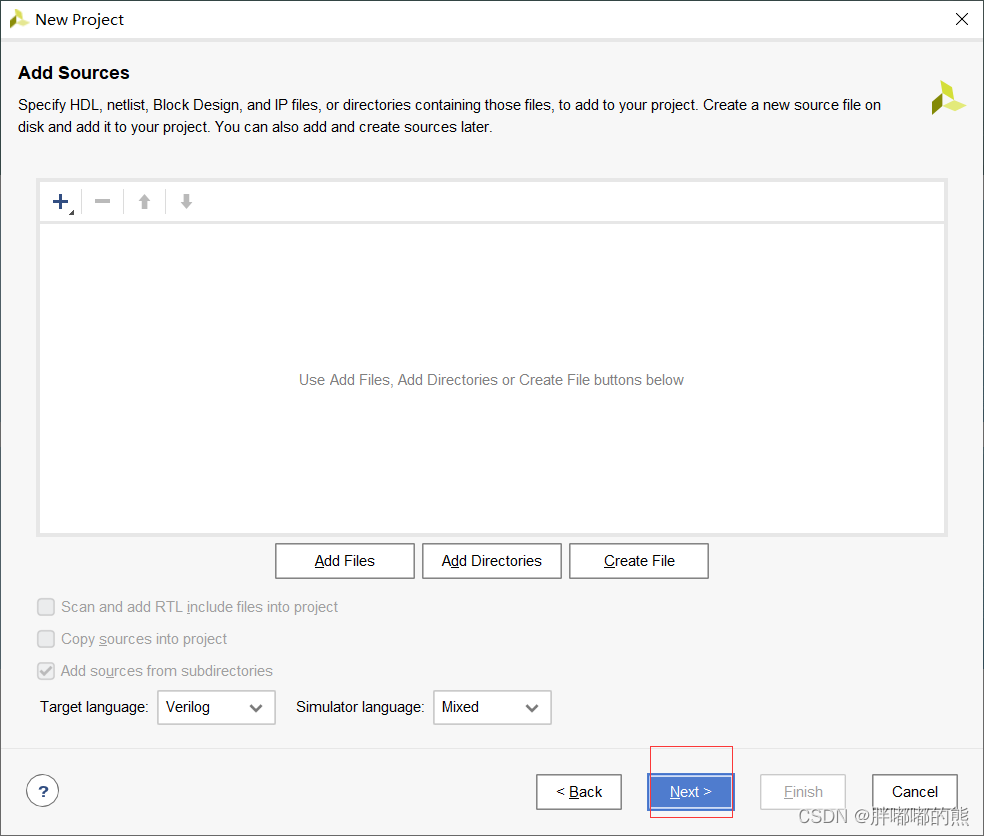

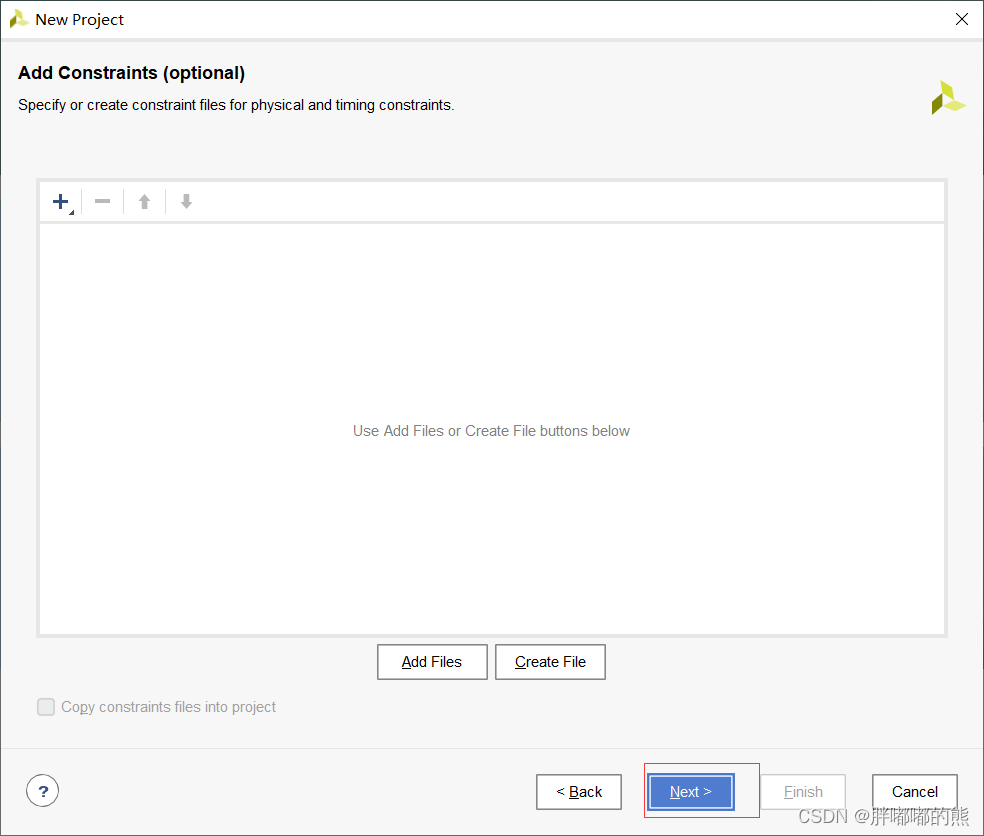

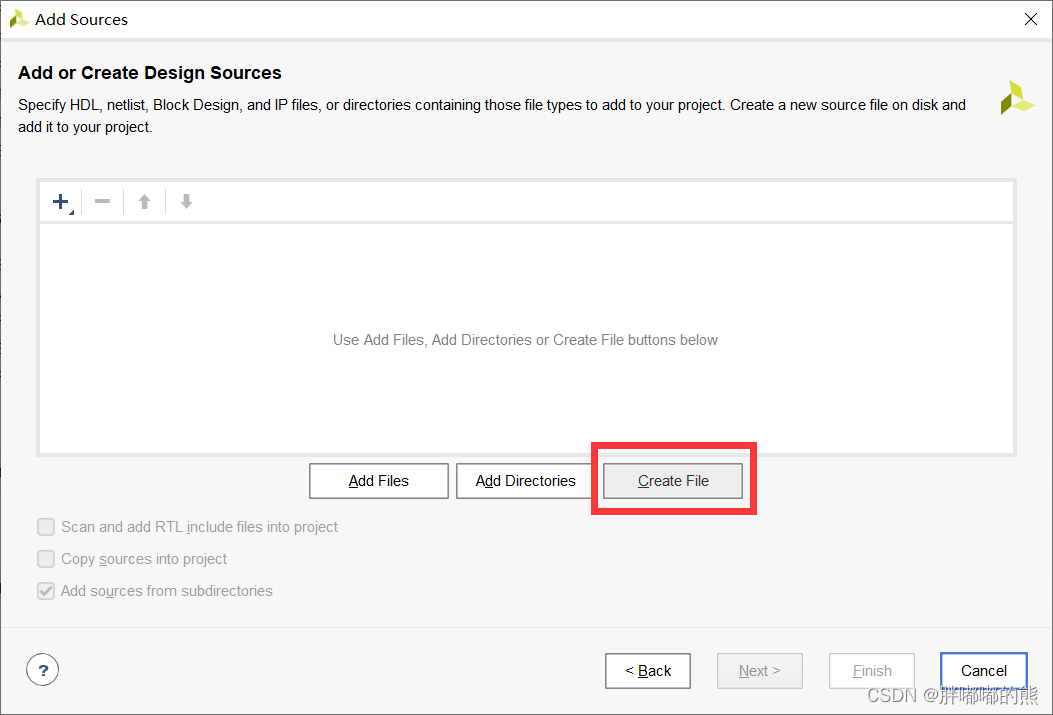

5.添加文件

这里选择暂时不添加文件,选择NEXT

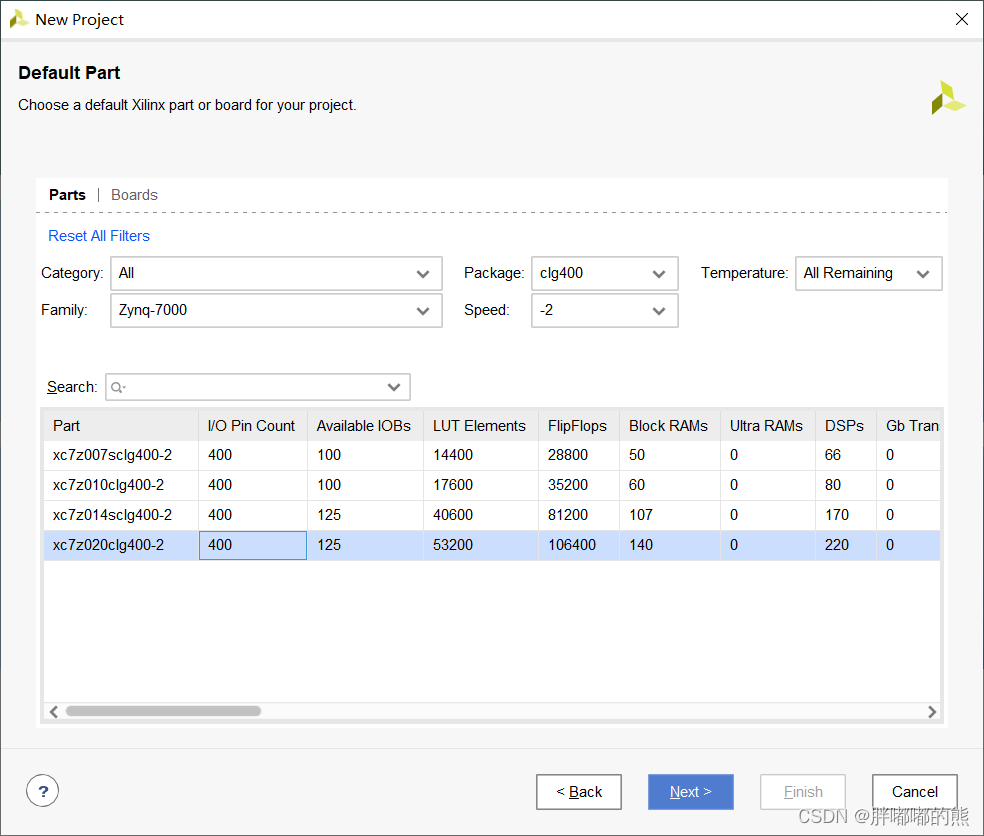

6.根据开发板型号选择相应配置

1. 这里以黑金Alinx ZYNQ7020为例

2. 选择Next

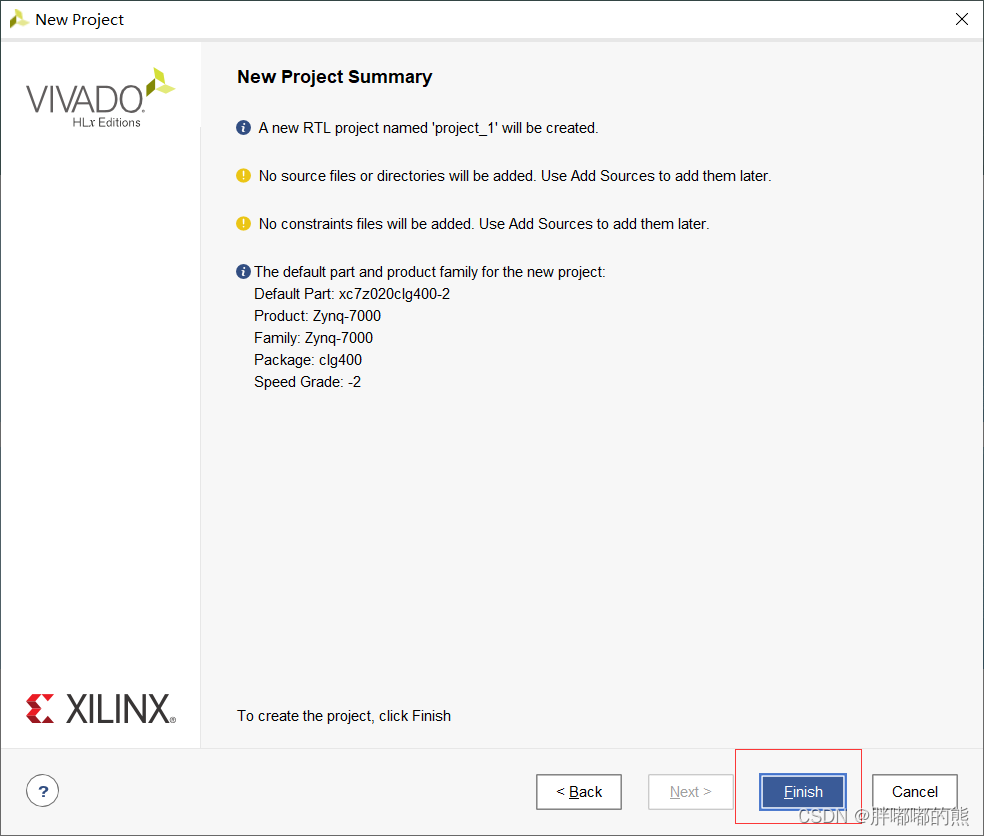

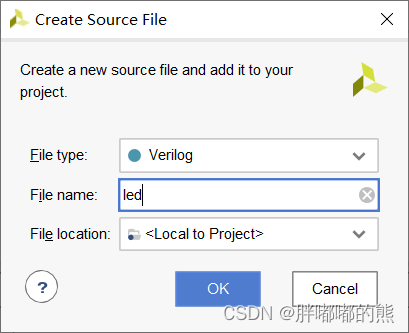

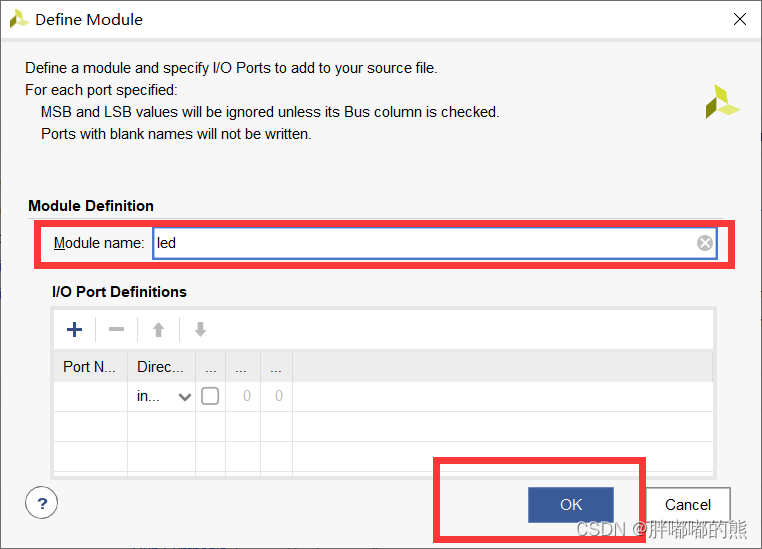

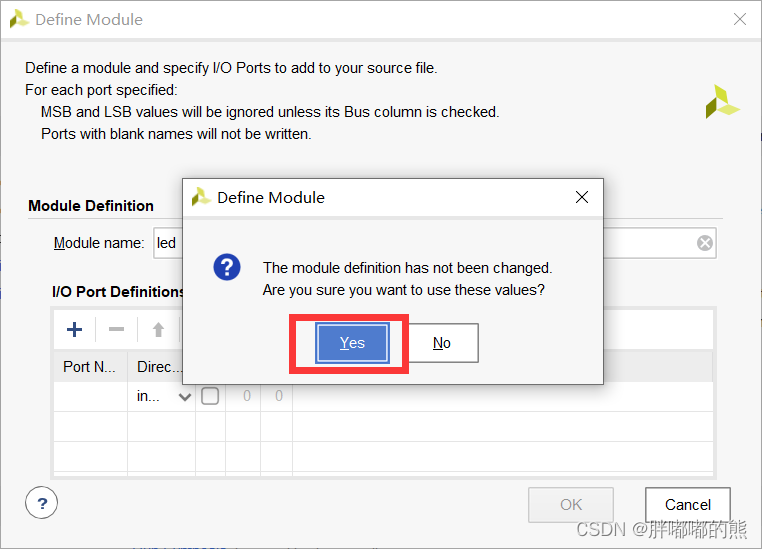

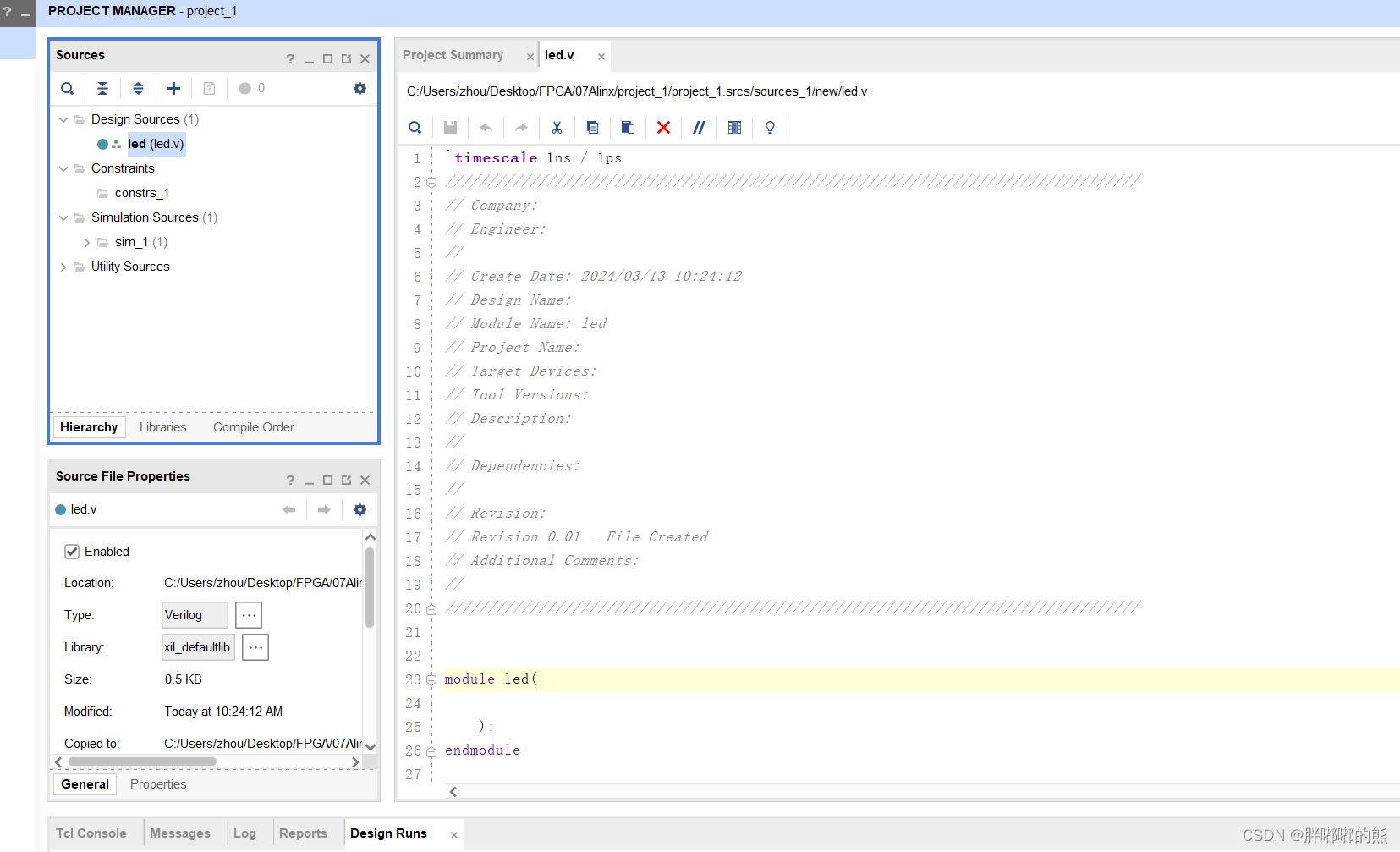

3.创建源文件

至此就创建完成啦!!! 第一次写博客,不是很熟悉,哈哈哈!!

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/431444

推荐阅读

相关标签