- 1【ES】springboot集成ES

- 2postman返回值乱码_postman 返回结果乱码

- 3代码随想录算法训练营第五十七天|647. 回文子串、516.最长回文子序列

- 4PHP+MySQL数据库编程的步骤_php和mysql自动编程

- 5【Tools】Navicat Premium12安装教程_navicat premiun12下载安装

- 6【路径规划】基于改进人工势场实现机器人路径规划附matlab代码

- 7【转】中国青年政治学院公开课:批判性思维 笔记

- 8效率软件:微软远程桌面安卓版_微软远程桌面链接apk csdn

- 9蓝桥杯java技巧总结_蓝桥杯复习java组

- 104万字,阿里云《大型体育赛事云上实战精选》电子书发布!_阿里云盘体育课件

手把手教你学会 Xilinx PCIE/XDMA 读写DDR系列(一) DDR/MIG配置详细步骤_xdma ddr

赞

踩

因最近想通过PCIE把数据从FPGA传到PC,借此机会和大家一起学习XDMA读写DDR

制作不易,记得三连哦,给我动力,持续更新!!!

完整工程文件下载:XDMA读写DDR工程 提取码:4sxh

----------------------------------------------------------------------------------------

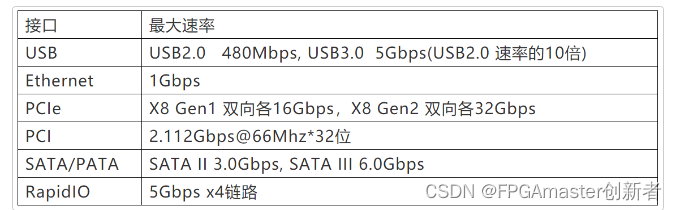

在实现FPGA和处理器、PC、ARM打交道的时候,有很多种方式进行通信,具体有以下几种实现方式:

由上图可以看的出来,PCIE的优势远远大于其他的通信方式,并且通信速度也是最快的一种,最高可以达到128Gbps。

Xilinx从15年前,V4系列开始,一直在PCIe的解决方案上深耕,提供众多的应用方案级的解决方案,方便用户专注于自己的应用。早期,Xilinx提供的有Application Notes,例如XAPP859,XAPP1052等,构建了基本的双向数据传输。当时一些第三方公司,类似于PLDA,NwLogic也出针对Xilinx FPGA的PCIe传输方案。

后来,Xilinx团队2017年附近推出XDMA解决方案,并持续增加功能、修正Bug,到目前为止,XDMA已经成为一个功能强大、成熟稳定的Xilinx FPGA解决方案。功能上涵盖了SG功能,AXI-Lite功能,多通道分离,AXI-MM和AXI-Stream支持等。稳定性上,经过4年的逐步完善,目前已经有众多的客户基于这套方案实现产品,涵盖医疗、电力、通讯、数据中心等各种应用。

最重要的是,XDMA是免费的!!

多余的废话我也不多说了,我知道大家最想看的是如何实现这种通信方式,直接上干货,手把手教大家实现PCIE/XDMA 读取DDR:

一、DDR/MIG配置详细步骤

首先本节先给大家介绍DDR/MIG的配置步骤

1、硬件设备

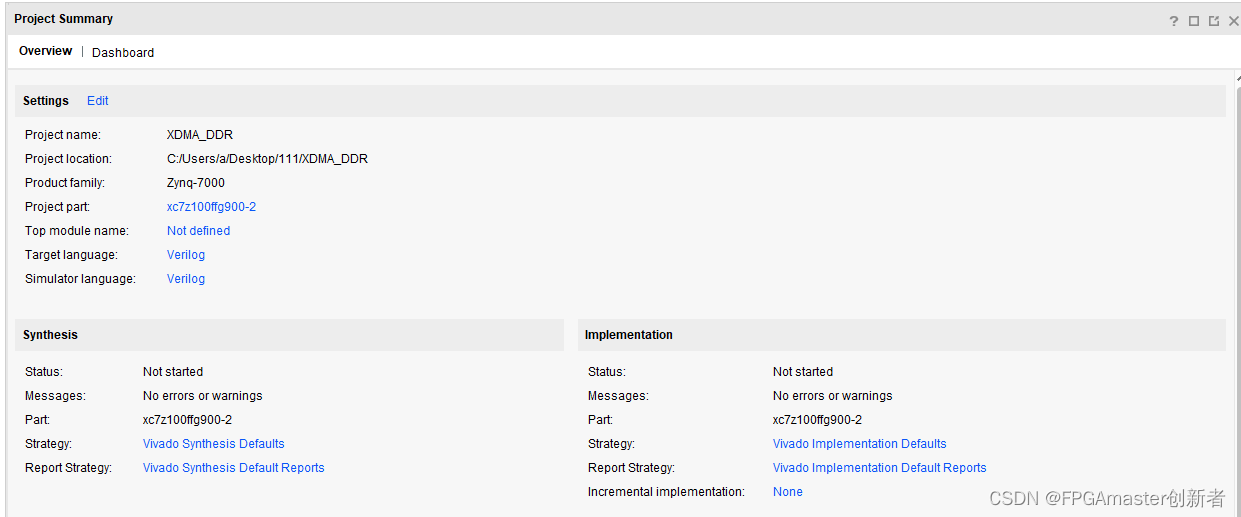

本次设计我采用的是Xilinx家的zynq100芯片:xc7z100ffg900-2,本次设计只用到PL部分,所以支持PCIE的FPGA开发板也可以按照我的步骤进行实现,vivado版本为vivado2018.3

首先基于你的芯片,建立一个工程

2、建立工程

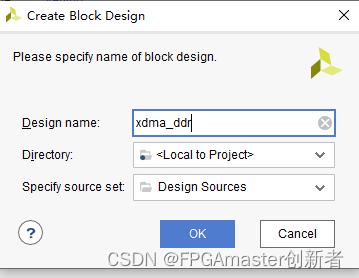

本次设计采用BD块进行设计,设计起来更加方便

1、在第一步的基础上,建立一个BD块

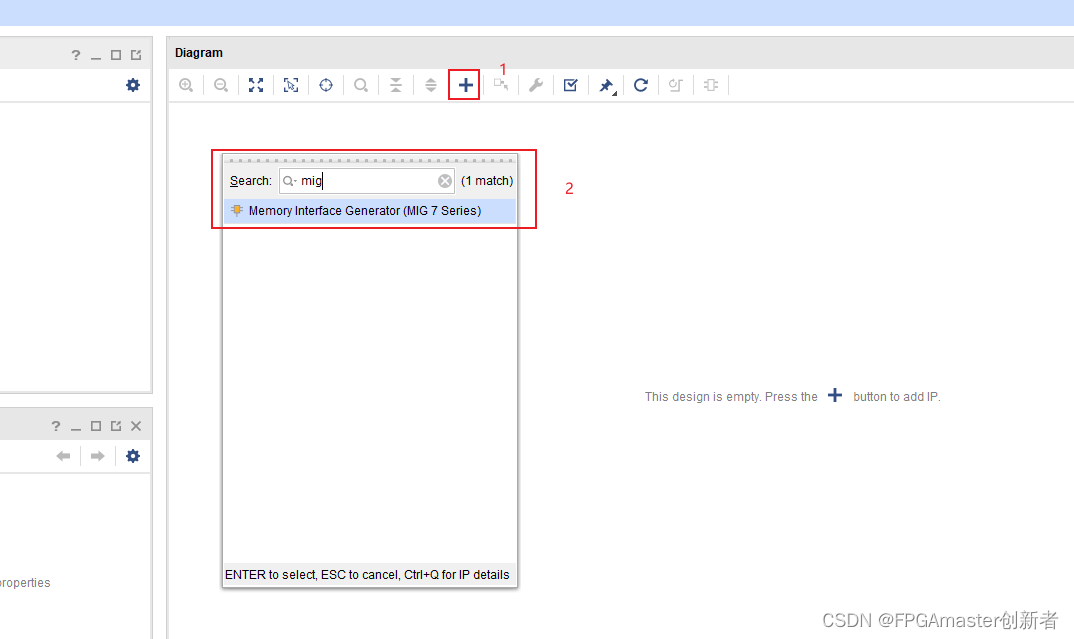

2、并添加MIG这个IP到设计中:

3、配置MIG

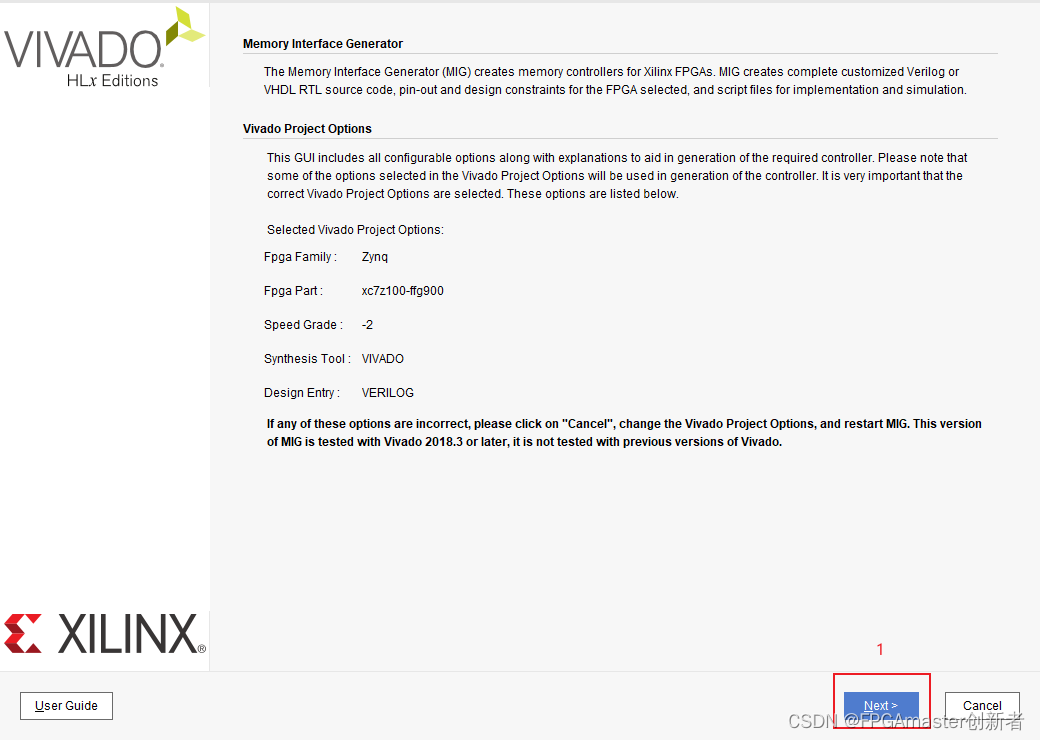

1、双击MIG这个ip:

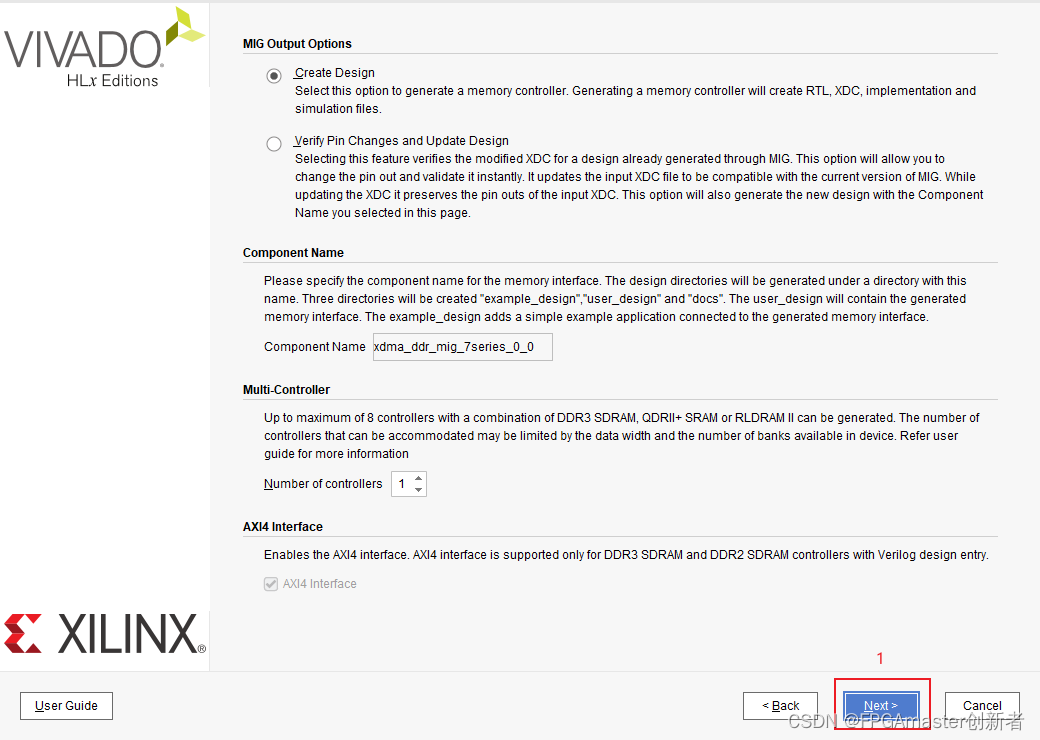

2、创建一个新的设计,选择AXI4接口

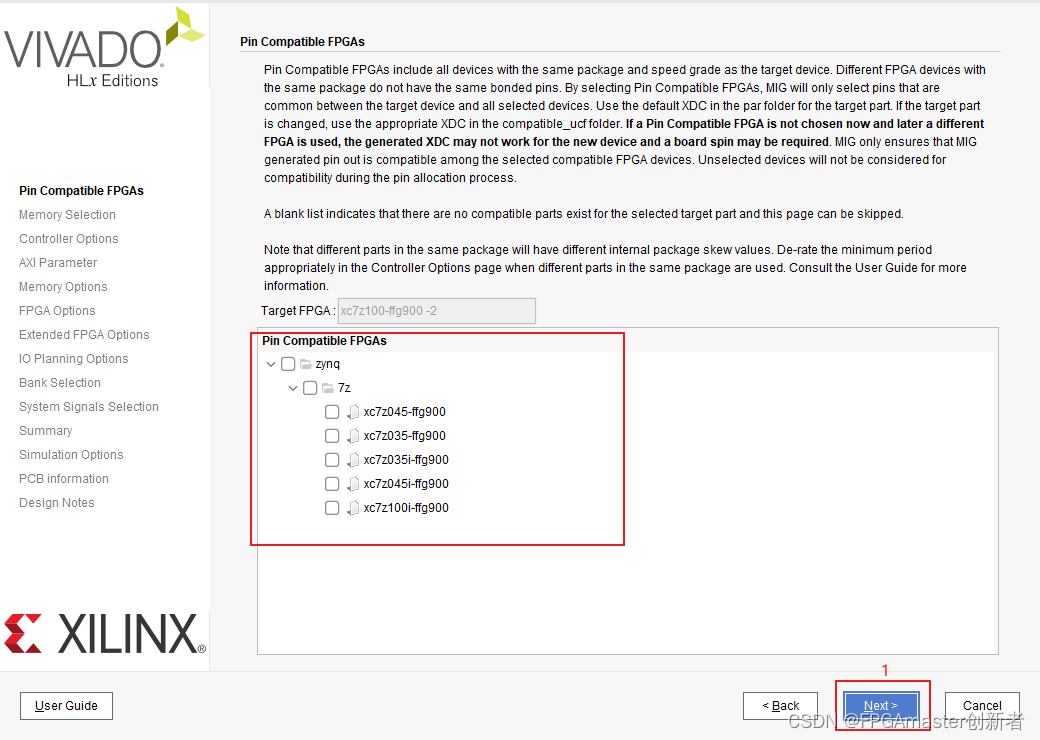

3、选择兼顾其他的FPGA型号,这里选择不兼容

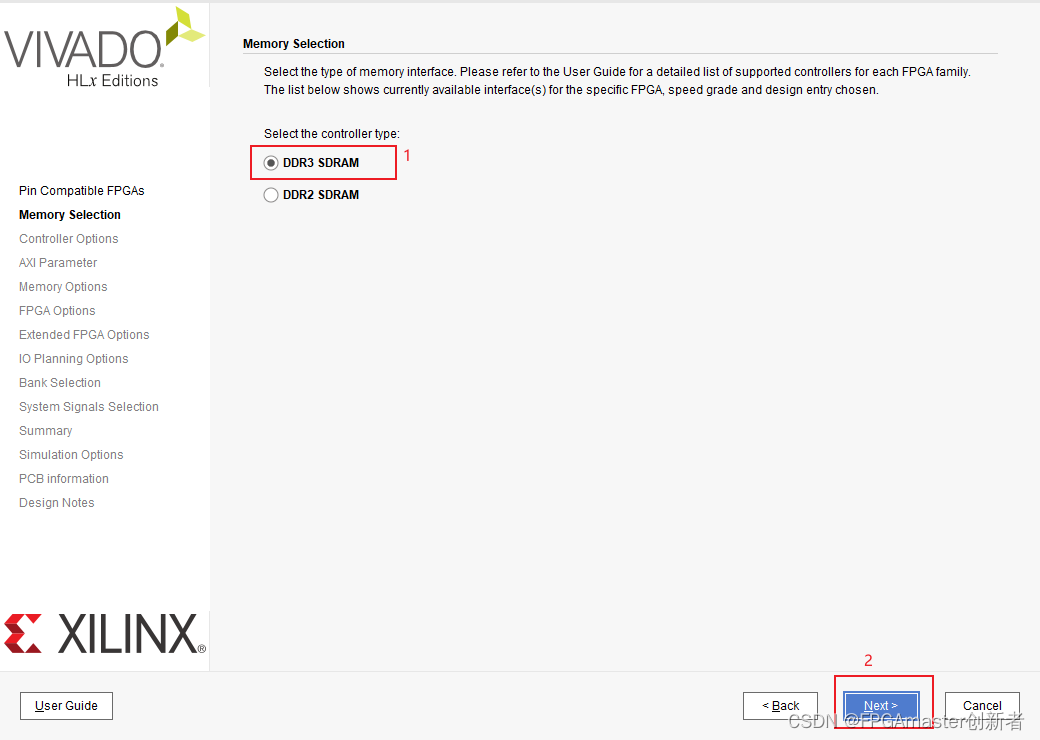

4、选择DDR3:

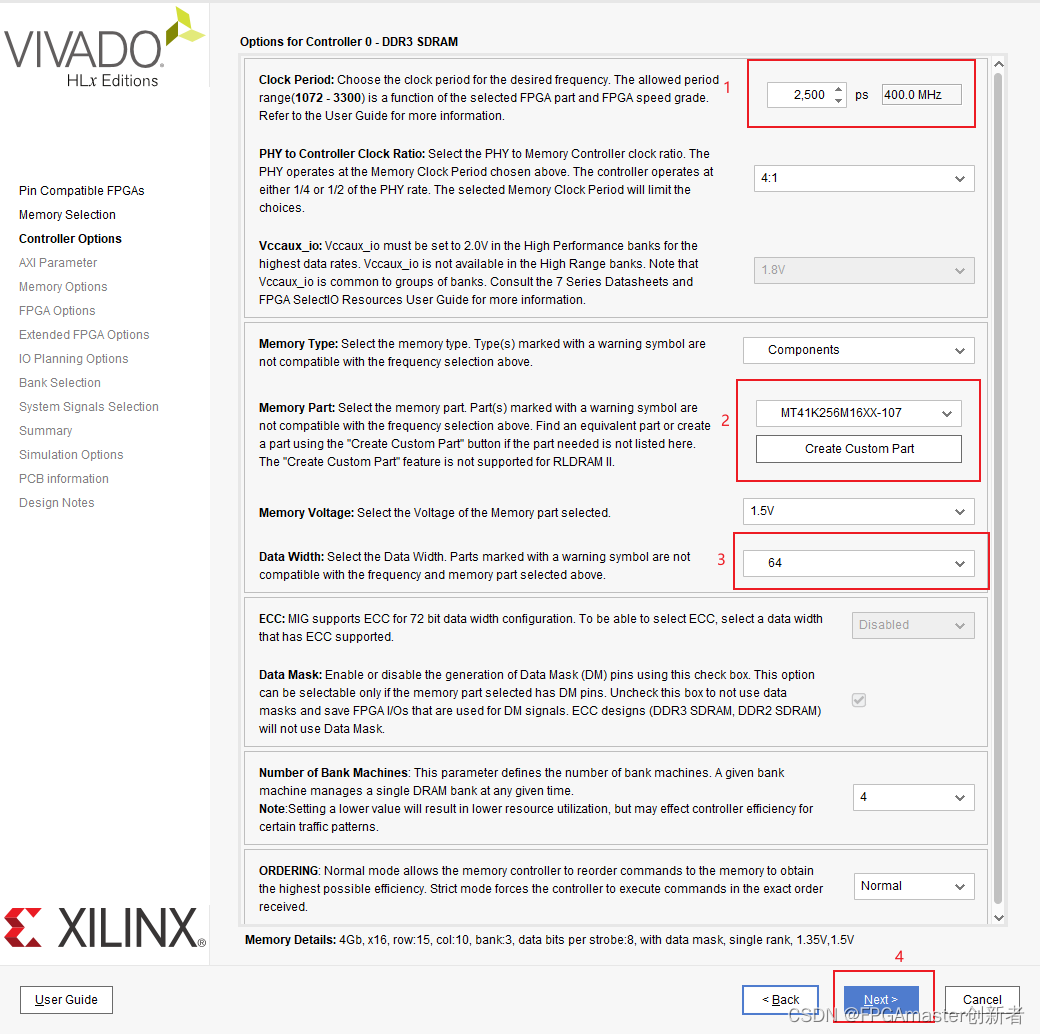

5、时钟配置、DDR选型:

| 端口名称 | 说明 | 值 |

| Clock Period | IP的主时钟频率,由MIG内部PLL生成 | 400MHz |

| PHY to Controller Clock Ratio | 物理侧到控制器时钟的比例 400M / 4 = 100M 这个100M为MIG IP 输出的ui_clk | 4:1 |

| Memory Type | 存储设备类型 | Components |

| Memory Part | DDR型号 | MT41K256M16-107 |

| Data Width | 数据位宽(取决于有几片DDR,和M*判断) 例如:板子有4片MT41K256M16的DDR 16 * 4 = 64 也可以根据你的DDR引脚分配中的dq来看 | 64 |

6、DDR内部的选项:

Data Width:此时这个为MIG IP的读写位宽,这个如果和前面保持一致,肯定没问题,但是也可以提高一点(提高后性能更快),但是也不能太高,太高可能会出现问题。(这个DATA Width是你的IP例化的时候的端口位宽)

不和前面位宽一致,并不会影响DDR读写数据,因为前面的interconnect IP 会把位宽转化为MIG IP的位宽

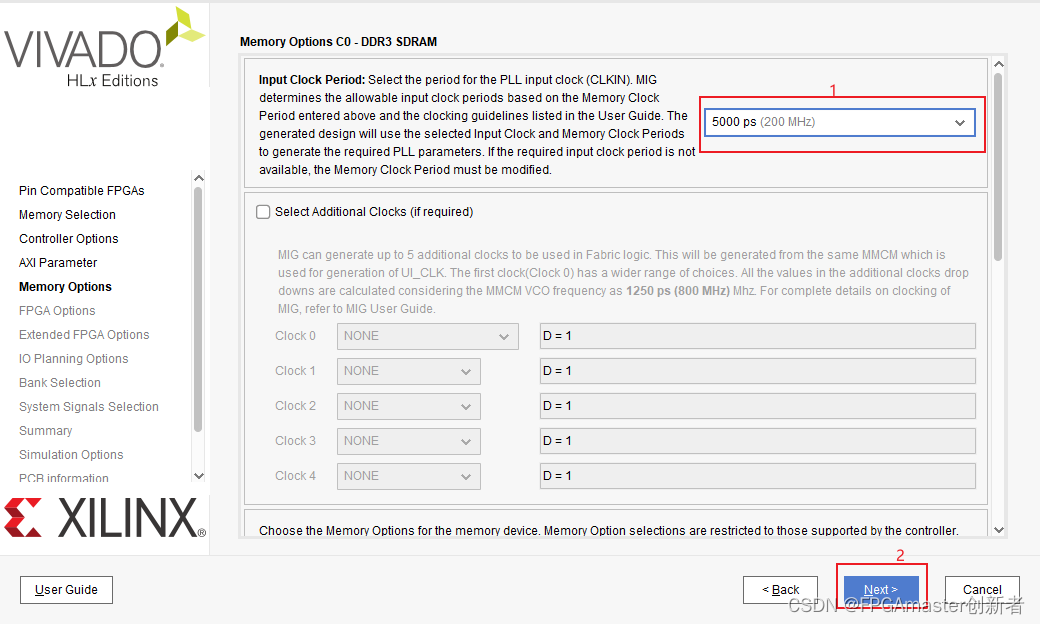

7、系统时钟:

选择你开发板给DDR的时钟,我的板子给的是200M,其余保持默认

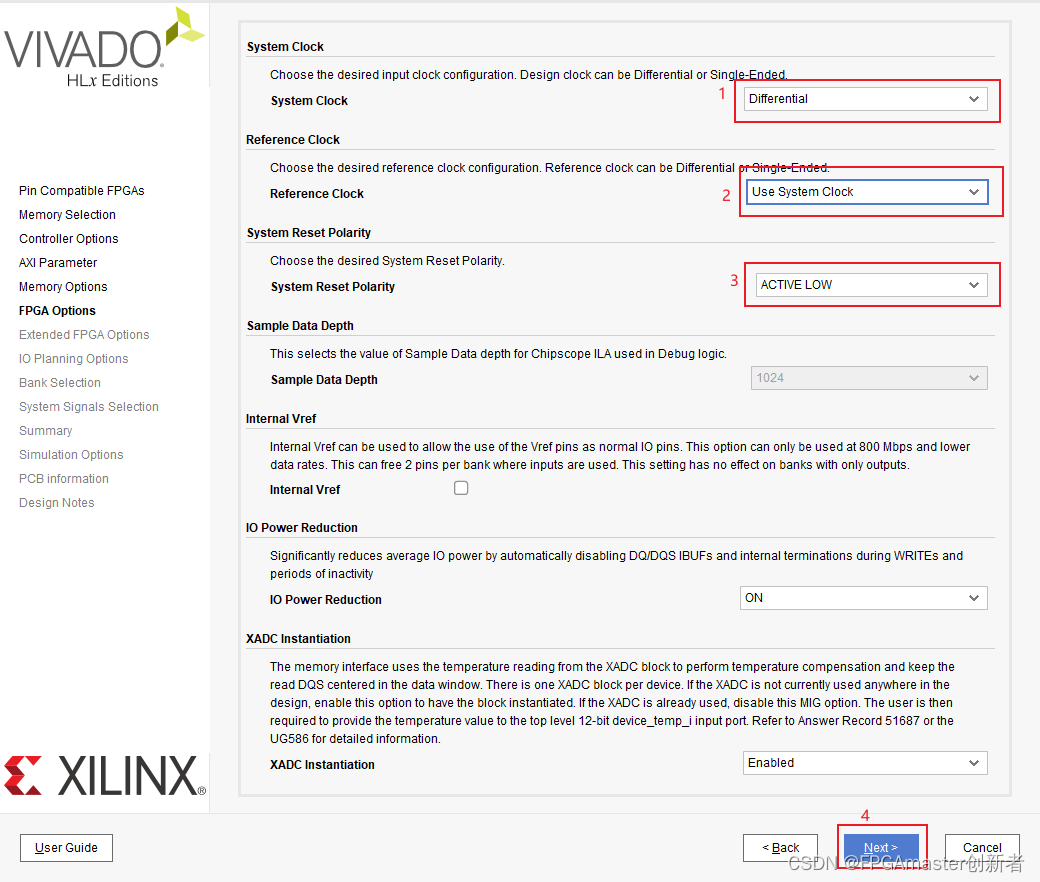

8、参考时钟、复位类型:

1、System Clock:输入时钟类型,根据板子自身选择,我这里选择查分类型

2、Reference Clock:参考时钟类型,跟随系统时钟

3、System Reset Polarity :系统复位类型,选择低电平复位

4、NEXT

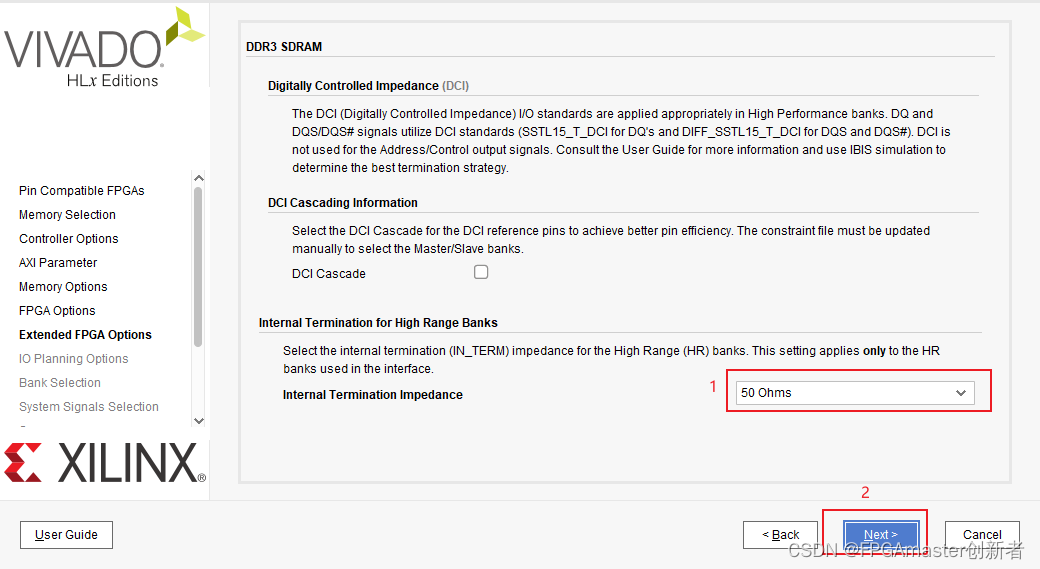

9、电气属性:

根据自己的硬件选择,此次设计保持默认50Ohms

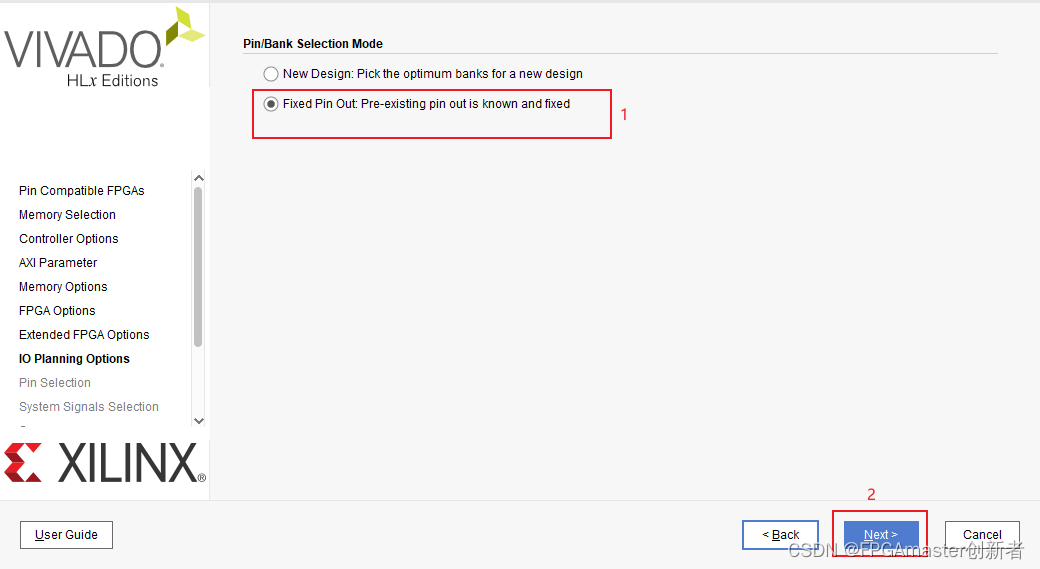

10、管脚分配模式:

选择第二个,可以导入.ucf文件

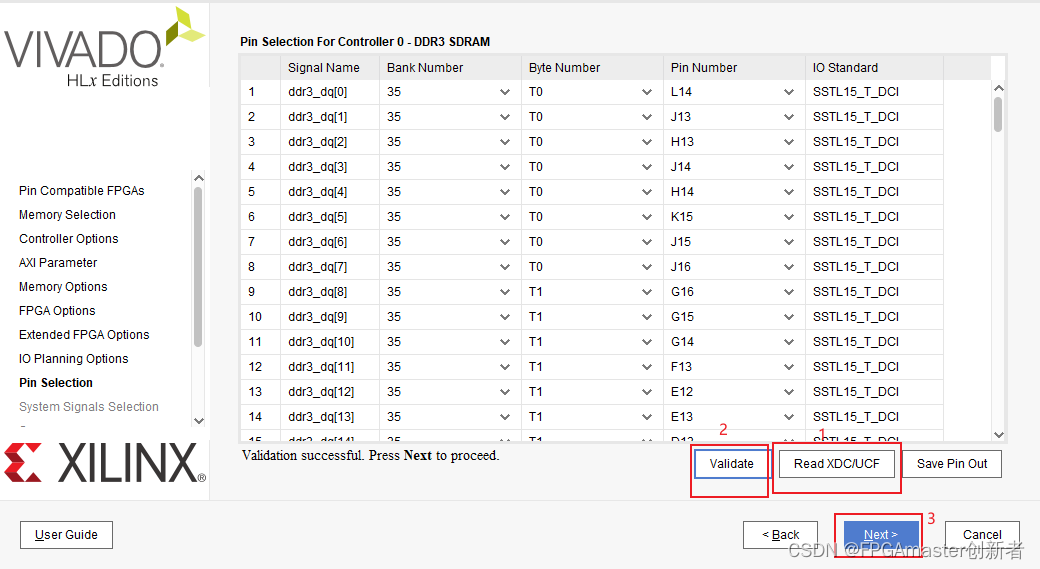

11、导入.ucf文件:

1、首先读取.ucf文件

2、然后需要验证这个文件,才可以点击next

3、NEXT

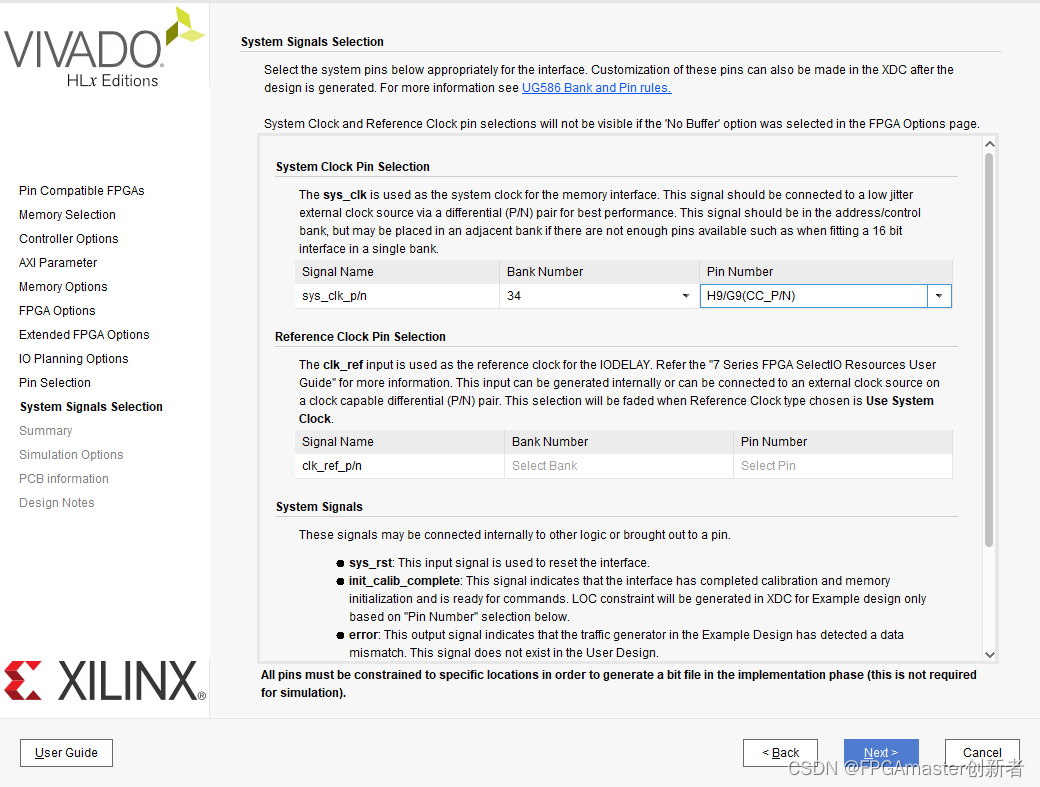

12、时钟、复位管脚分配:

可以直接在这里分配DDR的约束,如果在这里勾选过了,在xdc文件就不需要约束了

我这边选择一下我的DDR时钟引脚(根据原理图选择自己的)

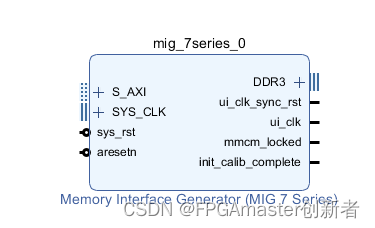

13、然后就是一路next,这样MIG的ip就已经配置完了

完整工程文件下载:XDMA读写DDR工程 提取码:4sxh

下一节讲解 XDMA这个IP的配置,并连接这两个IP

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!