热门标签

热门文章

- 1探秘便携式软件无线电:PortaPack-HackRF

- 2机器学习入门(11)——聚类(Clustering)_聚类中心

- 3c++入门学习⑨——STL(万字总结,超级超级详细版)看完这一篇就够了!!!

- 4使用变更数据捕获方法通过提取-转换-加载过程实时更新数据仓库_数据捕捉提取转换加载

- 5聊聊Nodejs中的核心模块:stream流模块(看看如何使用)_nodejs stream

- 6图神经网络(二十七)GeniePath: Graph Neural Networks with Adaptive Receptive Paths_graph neural networks with adaptive readouts

- 7Android Studio 中创建Flutter Project及环境配置(Mac环境)_mac android studio 创建flutter 工程 不能选择运行平台

- 8Scrapy入门、当当网商品爬取实战_dangdang.promotion.get

- 9python中的哈希_Python中hash的问题

- 10Python + requests实现接口自动化框架!_python requests 接口自动化_requests.reques接口自动化

当前位置: article > 正文

FPGA_Verilog学习之旅(4)---基于SPI读取AD7606_ad7606 spi

作者:盐析白兔 | 2024-07-15 12:47:24

赞

踩

ad7606 spi

最近要做的项目用到了AD7606,其实可以直接用并行接口,不过由于某些原因只能用SPI去读取AD7606(因为占用引脚少!!!)。本来想偷点懒直接网上CV一个FPGA SPI读取AD7606的,但是去网上找了半天,发现全都是用FPGA并行读取AD7606,无奈自己只能再花半天时间对着时序图写一个(不过这次写的代码倒是令我感到挺意外的,代码从开始写到编译到配置,连个语法错误都没出现,一遍过)。

下面就简单把数据手册上用到的重要引脚和串行读取的时序图贴一下,另附代码下载链接:

1. AD7606 SPI读取时,一些重要的引脚

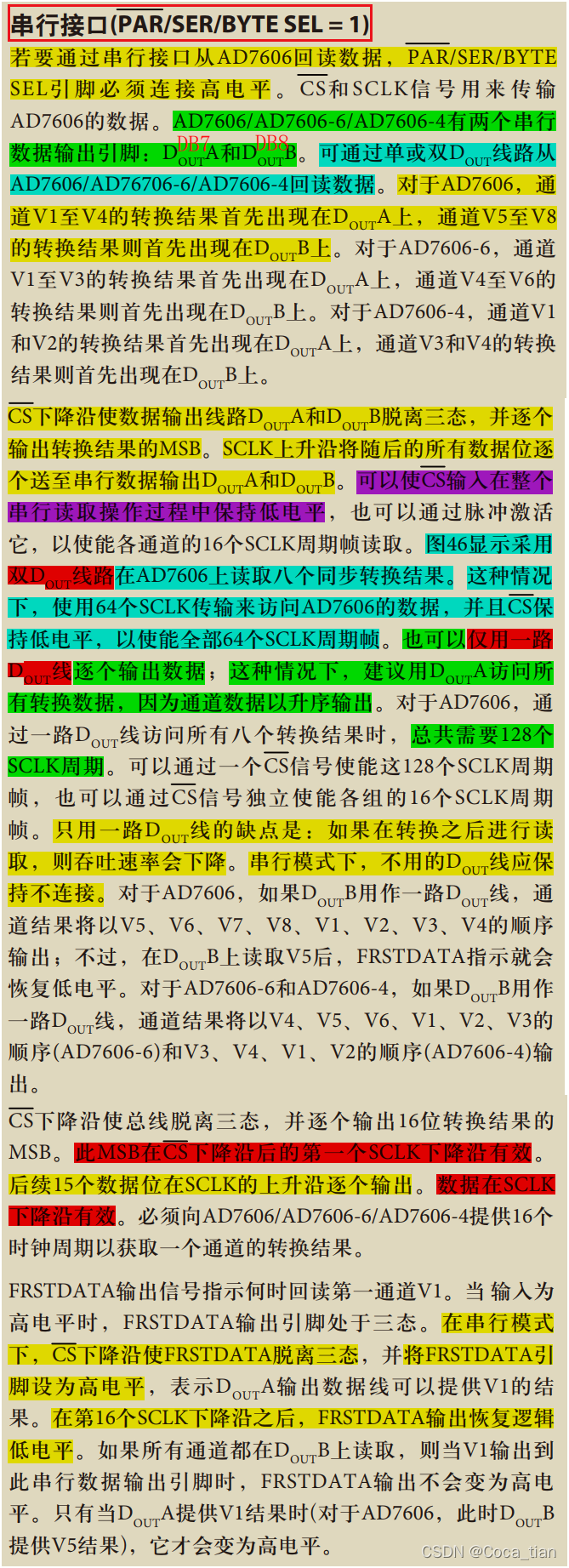

2. AD7606 SPI读取时的一些时序

3. AD7606 SPI读取时的一些说明

使用串行SPI输出时,可以选择是双Dout(DB7和DB8共同输出)还是只用一路Dout(DB7或DB8选择一个进行输出)输出,这里我们使用双Dout线路输出。

4. AD7606 SPI代码(Verilog)

- 将CONVST A 和 CONVST B 两个引脚并联在一起接到 FPGA 引脚,8个采样通道全用上

- 不使用过采样

- 输出采用 DB7 + DB8 的双Dout线路输出数据

完整代码下载链接:AD7606_spi_drive

或 https://download.csdn.net/download/hxt691083776/56800543

另附并行读取AD7606的代码:AD7606_parallel

或 https://download.csdn.net/download/hxt691083776/56815566

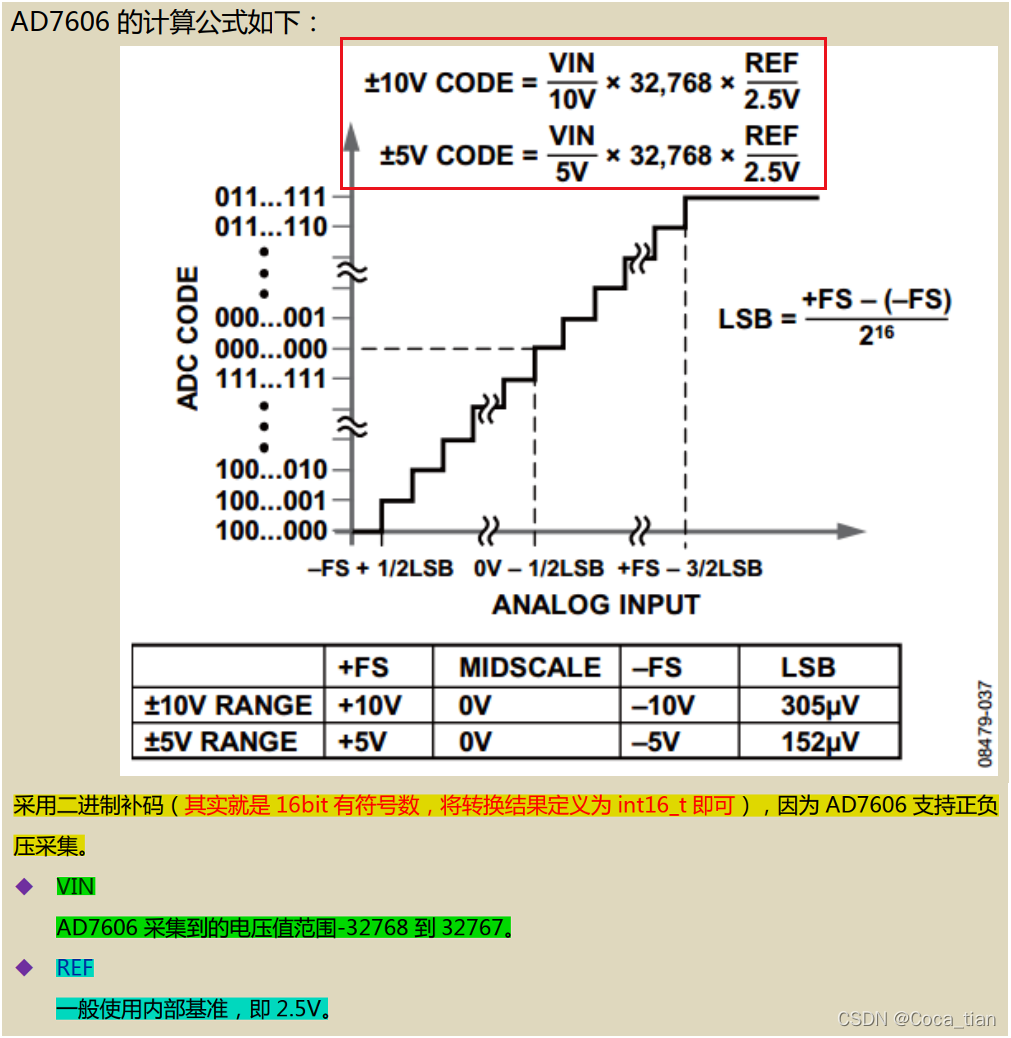

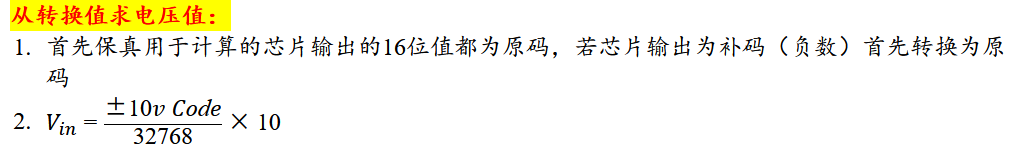

5. AD7606 输出电压计算公式

6. 上板验证

给AD7606的通道8接了一块1.6V的干电池,按照输出电压计算公式,应输出:(1.6/10)*32768=5242,实际测出为5268,基本一致,验证成功。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/盐析白兔/article/detail/829414

推荐阅读

相关标签