- 1jmeter-性能测试场景_.jmeter做性能测试设置场景是怎么做的(性能)

- 2设置、查看或修改Git的用户名和邮箱_ubuntu查看git用户名

- 3使用dblink同步本地数据库新增记录到远程服务器_有clob字段的表 远程视图

- 4Flink 实现端到端的exactly-once_flink通过()实现端到端exactly-once

- 5情感分析系列(四)——使用BERT进行情感分析_bert情感分析csdn

- 6批量下降法与随机下降法在自然语言处理中的应用

- 7鸿蒙开发实战-手写文心一言AI对话APP_鸿蒙no signature file

- 8ZYNQ入门

- 9Docker - Windows 11 下 Docker Desktop 的 下载 安装 配置 使用_dockerdesktop

- 10手机照片备份方案Immich

秋招 FPGA工程师 面试题最全总结_fpga工程师反问

赞

踩

FPGA面试题

1、FPGA的基本组成单元

可编程输入输出单元(IOB);基本可编程逻辑单元(CLB);完整的时钟管理模块;内嵌的底层功能单元和嵌入式专用硬核;可编程连线资源;嵌入式BRAM

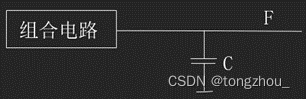

2、组合逻辑、时序逻辑

组合逻辑:任意时刻的输出仅仅取决于该时刻的输入,与电路原本的状态无关;

时序逻辑:任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关;仅当时钟沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

3、同步电路、异步电路

同步时序电路:各触发器的时钟端全部连接在一起,并接在系统的时钟端,只有当时钟脉冲到来时电路的状态才改变,改变后的状态会一直保持到下一个时钟脉冲的触发沿到来

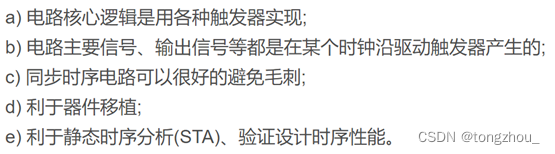

特点:

异步时序电路:电路没有统一的时钟,电路中除了可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件。电路状态的改变是由外部输入变化直接引起的

特点:

4、同步设计的好处

- 同步设计能有效避免毛刺的影响,使得设计更加可靠。

毛刺是逻辑设计的天敌,毛刺使得数据变得混乱,可能引起电路功能的误判断。当毛刺引入于时钟端或者异步复位端,就极有可能引起触发器的误翻转或者出现不正常的复位。但是毛刺是与生俱来的,也就是说毛刺是不可避免的,一般来讲凡是有组合逻辑的地方肯定就有毛刺。同步设计是避免毛刺的最简单有效的方法。

- 同步设计可以减少环境对芯片的影响

由于芯片的实际工作环境比我们在测试的实验室环境恶劣的多,加之长时间运行,随着芯片的温度的升高,电压的不稳定,将会使得器件内部时延发送变化,如果不使用同步设计的话,对于时序要求比较苛刻的电路将无法正常工作。因为只有满足芯片的Static timing的要求,才能保证芯片在预知的过程中工作。

- 同步设计可借助与STA工具进行时序分析,有助于提高设计的可靠性。

- 同步电路比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状。

- 同步电路可以很容易地组织流水线,提高芯片的运行速度,设计容易实现。

5、时钟抖动、时钟偏移

时钟抖动jitter:指时钟信号的跳变沿不确定,故是时钟频率上的不一致,时钟周期在不同的周期上可能加长或缩短。

时钟偏移Skew:指全局时钟产生的各个子时钟信号到达不同触发器的时间点不同,是时钟相位的不一致。

产生原因:

jitter主要受外界干扰引起,通过各种抗干扰手段可以避免。

skew由数字电路内部各路径布局布线长度和负载不同导致,利用全局时钟网络可尽量将其消除。

6、同步复位、异步复位、异步复位同步释放

同步复位:在时钟有效沿到来之后有效。

优点:抗干扰能力强,有效消除高于时钟频率的复位毛刺,同时也有利于时序分析

缺点:对于Altera的FPGA,其触发器只有异步复位端口,使用同步复位会增加逻辑资源消耗,同时插入组合逻辑,也会增加相应的组合逻辑门延时;同步复位依赖时钟,并且复位信号时间不能小于一个时钟周期,有可能错过时钟有效沿而不能复位。

异步复位:只要复位信号有效就能完成复位,

优点:无需增加逻辑消耗,复位简单

缺点:容易受到复位毛刺的干扰,造成虚假复位;属于异步逻辑,如果复位释放在时钟有效附近,容易使触发器进入亚稳态,可能导致逻辑错误;不利于时序分析

总结:对于Xilinx的FPGA,高电平复位,其触发器同时支持同步/异步复位,复位准则:

- 尽量少使用复位,特别是少用全局复位,能不用复位就不用,一定要用复位的使用局部复位;

- 如果必须要复位,在同步和异步复位上尽量使用同步复位,一定要用异步复位的地方采用“异步复位,同步释放”

- 复位电平选择高电平复位

对于Altera的FPGA,低电平复位,其触发器只有异步复位端口,所以如果想用同步复位,需要额外的资源实现。使用异步复位可以节省资源。

异步复位同步释放优势:经过异步复位同步释放(在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步)处理后,相比与纯粹的异步复位,降低了异步复位信号释放导致亚稳态的可能性;相比同步复位,能检测到同步复位中检测不到的复位信号。

D触发器搭建电路:使用两个带异步复位的触发器,D端输入逻辑1(VCC)。当异步复位无效(rst_async_n = 1)时,同步后的复位信号 rst_sync_n 也为 1;当异步复位有效(rst_async_n = 0)时,同步后的复位信号 rst_sync_n 立刻为 0,即实现了“异步复位”,但是会在时钟上升沿来临时恢复为 1,实现“同步释放”;

Verilog代码实现:

reg rst_n_1 = 1'b1;

reg rst_n_2 = 1'b1;

always @ (posedge clk or negedge rst_async_n) begin

if( !rst_async_n ) begin

rst_n_1 <= 1'b0;

rst_n_2 <= 1'b0;end

else begin

rst_n_1 <= 1'b1;

rst_n_2 <= rst_n_1;end end

assign rst_sync_n = rst_n_2;

7、竞争、冒险、消除竞争冒险

竞争:在一个组合电路中,一个输入变量经过几条路径到达输出端,由于每条路径的延时不同,到达输出端的时间就会有先后,这种现象为竞争;

冒险:在具有竞争现象的组合逻辑中,当某个变量发生变化时,比如从0跳到1或者从1跳到0,如果真值表所描述的逻辑关系或功能遭到短暂的破坏,在输出端出现一个不该有的尖脉冲,这种现象为冒险。(多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号)

消除:

(1)加入滤波电容(输出端并联一个电容),电容通高频阻低频,尖脉冲直接对地短路,从而消除了尖脉冲。(该方法只能用于对波形和延迟时间要求不严格的情况)

(2)引入选通信号:将输出门封锁,等到所有输入信号都变为稳态后再去掉封锁输出信号。

(3)更改逻辑设计,增加冗余项。

(4)保证同一时刻只允许单个输入变量发生变化,即可避免发生毛刺。比如对数据进行格雷码编码,即可解决这个问题。

组合逻辑电路出现的是竞争冒险问题;时序逻辑电路出现的是亚稳态问题

8、亚稳态、产生原因、消除方式

亚稳态:电路信号处于不确定的、不稳定的状态叫做亚稳态

产生原因:寄存器建立保持时间不满足引起亚稳态。

典型的场合:数据跨时钟域传输、异步复位电路。