热门标签

热门文章

- 1thinkphp5.0.23命令执行-靶场复现_thinkphp漏洞靶场

- 2使用Python获取公众号下所有的文章_python获取微信公众号文章内容的方法

- 3科锐国际(计算机类),快手,CVTE,得物,蓝禾,奇安信,顺丰,康冠科技,金证科技24春招内推

- 4一法通

- 5hadoop配置文件详解系列(一)-core-site.xml篇

- 6Spring cloud微服务搭建(一)——maven依赖_

org.springframework.cloud - 7MongoDB性能最佳实践:如何制定更有效的基准测试?

- 8QGIS:合并多个TIF_qgis 合并多个tif

- 9Kafka消息失败后无限重复消费现象的排查_kafka消费错误一直重试

- 10C++ 数字三角形(动态规划)_c++数字三角形

当前位置: article > 正文

检查zynq710核心板子的记录-3 (STEP6)_zynq 差分晶振

作者:笔触狂放9 | 2024-04-24 10:32:59

赞

踩

zynq 差分晶振

SETP6:检查一下UART_CLOCK.SCHDOC这个文件。

内有两路USB转串口芯片,无论原件还是是封装都是现成的,因此这部分比较有把握。

PS_UART部分接的PS的MIO必须严格对应,

我们用PS2PC来表示从PS为输出,PC也就电脑,是输入,则看到MIO48是PS2PC,同理可以MIO49是PC2PS。

经过确认没有问题。其实这里发现ZC706官方板子用的是CP2103这芯片,而咱们新的板子用的是CP2102,差别就在CP2103的IO可以通过VIO这个脚设置。我们用CP2102不得不加上一个电压转换芯片:

再次做新产品时候可以考虑使用上CP2103这个芯片。

检查PL UART 也没有问题。

LED接用CP2102输出的3.3V来驱动是经过验证无误的。

接下来看时钟部分:

其中33.333MHZ和100MHZ单端时钟用的是3528封装,并且供电电压是1.8V,实际上绝大多有源晶振是支持1.8V电压的。200M的差分有源晶振是5032封装的。

这里要确保一下晶振的PCB封装。

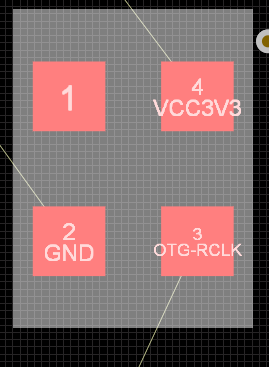

以上小的图是从ZEDBOARD的PCB里面拷贝的封装,下面就使我们板子的封装。可见引脚定义是一样的。其中4脚可以悬空或者接电源。

接下来看5032封装的有源差分晶振

从晶振的介绍网页里面确确认了一下封装定义无误。采购时候注意详细型号是SIT9102-231N-18E-200.00MHZ

之后查看时钟信号是否接在FPGA对应的引脚上。

此篇原理图检查完毕。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/478942

推荐阅读

相关标签