热门标签

热门文章

- 1DNS服务器显示两个地址,dns服务器地址出现两个

- 2大数据开发学习笔记_大数据应用开发课堂笔记

- 3机器学习-KNN算法(鸢尾花分类实战)_鸢尾花knn算法

- 4虚拟机上的ubuntu本地跟gitlab或gitee远程仓库建立连接_虚拟机设置绑定gitee

- 5Gary Marcus:因果熵理论的荒诞和认知科学带给AI的11个启示 | 文末赠书

- 6[NLP] PyTorch 实现双向LSTM 情感分析

- 7企业内网通过itms-services(https)协议安装IOS应用_itms ssl

- 8图解二叉树遍历方法-前序遍历、中序遍历、后序遍历_先序遍历中序遍历后序遍历图解

- 9OSPF的工作流程_ns3 ospf

- 10基于GitLab搭建DevSecOps流水线_gitlab devsecops

当前位置: article > 正文

基于FPGA的数字电子钟VHDL代码Quartus仿真_基于fpga的电子钟的调试及仿真

作者:笔触狂放9 | 2024-06-17 08:36:44

赞

踩

基于fpga的电子钟的调试及仿真

名称:基于FPGA的数字电子钟VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

1)设计一个能显示秒、分、时的24小时数字钟

2)用数码管显示出时,分,秒,复位显示00:00:00

3)通过按键可对时,分,秒进行设置

1. 工程文件

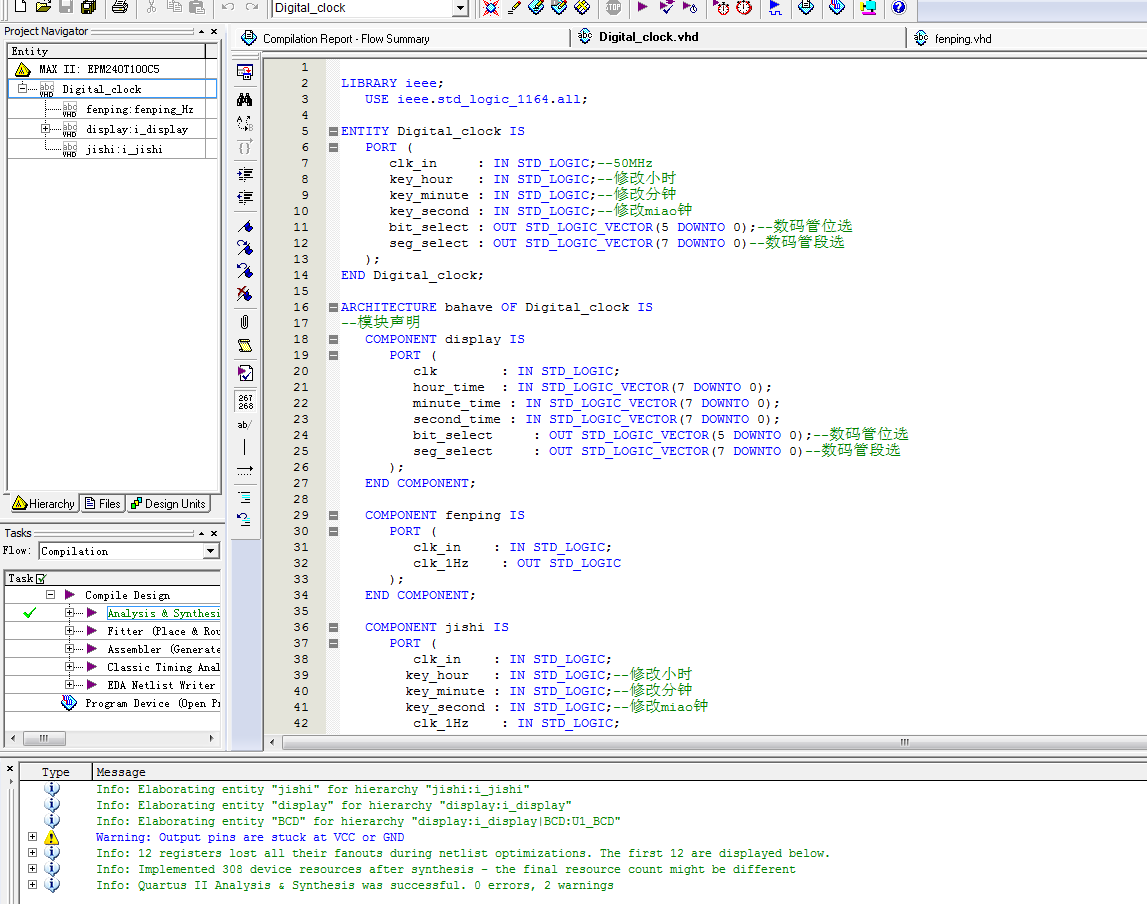

2. 程序文件

3. 程序编译

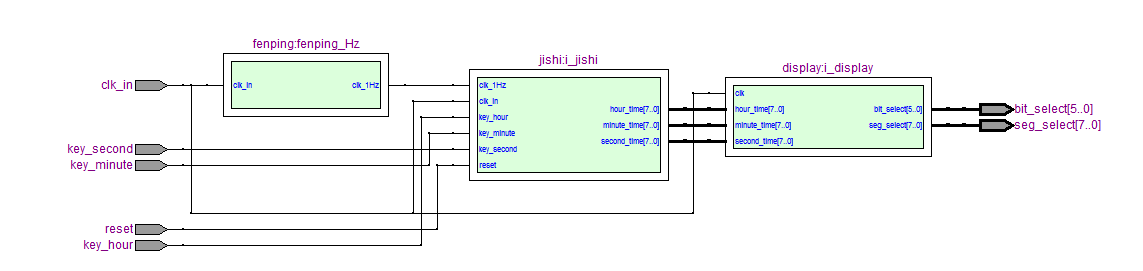

4. RTL图

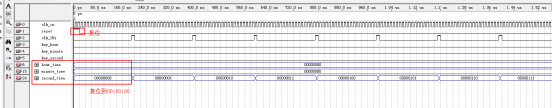

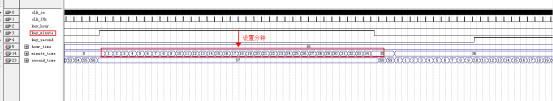

5. 仿真图

整体仿真图

分频模块仿真

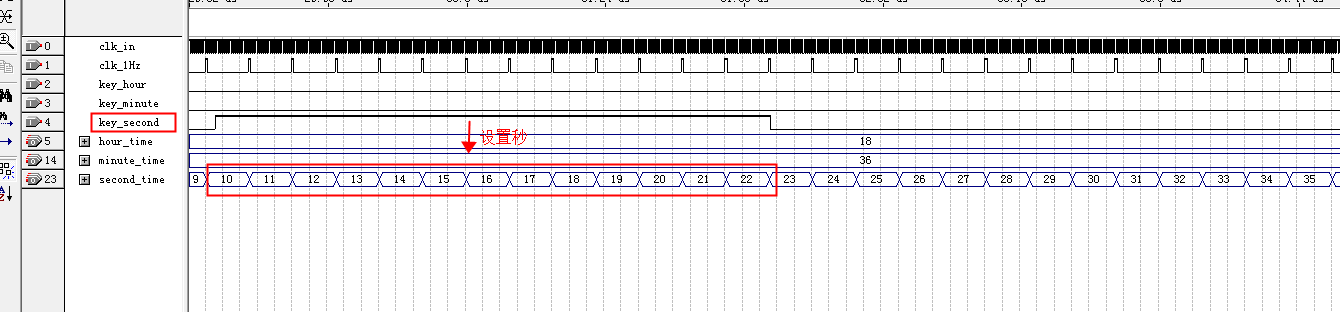

计时模块

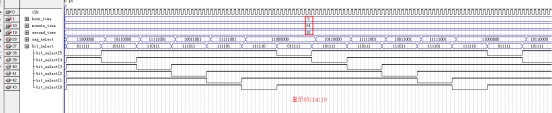

显示模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Digital_clock IS PORT ( clk_in : IN STD_LOGIC;--50MHz reset : IN STD_LOGIC;--reset key_hour : IN STD_LOGIC;--修改小时 key_minute : IN STD_LOGIC;--修改分钟 key_second : IN STD_LOGIC;--修改miao钟 bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END Digital_clock; ARCHITECTURE bahave OF Digital_clock IS --模块声明 COMPONENT display IS PORT ( clk : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END COMPONENT; COMPONENT fenping IS PORT ( clk_in : IN STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_in : IN STD_LOGIC; reset : IN STD_LOGIC;--reset key_hour : IN STD_LOGIC;--修改小时 key_minute : IN STD_LOGIC;--修改分钟 key_second : IN STD_LOGIC;--修改miao钟 clk_1Hz : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; SIGNAL hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL second_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL clk_1Hz : STD_LOGIC; BEGIN --分频到1Hz fenping_Hz : fenping PORT MAP ( clk_in => clk_in, clk_1Hz => clk_1Hz ); --计时模块 i_jishi : jishi PORT MAP ( clk_in => clk_in, reset =>reset, key_hour=> key_hour, key_minute=> key_minute, key_second => key_second,--修改miao钟 clk_1Hz => clk_1Hz, hour_time => hour_time,--时 minute_time => minute_time,--分 second_time => second_time--秒 ); --显示模块 i_display : display PORT MAP ( clk => clk_in, hour_time => hour_time, minute_time => minute_time, second_time => second_time, bit_select =>bit_select,--数码管位选 seg_select =>seg_select--数码管段选 ); END bahave;

源代码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/730435

推荐阅读

相关标签