- 1毕设项目分享 基于Spark网易云音乐数据分析_基于spark的音乐数据分析

- 2JMU 数科 数据库与数据仓库期末总结(1)

- 314、指针三剑客之二:树(结合LeetCode 104、110、543、437、101、1110、637、105、144、99、669、208学习)(99未进阶)(前缀树)_指针三剑客之三

- 4Python智能机器人2(电脑应用的使用,聊天等功能)_pyon

- 5BERT模型的输出

- 6Centos7升级Mysql8.0.37(mysql8小版本升级)_centos7 安装mysql8.0.37

- 7(一)Spark本地开发环境搭建与远程debug设置_spark debug

- 8Java语言概述,程序员翻身之路_java语言cnds

- 9ATtiny13与Proteus仿真-TM1637简单时钟仿真_proteus tm1637

- 10IP报文分片抓包简析_ip报文抓包分析

SOBEL图像边缘检测器的设计_vivado sobel边缘检测

赞

踩

本项目使用FPGA设计出SOBEL图像边缘检测器,通过分析项目在使用过程中的工作原理和相关软硬件设计进行分析详细介绍SOBEL图像边缘检测器的设计。

资料获取可联系wechat 号:comprehensivable

边缘可定义为图像中灰度发生急剧变化的区域边界,它是图像最基本的特征。边缘检测主要就是(图像的)灰度变化的度量、检测和定位,它是图像分析和模式识别的主要特征提取手段,它在计算机视觉、图像分析等应用中起着重要的作用,是图像分析与处理中研究的热点问题。在过去的20年里产生了许多边缘检测器,而Sobel算法只涉及加法操作,但却可以得到很好的划分效果,因而是图像处理系统中最常用的边缘检测算法。

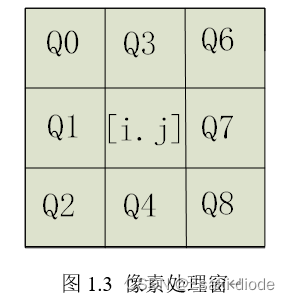

Sobel算法包括带4个3×3掩码的输入图像数据,即Sobel算子,它设置权重来检测水平、垂直、左对角、右对角各个不同方向上密度幅度的不同。这个过程通常被称为过滤。我们来看像素窗口(3×3),如图2所示。水平、垂直、左对角、右对角各图像方向上密度幅度的变化可以用如下算子进行计算:

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

H,V,DL,DR这四个参数用于计算梯度大小和方向。

对梯度大小的一个普遍估计值为:Magnitude=Max(H,V,DR,DL)

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

| Q0 | Q3 | Q6 |

| Q1 | [i,j] | Q7 |

| Q2 | Q5 | Q8 |

H,V,DL,DR这四个参数用于计算梯度大小和方向。

我们通过对图像灰度作直方图分析后,便可以给出区分度阀值

Threshold,区分度阀值往往要借助一定的经验并需要反复调整。如果Magnitude大于Threshold,则该像素被声明为边界像素,否则为一般像素。

本课题就是要求使用LPM兆功能块设计和VHDL程序设计相结合的方式或全部采用VHDL程序设计方式,用FPGA/CPLD实现Sobel算法。

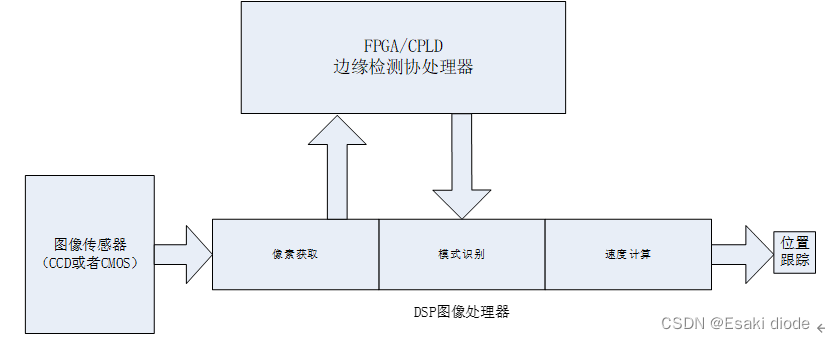

图1.1为一个DSP+FPGA/CPLD的图像处理系统的总体框图,本课题就是设计图中的图像边缘检测协处理器,并且能够绘画出图形边缘如图1.2所示;

图1.1 DSP+FPGA /CPLD 图像处理系统的组成框图

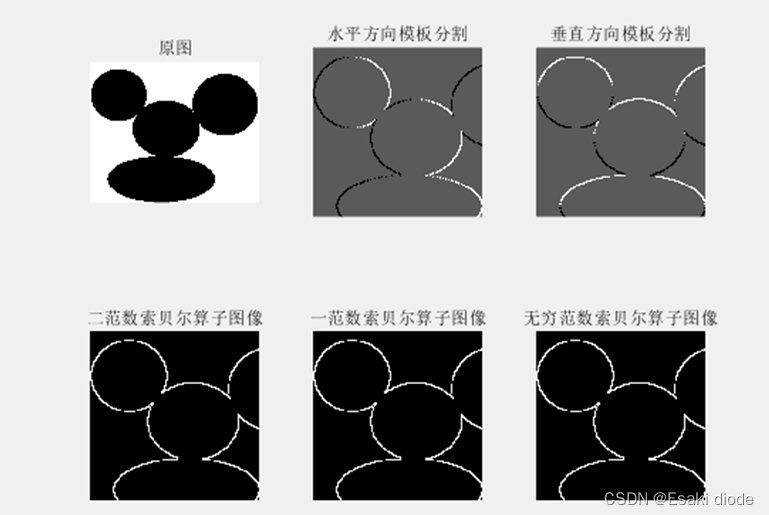

图1.2 实验效果

由于Sobel算法只涉及加法操作,但却可以得到很好的划分效果,因而是图像处理系统中最常用的边缘检测算法。

Sobel算法包括带4个3×3掩码的输入图像数据,即Sobel算子:

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);

V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);

DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

H,V,DL,DR这四个参数用于计算 水平、垂直、左对角、右对角各个不同方向的梯度大小和方向(该过程称之为过滤)。

梯度大小的估计公式:Magnitude=Max(H,V,DR,DL)。

边缘的判定:如果Magnitude>Threshold,则该像素为边界像素,否则为一般像素。处理像素端见图1.3所示;

Sobel的滤波函数为:

H=(Q0+2Q3+Q6)-(Q2+2Q5+Q8);

V=(Q0+2Q1+Q2)-(Q6+2Q7+Q8);

DR=(Q1+2Q0+Q3)-(Q5+2Q8+Q7);

DL=(Q1+2Q2+Q5)-(Q3+2Q6+Q7);

Magnitude=Max(H,V,DR,DL)

为了减少设计的复杂度,可将Sobel的滤波函数中的乘法运算可以改写成加法运算:

H=(Q0+Q3+Q3+Q6)-(Q2+Q5+Q5+Q8);

V=(Q0+Q1+Q1+Q2)-(Q6+Q7+Q7+Q8);

DR=(Q1+Q0+Q0+Q3)-(Q5+Q8+Q8+Q7);

DL=(Q1+Q2+Q2+Q5)-(Q3+Q6+Q6+Q7);

对于数据的处理,我们估算一下分别使用单片机、DSP、CPLD/FPGA所需的时间。

(1)如果使用12M的单片机:完成一次Sobel滤波操作需要的时间至少为:(24×2+20+2×3+2)×1us=72us。对于一幅600×800像素的图像,总共的时间为:600×800×72us=32s。

(2)若使用40M六级流水的DSP,他们的处理时间大概为 32s/24=1.4s。

(3)如果使用CPLD/FPGA进行自行设计,通过采用并行流水线技术假设使用50M的系统时钟,处理完一个像素点的时间为 4×1/(50M)=80ns,处理完一帧图像的时间为 800×600×80ns=38.4ms,结果处理速度比DSP高了大约两个数量级,从上可以看出,使用CPLD/FPGA进行自行设计有关图像处理模块,对整个系统速度的改善是很非常明显的。

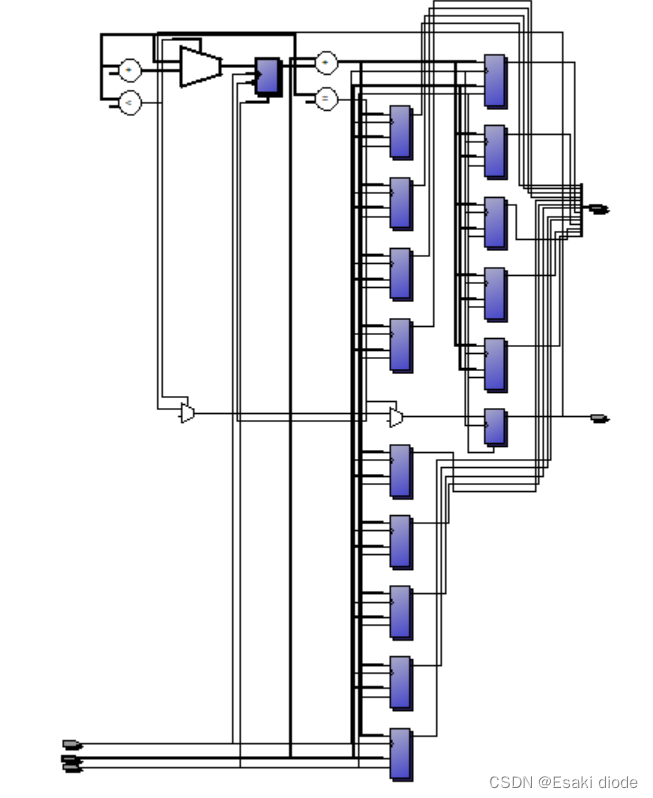

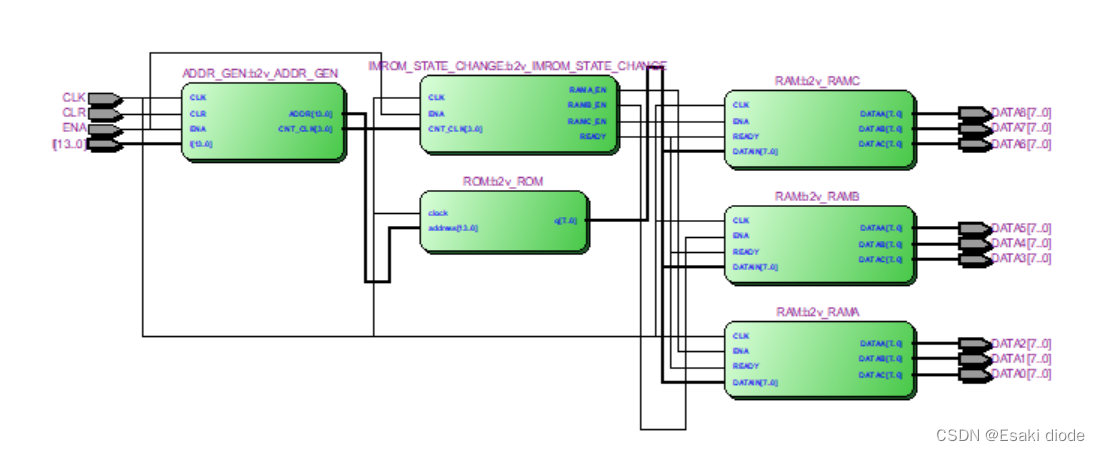

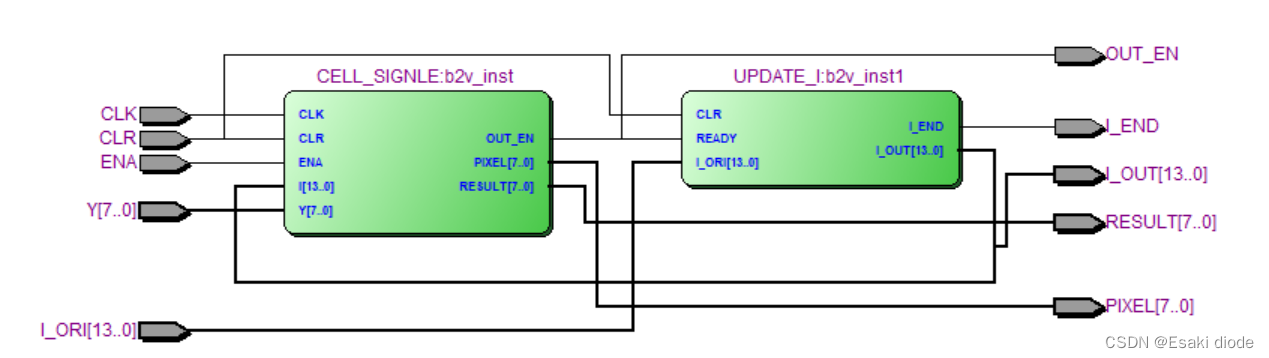

通过使用VHDL代码设计出对应的模块,以下为部分RTL图;

UPDATE的RTL图

读取的RTL图

由于本次实验要求只需要在软件上显示图像并且进行边缘化即可,无需在硬件在显示出像素的数据,整体RTL图见图4.1所示,主要包括俩个模块,即SOBEL算法的部分和数据输出的部分,在SOBEL算法内部又包括了许多的模块,从而达到我们需要设计的目的。

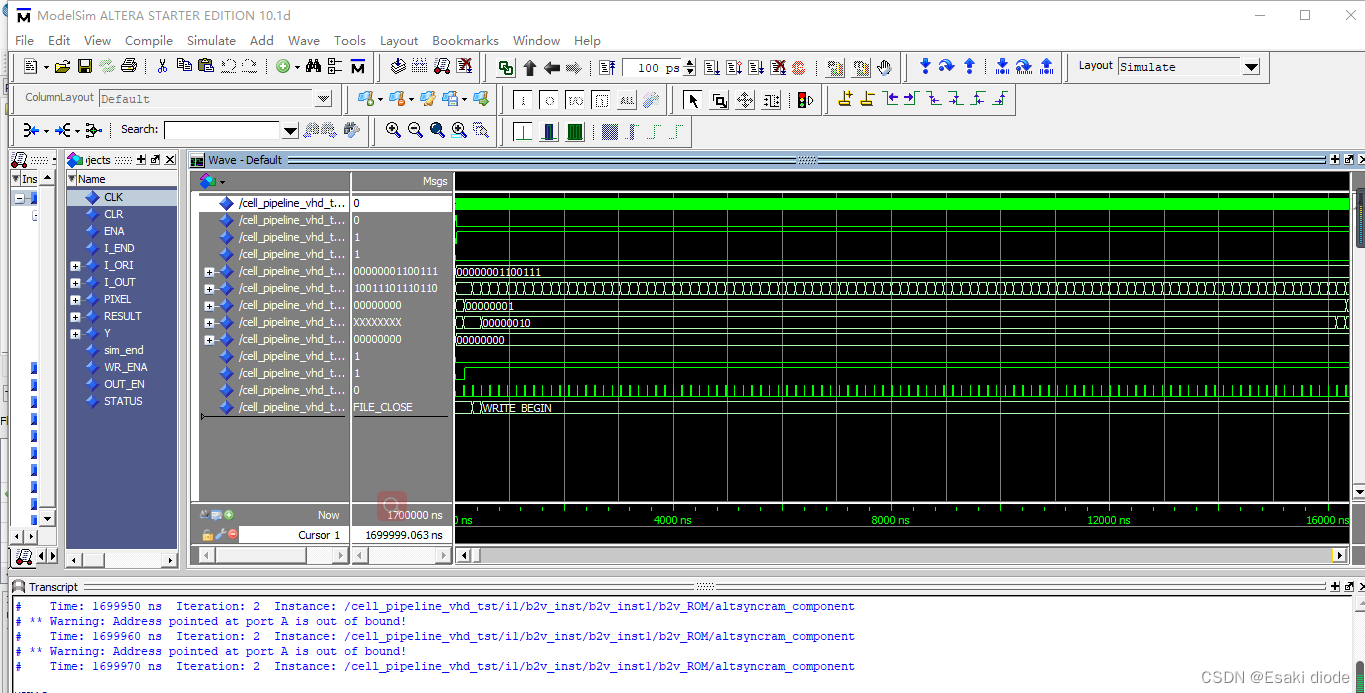

编译完成后调用ALTERA-MODELSIM仿真如下图4.4所示;

图4.4 调用ALTERA-MODELSIM仿真

图4.4 调用ALTERA-MODELSIM仿真

总结:

对SOBEL算法有了初步的了解,并且本次SOBEL算法对图形边缘检测能够很好的应用,对嵌入式的功能有了更多的知晓,也明白VHDL语言的强大之处;

本次实验网上资料较多,要求使用matalab软件和EDA仿真等软件配合使用,在网络上寻找相关资料并且去深入了解,对于我的自学能力有了进一步的提高。