- 1[MySQL]数据库原理9——喵喵期末不挂科

- 2DAY29| 491.递增子序列 ,46.全排列 ,47.全排列II

- 3python 3.7 安装demjson_demjson安装

- 4Java实战09之 linux 下 prometheus+Grafana 监控 快速上手_java 普罗米修斯

- 5【网络安全】DVWA靶场实战&BurpSuite内网渗透

- 6门控循环单元网络在图像处理领域的潜力

- 7小红书最强导流私域,合规引流,无屏蔽,可跳转任意场景,打造高效转化通道_小红书私域跳转

- 8大模型论文周报 | 来自北大、百度、DeepMind、OpenAI等机构前沿论文研究

- 9SQL Server 数据库高级编程(T-SQL)笔记_sql server数据库编程

- 102022年NOC大赛编程马拉松赛道初赛图形化低年级A卷-正式卷,包含答案_编程马拉松初赛题

【紫光同创国产FPGA教程】【PGL50H第六章】DDR3 读写实验例程_盘古50k的ddr3分开用

赞

踩

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

紫光同创PGL50H开发平台(盘古50K)

一:盘古50K开发板(紫光同创PGL50H开发平台)简介

盘古50K开发板(紫光同创Logos系列PGL50H关键特性评估板)采用核心板+扩展板的结构,并使用高速板对板连接器进行连接。

核心板由 FPGA+2 颗 DDR3+Flash+电源及复位构成,承担 FPGA 的最小系统运行及高速数据处理和存储的功能。FPGA 选用紫光同创 40nm 工艺的 FPGA(logos 系列:PGL50H-6IFBG484)。PGL50H 和 DDR3 之间的数据交互时钟频率最高到 400MHz,2 颗 DDR3 的数据位宽为 32bit,总数据带宽最高 25600(800×32)Mbps,充分满足高速多路数据存储的需求。

PGL50HFPGA带有4路HSST高速收发器,每路速度高达 6.375Gb/s,适合用于光纤通信和PCIe数据通信;电源采用多颗 EZ8303(艾诺)产生不同的电源电压。底板为核心板扩展丰富的外围接口, 预留 HDMI 收发接口用于图像验证及处理;预留的光纤接口、10/100/1000M 以太网接口,PCIE 接口,方便各类高速通信系统验证;预留一个 40pin 的 IO 扩展连接器,方便用户在开发平台基础上验证模块电路功能。

二、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

三、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器解决方案,配置方式比较灵活,采用软 核实现 DDR memory 的控制,有如下特点:

➢ 支持 DDR3

➢ 支持 x8、x16 Memory Device

➢ 最大位宽支持 32 bit

➢ 支持裁剪的 AXI4 总线协议

➢ 一个 AXI4 256 bit Host Port

➢ 支持 Self_refresh,Power down

➢ 支持 Bypass DDRC

➢ 支持 DDR3 Write Leveling 和 DQS Gate Training

➢ DDR3 最快速率达 800 Mbps

四、实验设计

安装 DDR3 IP 核

PDS 安装后,需手动添加 DDR3 IP,请按以下步骤完成:

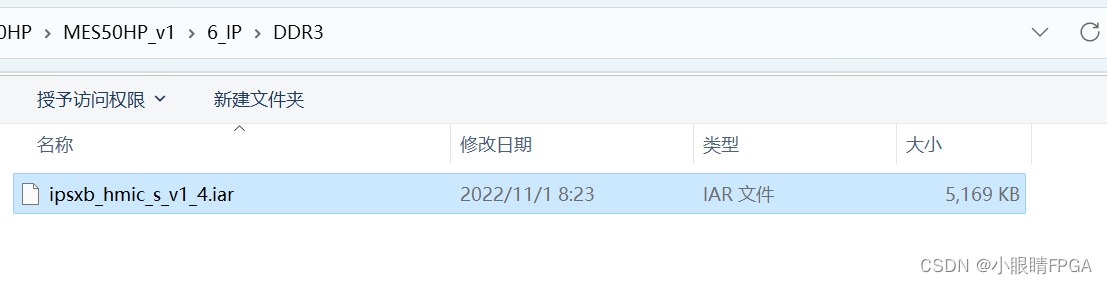

(1)DDR3 IP 文件:6_IP_setup_packet\DDR3\ipsxb_hmic_s_v1_4

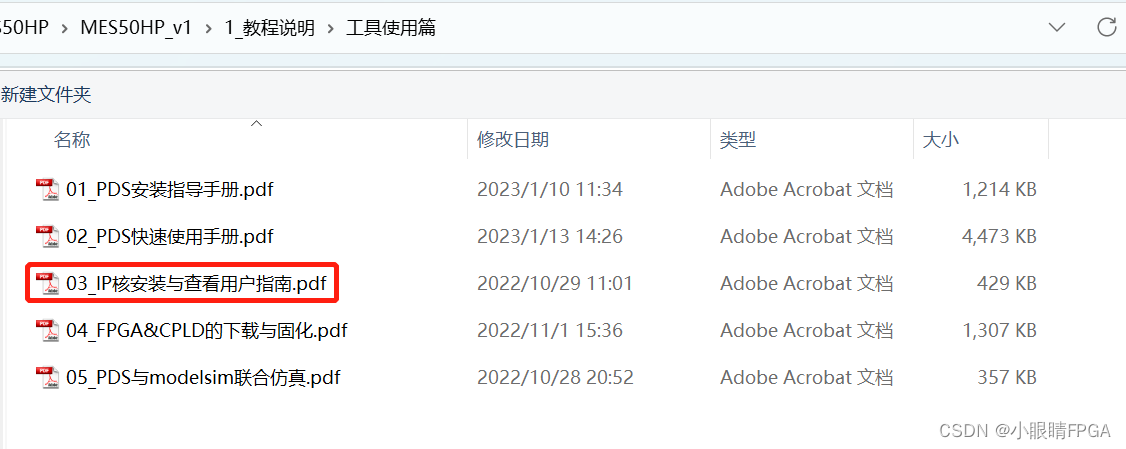

(2)IP 安装步骤:1_Demo_document\工具使用篇\03_IP 核安装与查看用户指南

DDR3 读写 Example 工程

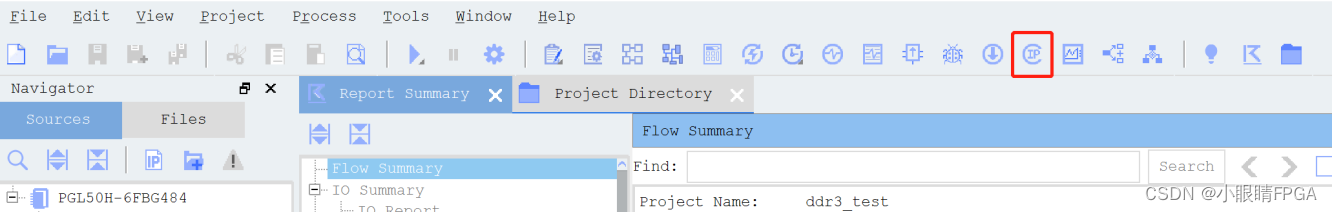

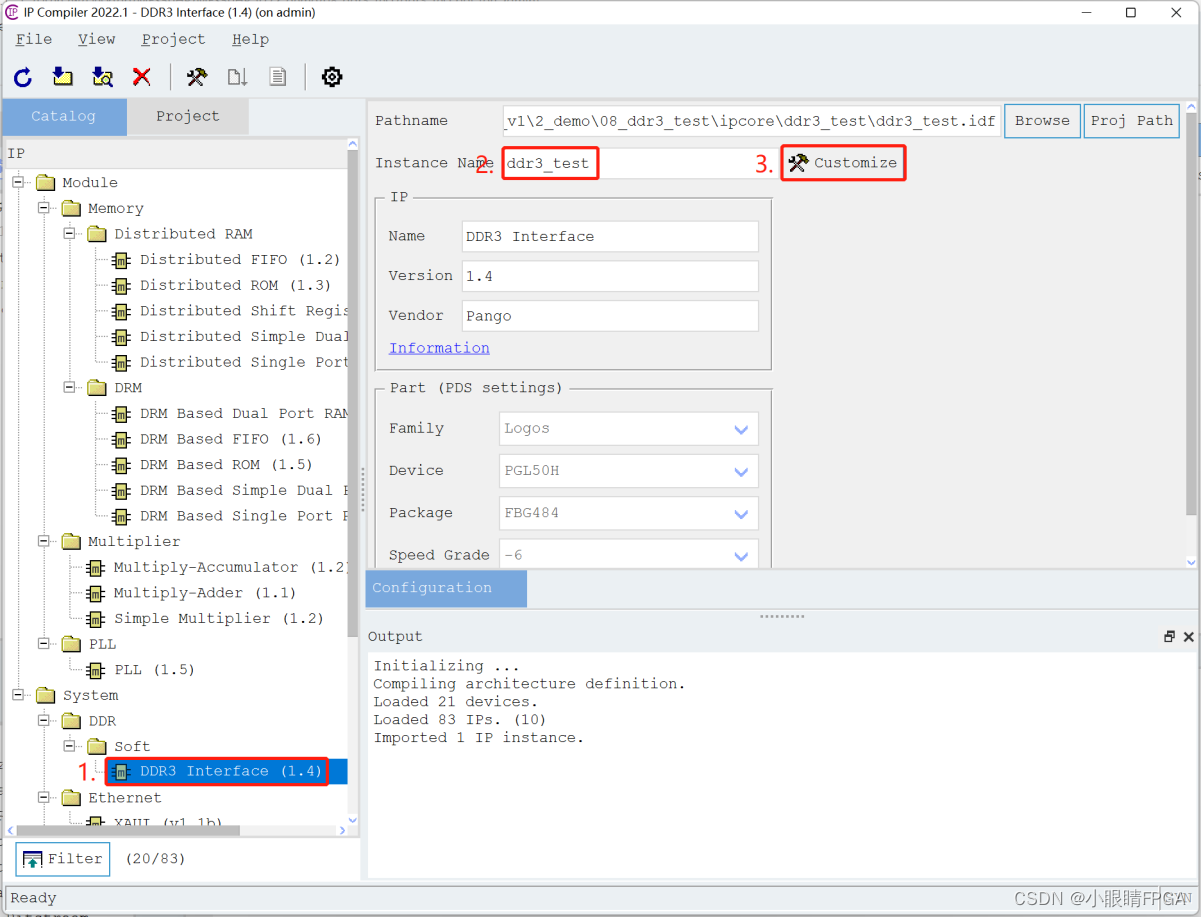

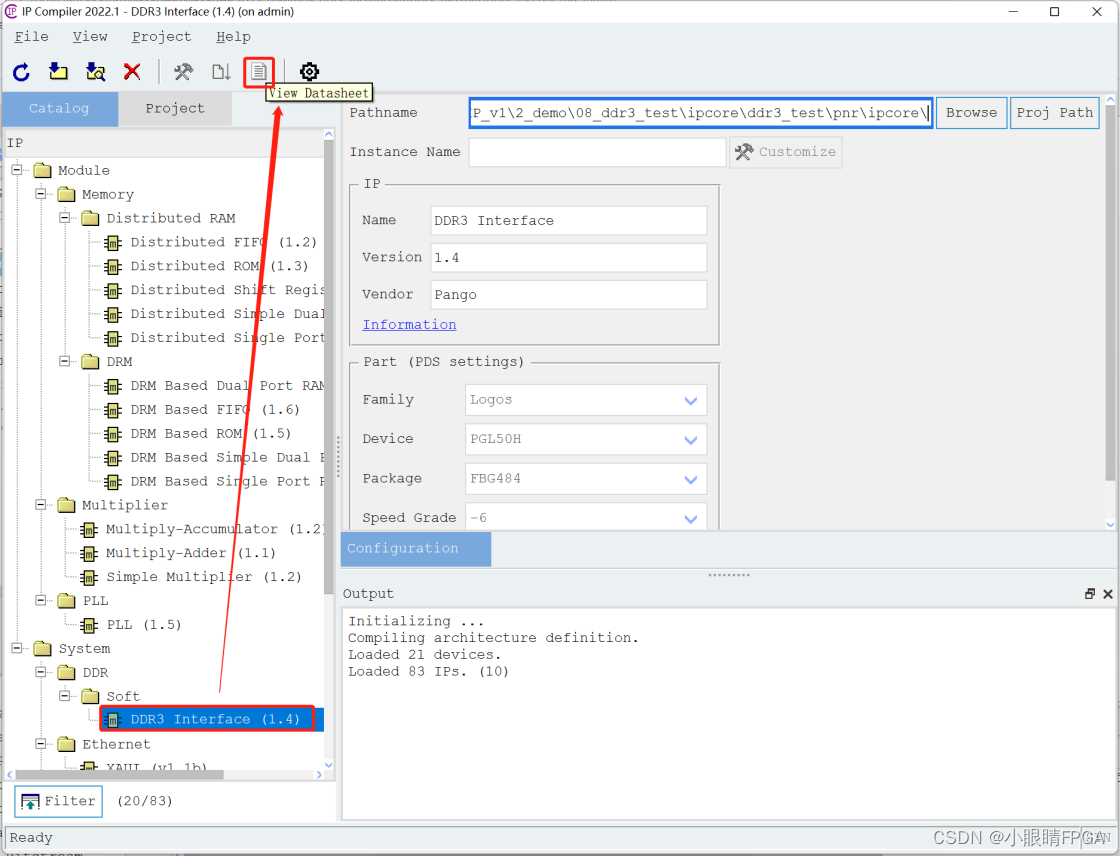

1.打开 PDS 软件,新建工程 ddr3_test,点开如下图标,打开 IP Compiler;

2.选择 DDR3 IP,取名,然后点击 Customize;

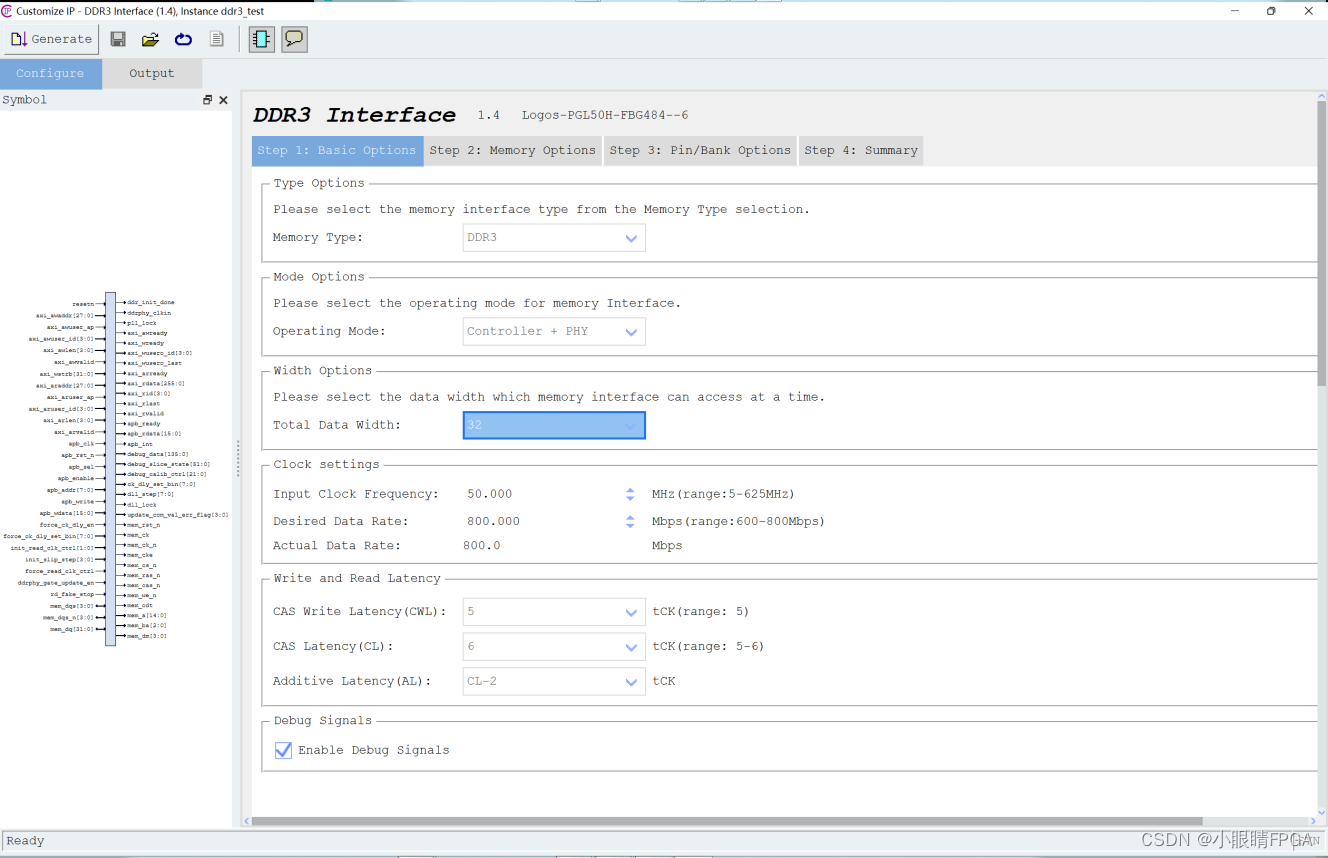

3.在 DDR3 设置界面中 Step1 按照如下设置:

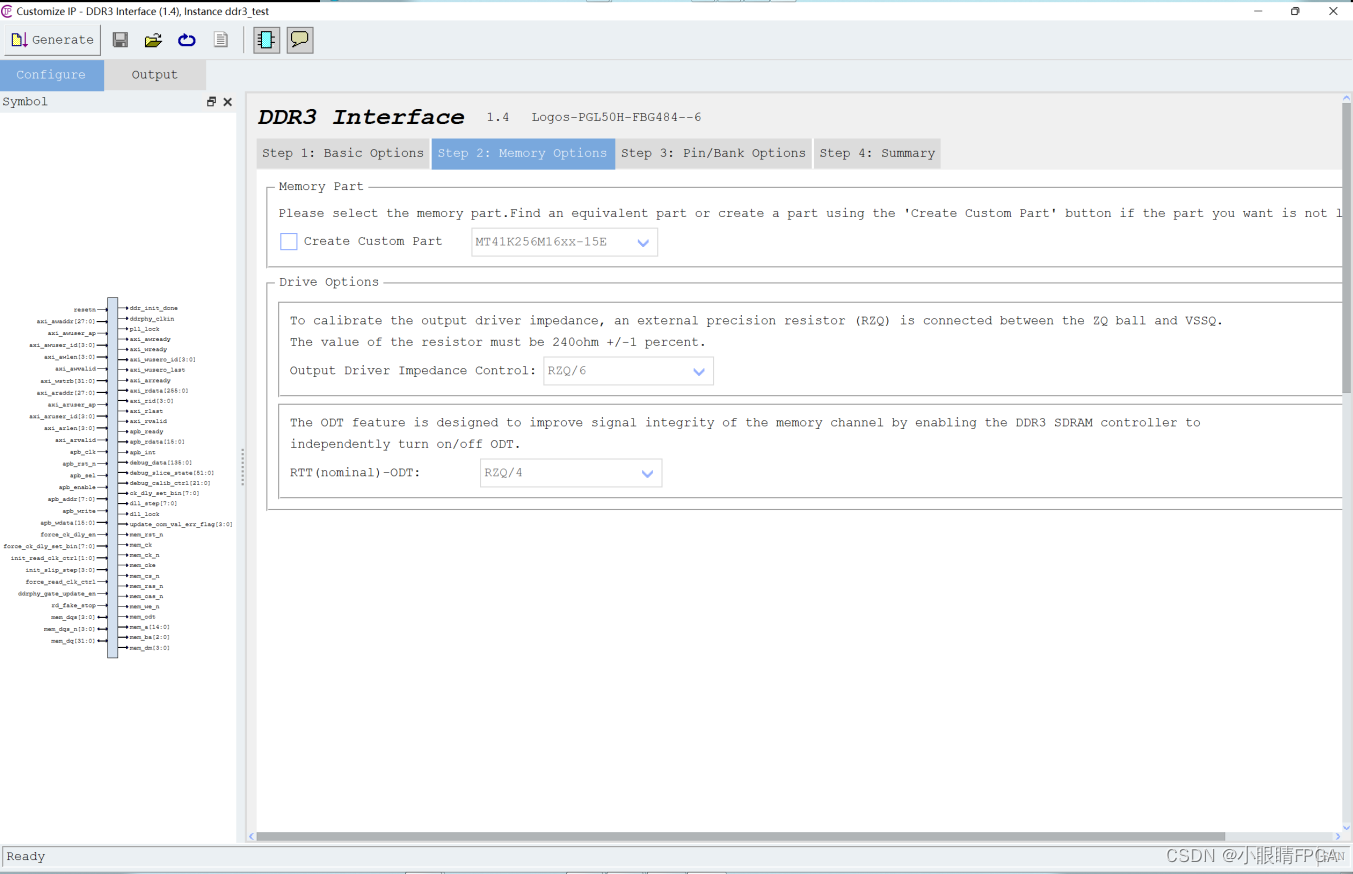

4. Step2 按照如下设置:

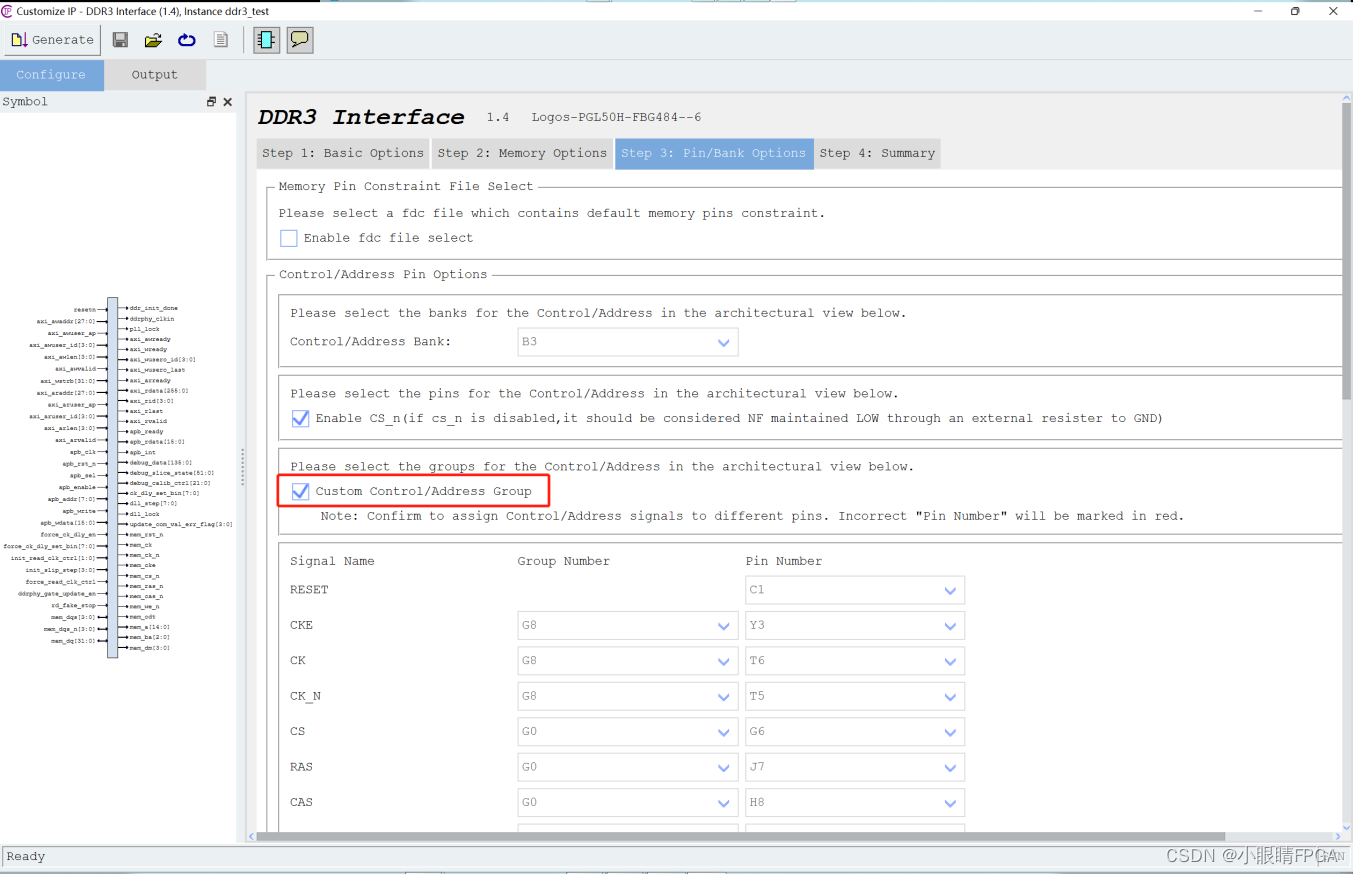

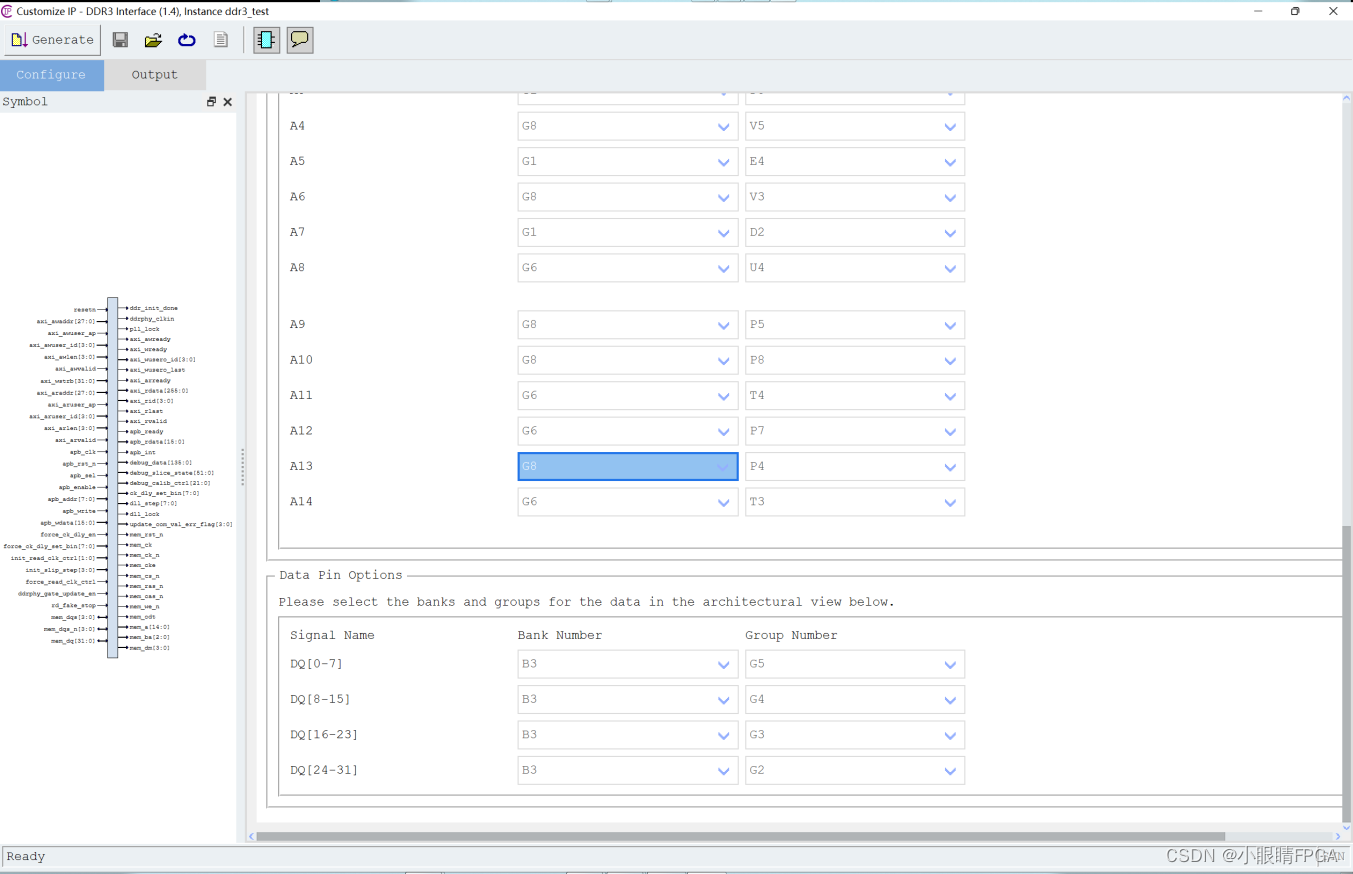

5.Step3 按照如下设置,勾选 Custom Control/Address Group,管脚约束参考原理图:

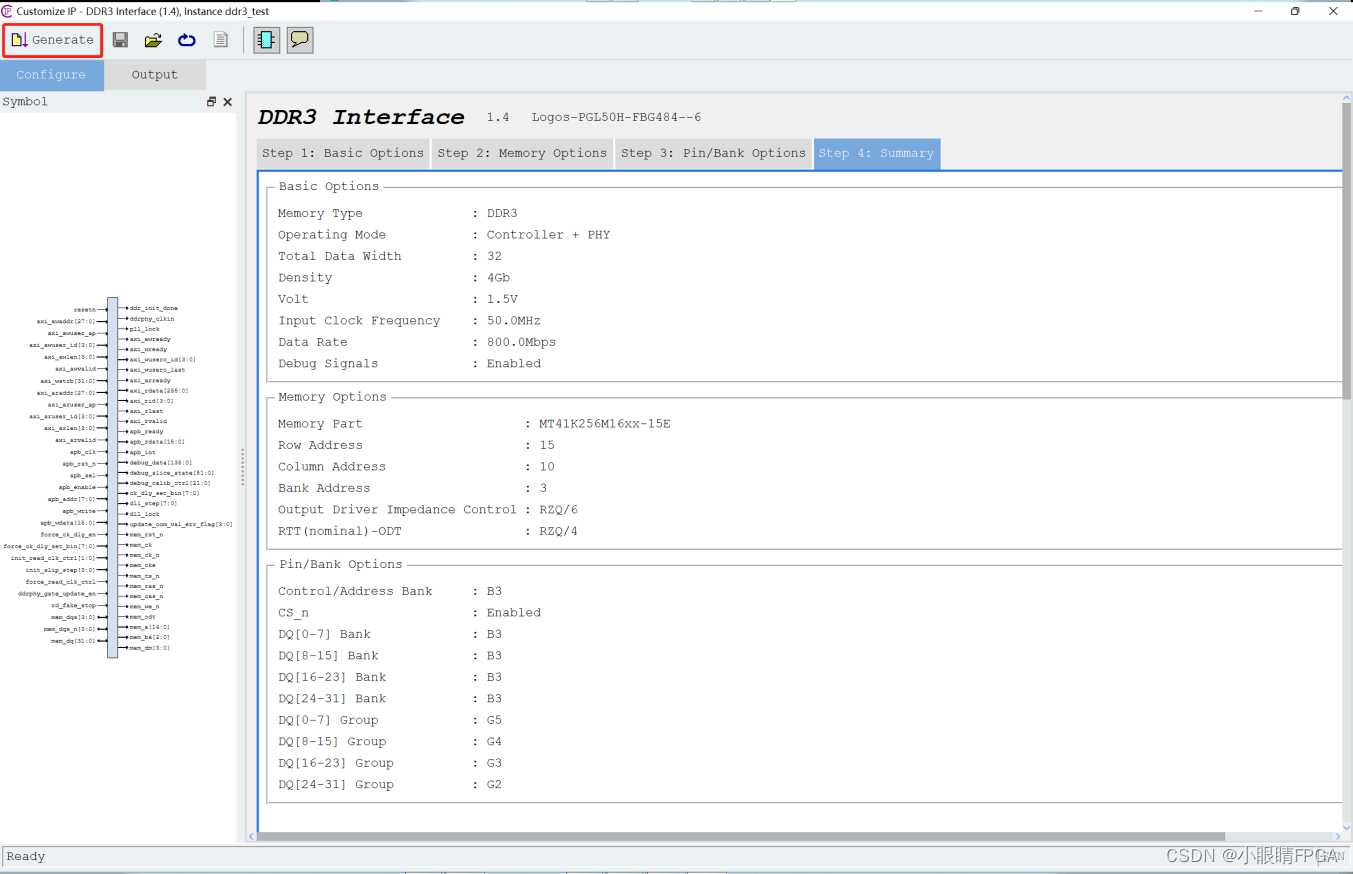

6.Step4 为概要,点击 Generate 可生成 DDR3 IP;

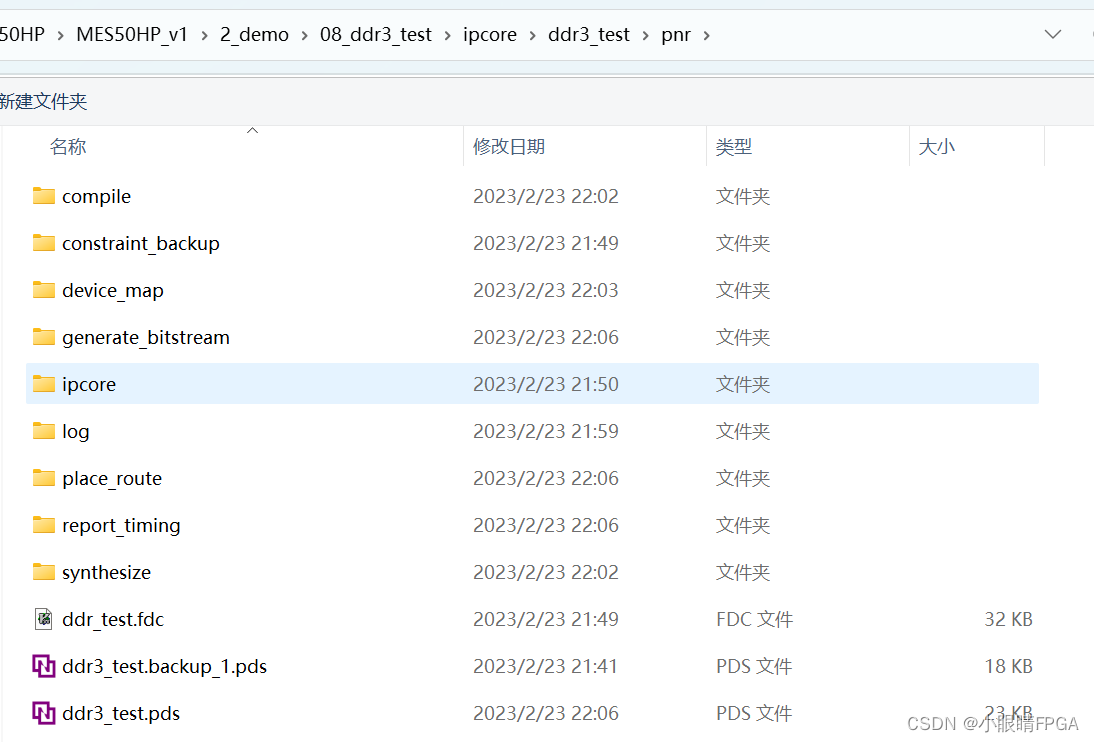

7.关闭本工程,按此路径打开 Example 工程: 2_Demo\08_ddr3_test\ipcore\ddr3_test\pnr

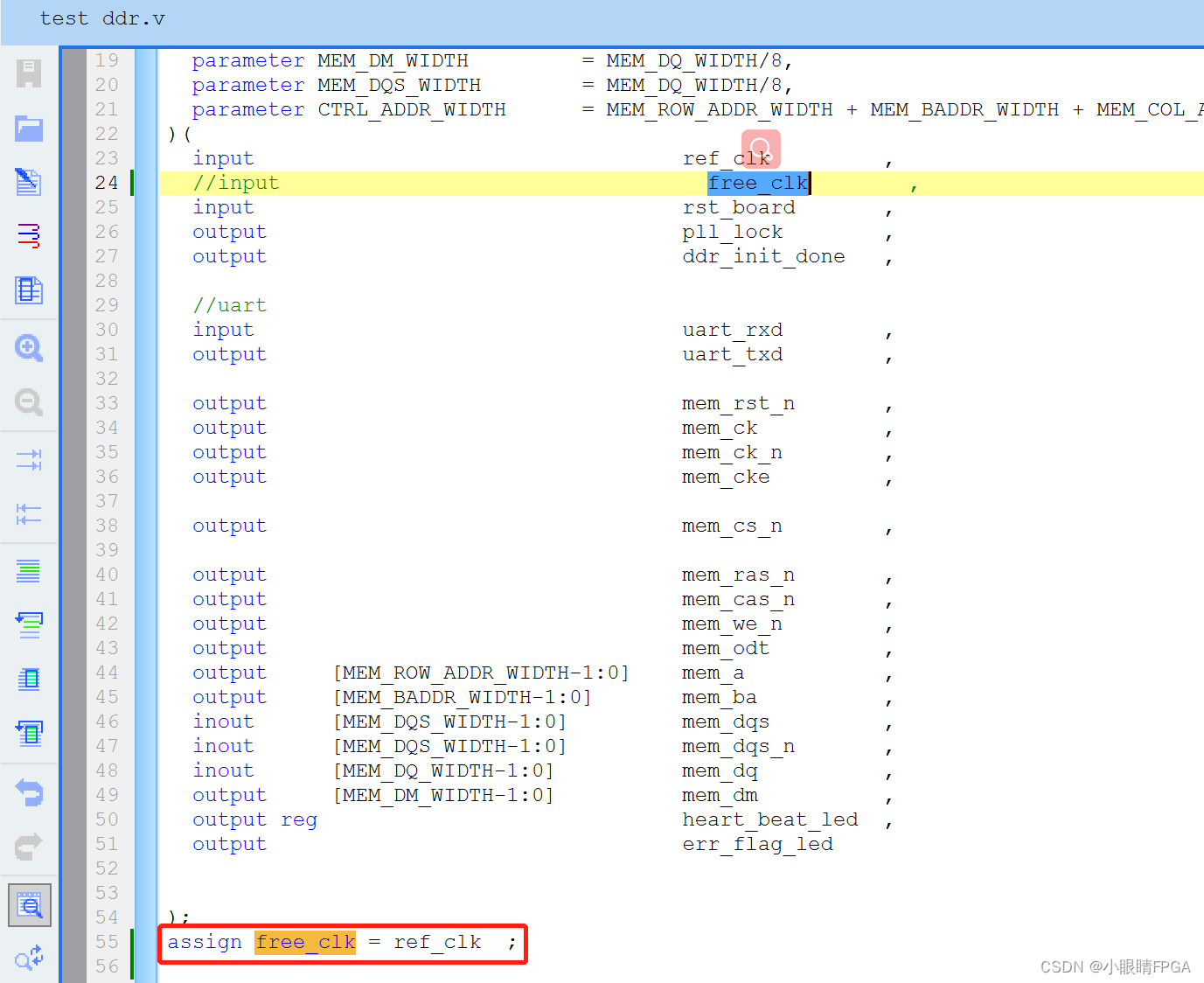

8.打开顶层文件 free_clk、ref_clk 可使用同一时钟源:

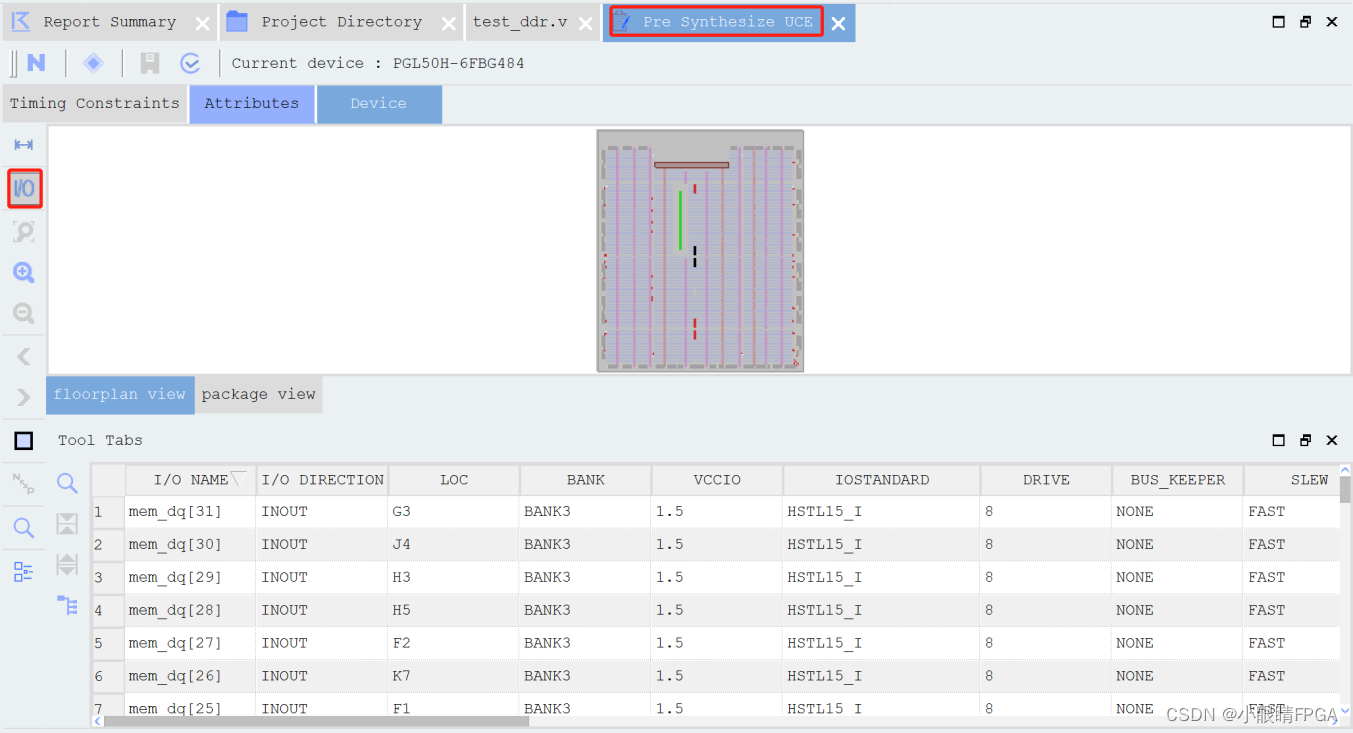

9.对“Step3 已做管脚约束”外的其他管脚,对照原理图使用 UCE 工具进行修改:

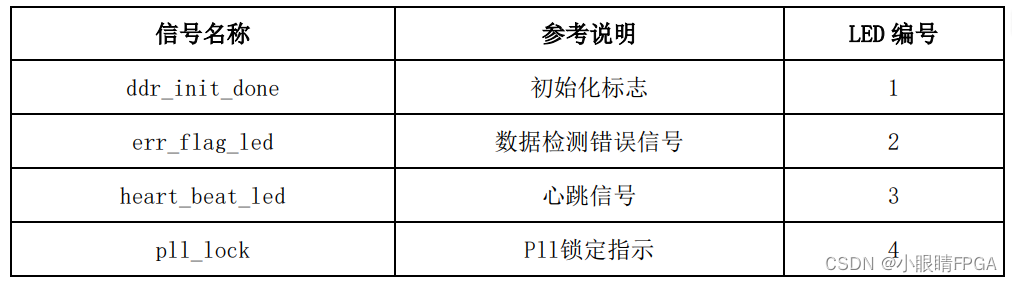

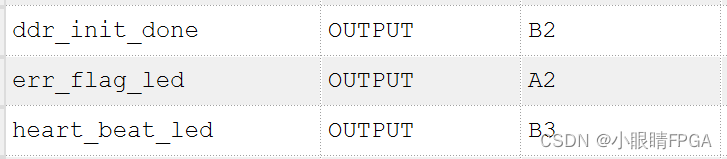

10.以下管脚可约束在 LED,方便观察实验现象;

![]()

11.可按以下方式查看 IP 核的用户指南,了解 Example 模块组成;

五、实验现象

注:例程位置:2_Demo\07_ddr3_test\ipcore\ddr3_test\pnr 下载程序,可以看到 LED1 常亮,LED2 常灭, LED3 闪烁,LED4 常亮;