- 1ComfyUI中使用 SD3 模型(附模型下载详细说明)_comfyui sd3

- 2ChatGLM4重磅开源! 连忙实操测试一波,效果惊艳,真的好用!_chatglm4 开源发布时间

- 310款国内可用的AI工具分享,每一款都能让你工作效率翻倍_魔术todo任务分解

- 4普通人也能搞的,0成本,热门副业AI绘画,月入1w+_2024年0成本如何日入10000

- 5聚类模型的算法性能评价

- 6NLP综述:知识脉络图、四大类任务【序列标注(分词、词性标注、NER)、分类任务(文本分类、情感分析)、句子关系判断(顺序判断、相似度计算)、生成式任务(机器翻译、问答 、文本摘要)】_图书馆nlp标注 脉络洞察

- 7百度云不限速客户端让你获取SVIP速度_加速链接获取中啥意思

- 8C++11 智能指针详解_c++ 11所有的智能指针

- 9大模型入门指南:基本技术原理与应用_大模型原理

- 10Kafka和Spark Streaming的组合使用学习笔记(Spark 3.5.1)_2. kafka和structured streaming组合使用 (1)编写生产者程序每1秒生成一

FPGA中的BEL Site Tile FSR SLR分别指什么?_fpga中slr与sll

赞

踩

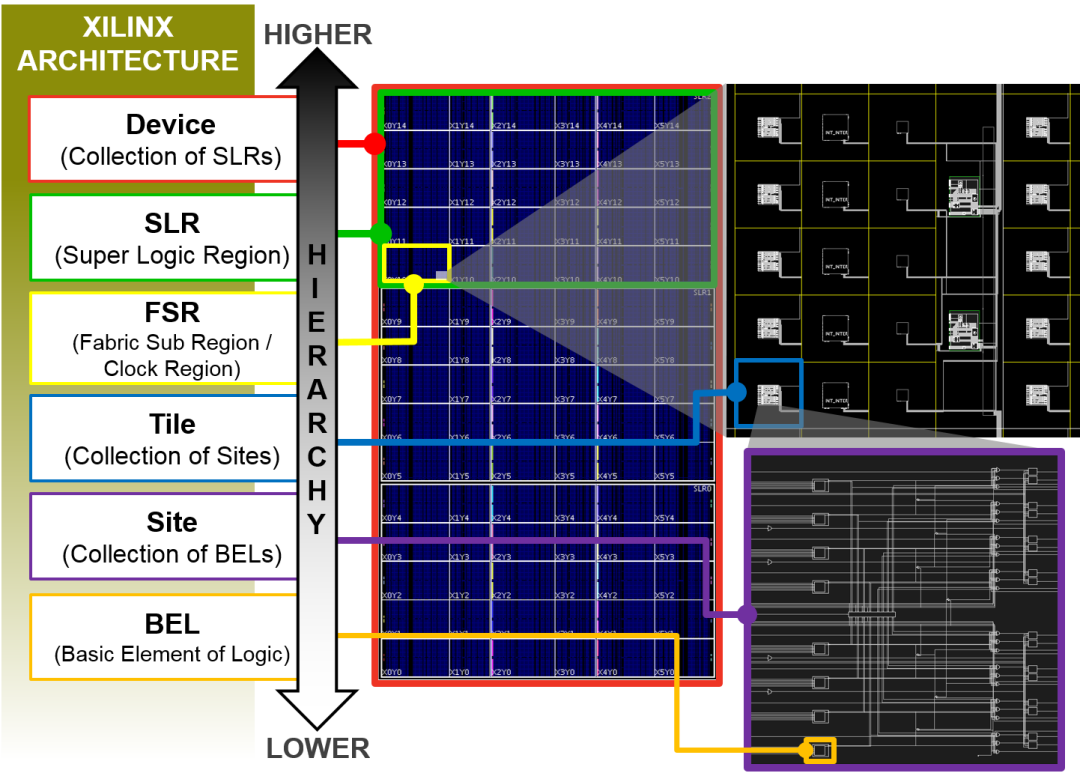

在Xilinx FPGA中,从底层到整个设备可以划分为6个层次:

BEL

Site

FSR

SLR

Device

下面我们从下到上依次来看一下各个定义。

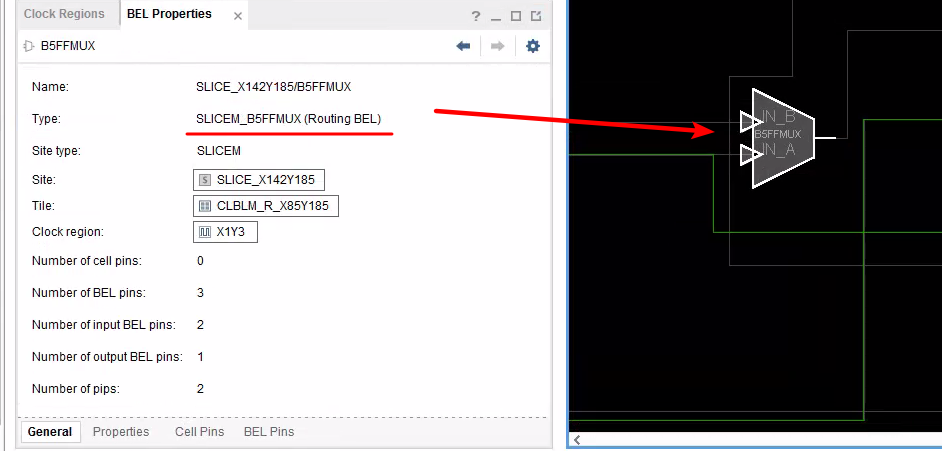

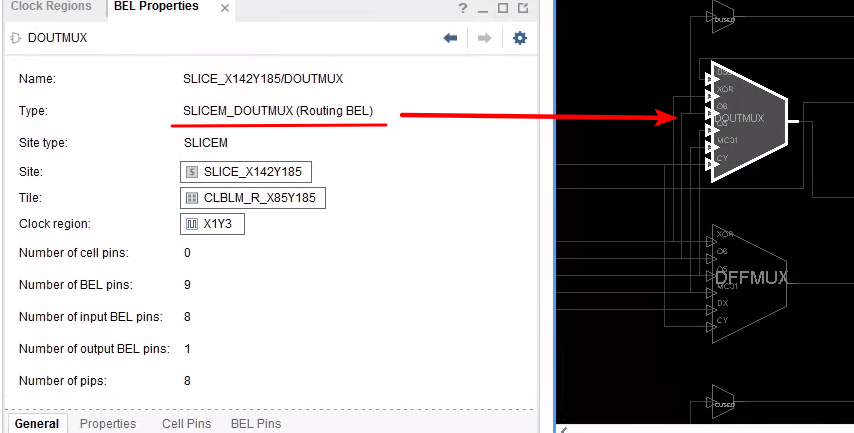

BEL(Basic Element of Logic)

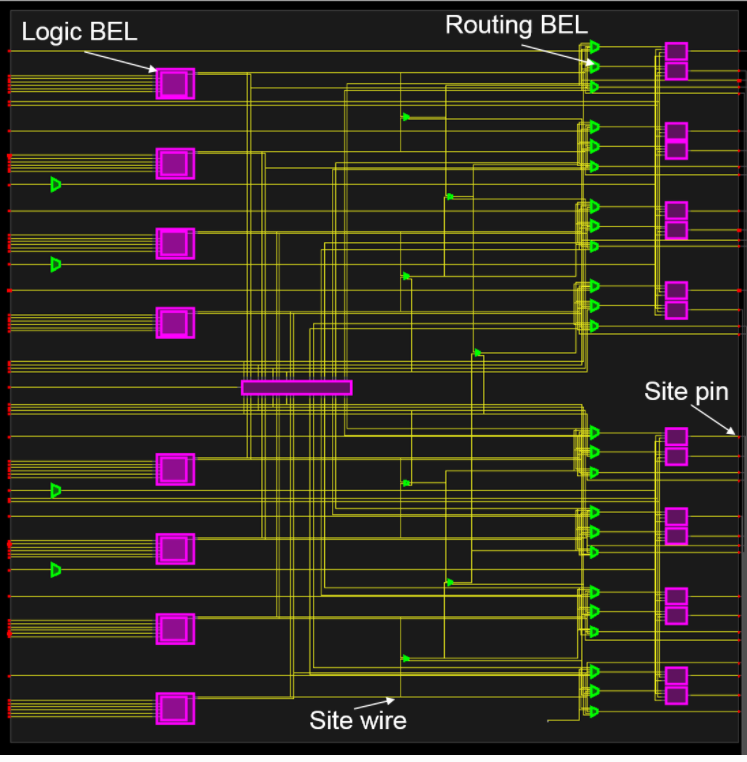

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。像我们常说的LUT、FF、CARRY都属于Logic BEL,Routing BEL我们平时不常说,很多工程师可能也没太听过,像FFMUX和DOUTMUX都属于Routing BEL,它们分别长下面这样:

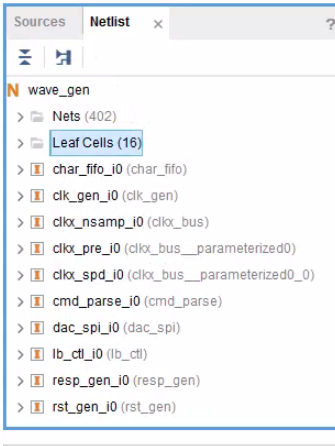

在Vivado综合或实现的Design中,可以看到会在每一个模块下都会有Nets和Leaf Cells。

image-20211224212553327

Leaf Cells就是FPGA中一个个真实存在的硬件模块,Vivado中place_design做的工作就是把这些Leaf Cells放到合适的BEL上。

image-20211224212627988

Site

一系列相关的元素与它们的连线组成了Site,Site中主要包含下面三种:

-

BEL

-

Site的输入输出管脚

-

Site内部的连线

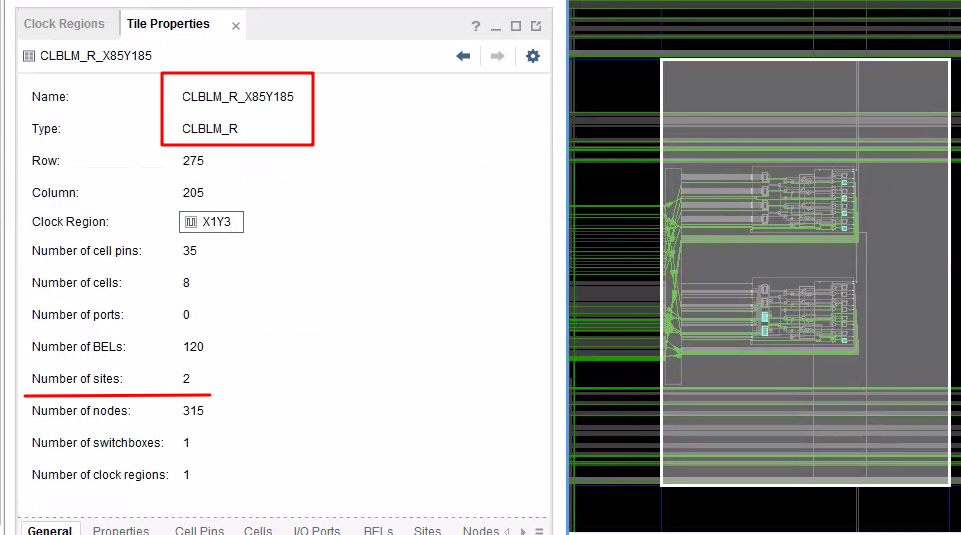

Site一般都是跟Slice、DSP48、BRAM等是对应的,我们以Slice为例,在7系列的FPGA中,一个CLB有两个Slice,下图的白色框是一个CLB,从左边的Properties中可以看出,包含了两个site,其实就是包含了两个Slice。每个Slice都有独立的site,所以这个CLB中就有两个sites。

Xilinx FPGA中很多元素的位置都是以_X_Y结尾来表示该元素在坐标中的位置,下图中的这个Slice的位置是X142Y185。

Tile

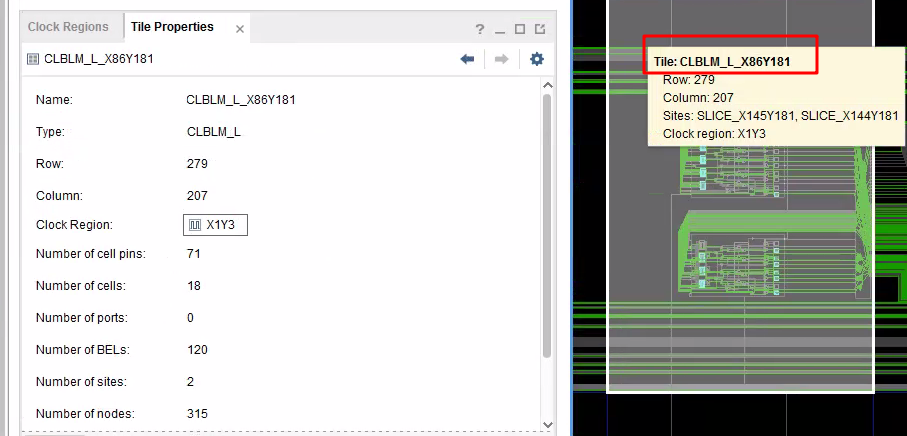

Tile是比Site更高一级的概念,一个Tile里面包含多个Site,Tile没有pin的概念,比如下面这个Tile,其实就是一个CLB。

FSR

FSR就是Fabric Sub Region or Clock Region,是由一片Tile组成的,在UltraScale的FPGA中,所有的FSR的高度都有60个CLB,但宽度不尽相同。

时钟routing和distribution的粒度与FSR相同,在UltraScale的FPGA中,有24个水平的routing track,24个垂直的routing track,24个水平的distribution track和24个垂直的distribution track,相邻的FSR就靠这些track互连。

SLR

SLR就是Super Logic Region,这个概念仅针对SSIT的FPGA,也就是包含多个die的芯片,这样每个die就被称为一个SLR。

Device

这个概念就无需过多介绍,就是指整个FPGA;如果是单个die的片子,那么多个FSR就组成了Device,如果是多个die的片子,那么多个SLR组成了Device。