热门标签

热门文章

- 12023 一带一路暨金砖国家技能发展与技术创新大赛【Web 应用软件测试】系统功能测试报告参考_金砖web技术赛项

- 2运维人员的未来:新技术下的挑战与机遇_运维新技术

- 3RabbitMQ,RocketMQ,Kafka 消息模型对比分析_rocket mq、rabbit mq和kafka分别是通过什么形式获取消息?

- 4学python有什么用-普通人学Python有什么用?

- 5ImportError: cannot import name 'imread'_importerror: cannot import name 'imread' [31]

- 6前端Vue小兔鲜儿电商项目实战Day05_vue小兔鲜儿项目

- 72022年Ei收录的中国期刊源目录_cpxsourcelist2022

- 8基于maven的spring boot 项目porm文件配置(含定时器,数据抓取,分词器依赖配置)

- 9解决github网站的css,js文件被墙

- 10关于数据库容灾之数据容灾的总结_数据存储与容灾课程总结体会

当前位置: article > 正文

【FPGA静态时序分析与时序约束_1】基础知识总结1_正点原子fpga静态时序分析与时序约束

作者:菜鸟追梦旅行 | 2024-05-26 02:31:04

赞

踩

正点原子fpga静态时序分析与时序约束

【FPGA静态时序分析与时序约束1】基础知识总结

0、前言

【废话计划】今天开始学习FPGA静态时序分析与时序约束,计划15天内学习完!!!

1、 为什么要时序约束?

简而言之:不加时序约束,可能会出现错误(也可能,不出现,看缘分)。

一般对于高速传输场景添加时序约束,以确保数据准确。

2、什么是时序分析?

针对设计电路,添加是时序约束后,分析系统是否满足设定的时序要求。

- 当时序约束要求过高时,要么降低要求,要么更换更加高速的器件。

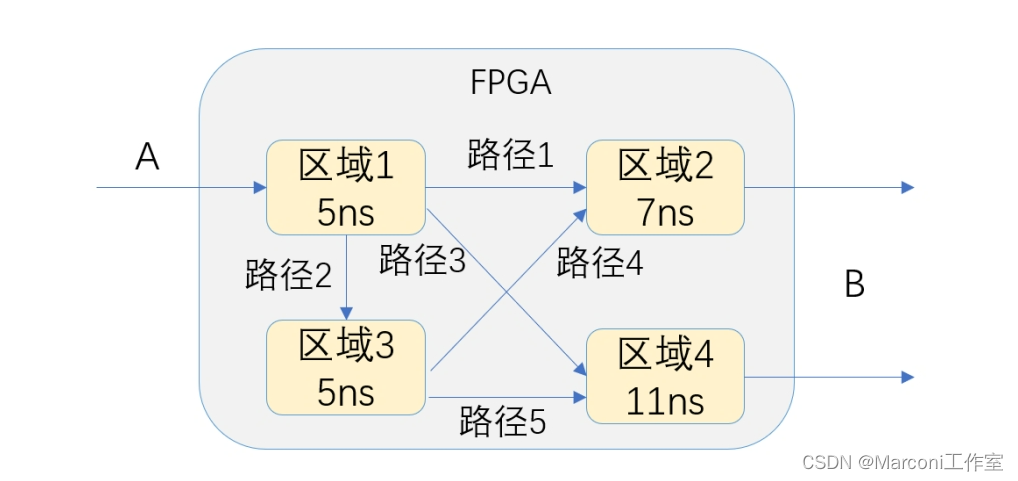

例如:一个信号需要从输入到输出在 FPGA 内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在 FPGA 内部的延时不能超过 13ns,而开发工具在执行过程中会找到一些可能的布局布线方式:

图中是可能的布线情况:

区域 1 的延迟是 5ns,

区域 2 的延迟是 7ns,

区域 3 的延迟是 5ns,

区域 4 的延迟是 11ns;

【1】走哪条路径满足设计的时序约束要求?

【答】: 只有 1 条

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/624789

推荐阅读

相关标签