热门标签

热门文章

- 1重磅推荐:很全的 Java 权限认证框架!

- 2【Python报错】已解决ImportError: cannot import name ‘mapping‘ from ‘collections‘_importerror: cannot import name 'mapping' from 'co

- 3Linux系统centOS7在虚拟机下的安装及XShell软件的配置

- 4【示例】postman基础使用教程_postman访问百度怎么配置

- 5GitHub帮助:创建SSH Keys_there are no ssh keys with access to your account.

- 6IDEA调优_-xxlogc

- 7如何在github上pull request?_github pull request

- 8STM32-OTA升级

- 9spark—连接hive、mysql_spark mysql与hive联查

- 10mac外接显示器 字体发虚解决方案_macbook外接显示器字体小

当前位置: article > 正文

FPGA上基于Verilog HDL的千兆以太网UDP IP协议实现与GMII接口对接_verilog千兆以太网

作者:运维做开发 | 2024-08-09 00:04:53

赞

踩

verilog千兆以太网

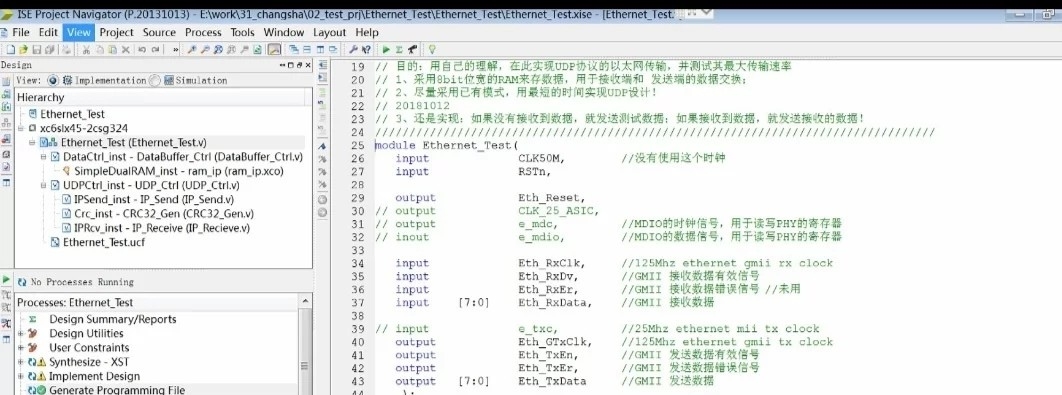

FPGA 以太网 UPD/IP 协议实现 fpga 千兆以FPGA 以太网 UPD/IP 协议实现 fpga 千兆以FPGA 以太网 UPD/IP 协议实现, fpga 千兆以太网接口控制器,FPGA UDP/IP协议实现 在FPGA上实现UDP通信,Verilog HDL描述语言实现,数据链路层,网络层,传输层有纯逻辑实现。

接口为GMII接口,与外部phy对接。

实验器件为s6,因此编译环境用的是ISE14.7。

换vivado轻松无压力,随意移植。

ID:6958652417958173

不过一场少年梦。,

FPGA以太网UDP IP协议实现

随着互联网的迅猛发展,数字通信技术也在不断演进。以太网作为一种常见的局域网通信协议,被广泛应用于各种设备之间的数据传输。FPGA(Field-Programmable Gate Array)是一种可编程的集成电路芯片,具有自由度高、速度快等特点,因此在以太网通信领域也得到了广泛的应用。

本文将重点讨论FPGA实现以太网UDP IP协议的过程。首先,我们需要了解FPG

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/运维做开发/article/detail/950452

推荐阅读

相关标签