- 1如何从github上下载文件并运行_如何打开一个github上下载的app

- 2基于机器学习数据分析聚类的早期糖尿病风险预测-毕业设计分享 完整代码数据可直接运行_基于某个数据集,利用所学机器学习算法(分类、回归、聚类等)实现数据的分析,论文糖

- 3spark—三层架构_控制层,服务层,持久层

- 4git上传遇到 “在签出前,请清理存储库工作树。”_在签出前,请清理仓库工作树。

- 5Java进阶笔记-日期与时间、包装类、正则表达式、Arrays类、常见算法、Lambda表达式枚举_java 正则匹配年月日时分秒

- 6MySQL之复制(十)

- 7C++ STL之queue详解_c++ stl queue

- 8linux部署yolov5_linux yolov5

- 9等保测评2.0——机房的安全物理环境_等保2.0对静电地板的要求

- 102024年最全【数据结构与算法】链表2W字终极无敌总结

xilinx7系列FPGA上电flash模式选择,及CFGBVS管脚电平选择

赞

踩

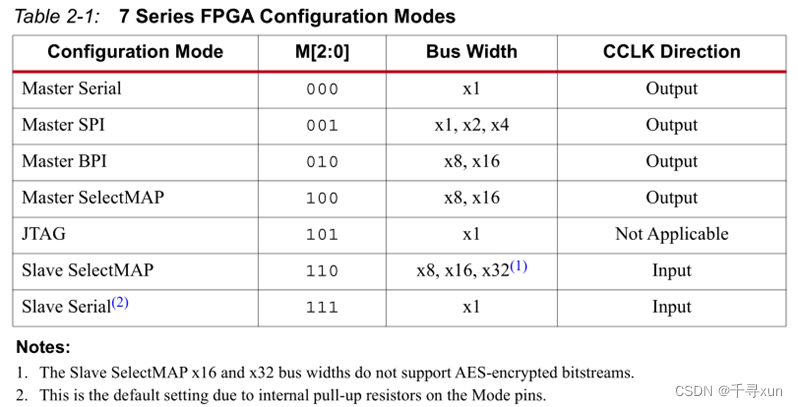

xilinx7系列FPGA上电flash模式选择,主要是控制mode管脚电平。详情见下图:

若FPGA配置flash为spi flash类型,mode【2:0】=001;FPGA配置flash为bpi flash类型,mode【2:0】=010。

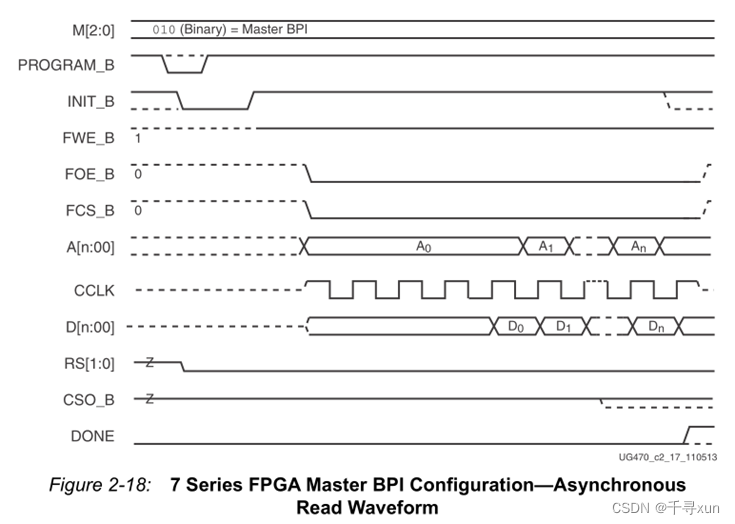

FPGA上电读bpi flash时序如图:

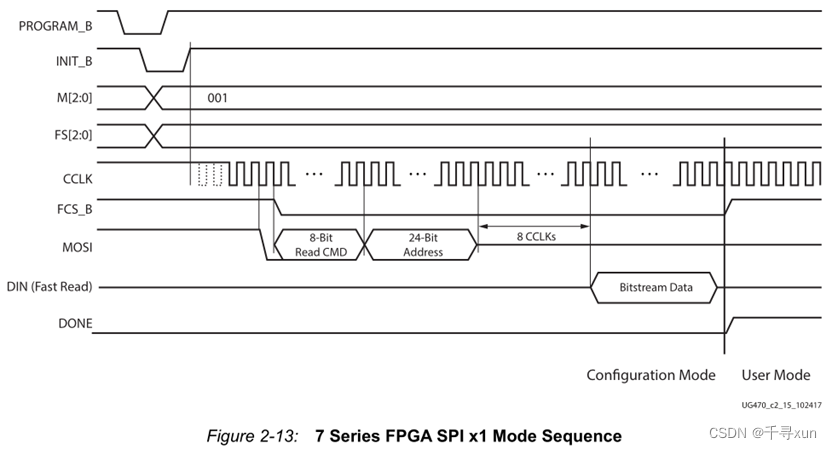

FPGA上电读spi flash x1模式时序如图:

Configuration Banks Voltage Select(CFGBVS)

配置组电压选择(CFGBVS)引脚必须设置为高或低,以便确定bank0中的引脚和bank14,bank15中的多功能引脚的I/O电压支持当它们在配置期间使用。CFGBVS是参考的逻辑输入引脚0和GND之间。当CFGBVS引脚为高电平时(例如,连接到V CCO_0电源3.3V或2.5V)。bank 0上的配置和JTAG I/O支持3.3V或2.5 V下的操作在配置期间和之后。当CFGBVS引脚为低(如,连接到GND)时bank0支持1.8V或1.5V下的操作。1.2V下不支持配置。

CFGBVS类似地控制bank 14和15上的电压容差,但仅在配置当CFGBVS为高时,bank 14和15上的配置I/O支持操作在配置期间为3.3V或2.5V。当CFGBVS引脚为低时,bank 14和15中的配置I/O在配置期间支持1.8V或1.5V的操作。

大概意思是V CCO_0电压为3.3V或2.5V,CFGBVS接高电平(1);V CCO_0电压为1.8V或1.5V时,CFGBVS接低电平(0)。

声明:以上内容均摘抄至xilinx用户手册ug470_7Series_Config。可自行去xilinx官网下载AMD Adaptive Computing Documentation Portal