- 1使用Neo4j和Langchain创建知识图谱_langchain neo4j

- 2【华为机试】2024年真题C卷(java)-最长子字符串的长度1_给你一个字符串s,字符串s首尾相连成一个环形

- 3常用服务器管理口IP及账号密码(持续更新)

- 4TCP协议-状态机_tcp状态机

- 5两数之和、三数之和、四数之和还不会写?看完此篇轻松掌握

- 6贪心算法(greedy algorithm,又称贪婪算法)详解(附例题)_贪心算法求边界线

- 7区块链技术及实际应用_区块链技术 运用

- 8UPF里面设置的power switch和powerswitch.tcl设置的power switch有什么区别?_upf中的power switch

- 9浅谈对大数据技术的发展趋势_大数据技术的发展方向

- 10微信小程序 wx.getFileSystemManager().saveFile的[读取文件/文件夹警告] 无法读取报错

彻底搞懂FPGA配置_fpga nconfig

赞

踩

近期通过Chipyard平台生成自定义的Rocket-chip处理器后,对怎么上板产生了疑惑,牵扯一些SOC、FPGA的知识不太熟练,故写此文章记录一下对FPGA配置过程的理解。

何谓芯片?

芯片的本质就是半导体+集成电路。

- 按处理信号方式可分为模拟芯片和数字芯片

- 按设计理念可分为通用芯片和专用芯片

- 按应用领域可分为航天级芯片、汽车级芯片,工业级芯片和商业级芯片

- 按应用功能角度可分为处理器芯片(CPU,GPU,DSP,MCU)、存储芯片(SRAM,DRAM,ROM,Flash)、传感器、电源芯片(PMU)、通信芯片(蓝牙、WIFI)和接口芯片

- ……

FPGA是怎么配置的?

FPGA是基于SRAM的架构。SRAM是静态随机存取存储器,通电后,数据可以保持不变;断电后,数据会消失。FPGA重新上电后,需要重新写入配置数据(即所谓的bit流)。根据bit流载入方式的不同,可分为两大类:

- 通过JTAG直接下载到FPGA中,每次重新上电都需要再下载一遍。(JTAG配置模式)

- 提前将配置数据存储在外部非易失存储器(例如Flash)中,上电后自动加载到FPGA中。

- 更详细的分类请见这篇文章XILINX 7系列FPGA_配置篇 - 知乎 (zhihu.com)

FPGA上电以后首先进入配置模式(configuration),在最后一个配置数据载入到FPGA以后,进入初始化模式(initialization),在初始化完成后进入用户模式(user-mode)。在配置模式和初始化模式下,FPGA的用户I/O处于高阻态(或内部弱上拉状态),当进入用户模式下,用户I/O就按照用户设计的功能工作。

一个器件完整的配置过程将经历复位、配置和初始化等3个过程。FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

所以配置模式取决于配置模式管脚的信号状态。

配置模式怎么设置?

Vivado设计过程中生成的bit流文件需要通过特定的配置引脚导入到FPGA中。专用配置引脚上的不同电压级别决定了不同的配置模式。可选的配置模式有:

- Master SPI x1/x2/x4

- Master Serial

- Slave Serial

- Master BPI-Up x8/x16

- Slave SelectMap x8/x16/x32

- JTAG/Boundary Scan

- Master SelectMap x8/x16

不管是哪种配置模式,配置数据都是存储在FPGA中的CMOS锁存器中,每次掉电后数据都会丢失,上电之后重新配置。但是选择一个片外存储器如SPI Flash存储配置数据,并设置相应的配置模式,上电后可以自动配置FPGA。

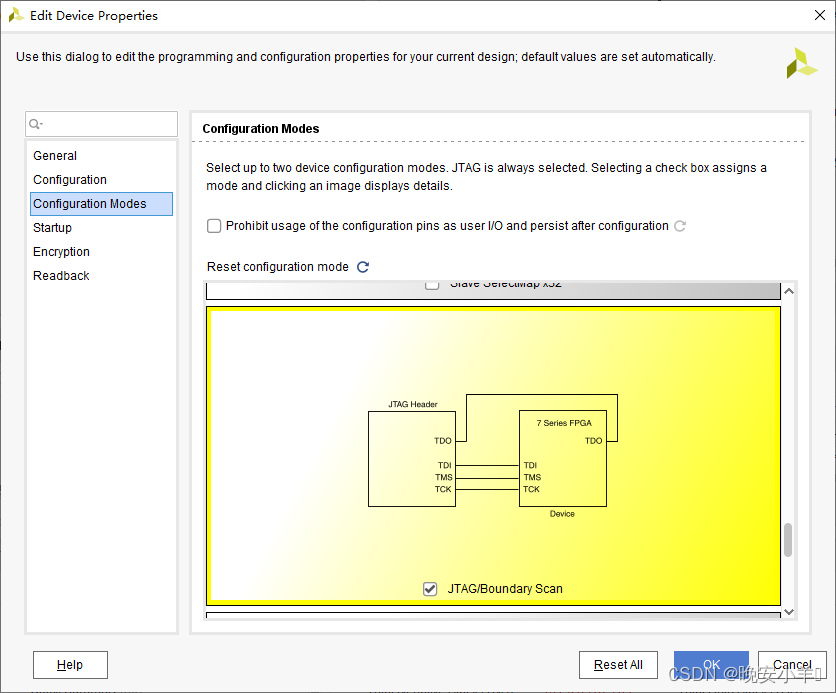

打开Vivado,运行SYNTHESIS -> IMPLEMENTATION,需要点击 Open Implemented Design,打开之后,再看左上角Tools菜单栏会发现有Edit Device Properties选项

在Configuration Modes标签中选择配置模式,可以选择多个,并且JTAG作为最基本的配置模式总会被选中。

设置配置模式会创建约束,自动添加到约束文件的末尾。

- //这条语句是选择配置模式后生成的

- set_property CONFIG_MODE <configuration_mode> [current_design]

-

-

- //这条语句是选中"Prohibit usage of the configuration pins as user I/O and persist after configuration"才会生成的

- set_property BITSTREAM.CONFIG.PERSIST YES [current_design]

-

- //设置bank电压,这两条语句要与硬件设计相符。比如,当使用JTAG配置模式时,CFGBVS设置为GND,CONFIG_VOLTAGE就必须设置为1.8

- set_property CFGBVS GND [current_design]

- set_property CONFIG_VOLTAGE 1.8 [current_design]