热门标签

热门文章

- 1深入了解:Kubernetes pod状态出现CrashLoopBackOff 的原因

- 2测试计划包括哪些内容?目的和意义是什么?_软件测试计划

- 3Datasophon基于dinky1.0.1升级到dinky1.0.2_dinky 1.0.2

- 4Beats:使用 Filebeat 从 Python 应用程序中提取日志_python filebeat

- 5从盘古开天辟地教你使用yolov5(一万六千字)_yolov5使用

- 6【surfaceflinger源码分析】surfaceflinger进程的消息驱动模型_surfaceflinger 源码分析

- 7vue 单元测试_vue单元测试

- 8PicGo搭建个人图床_思源笔记 图床

- 9Python3 async def和@asyncio.coroutine的区别

- 10MySQL 8.0.34(x64)安装笔记_mysql-8.0.34-winx64安装

当前位置: article > 正文

zynq PS到PL交互方案设计|学习笔记_zynq7000 设计 ps pl

作者:从前慢现在也慢 | 2024-07-15 18:55:49

赞

踩

zynq7000 设计 ps pl

此方案经zynq7000、MPSOC验证,详细记录下来以供温习,如有错误请指正,欢迎讨论。

一·背景

资源板卡内部由Zynq芯片实现对外部FPGA芯片再到各外设模块(如ADC\DAC等)的控制。

在资源板卡功能验证调试阶段,考虑到开发便利性及时效性,需要通过Zynq芯片的PS侧(即ARM)与PL侧交互,实现指令分发及数据流传输。

二·需求分析

- 交互内容:如指令传输和数据传输;

- 交互条件:如PL侧是否处于空闲或者忙碌状态;

- 交互生效:何时触发交互内容生效至外设或者PL内部;

- 异常处理:当通信出现异常时,预留全局复位机制使PL复位至某初始化状态。

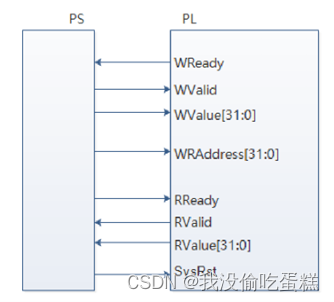

三·指令传输详情

| 信号 | 位宽 | 方向(相对PL) | 描述 | 有效值 |

| WReady | 1 | output | PL准备好,允许PS写入 | 高电平 |

| WValid | 1 | input | 指示寄存器地址和数据均有效,触发指令 | 上升沿写有效 |

| WValue | 32 | input | 待写入寄存器的值 | |

| WRaddress | 32 | input | 待写寄存器的地址 | |

| RReady | 1 | input | PS准备好,允许接受PL侧数据 | 上升沿读有效,下降沿读完毕 |

| RValid | 1 | output | 指示RValue有效信号 | 高电平 |

| RValue | 32 | output | 回传数据 | |

| SysRst | 1 | input | 复位信号 | 上升沿有效 |

NOTE:因为PS侧属于CPU,涉及到操作系统时间片调度问题,故PS侧程序运行一条语句大多在微秒级。如果PL侧的FPGA将WReady信号或者RValid信号设置为边沿有效,PS侧是无法保证能识别到有效信号,所以将WReady和RValid信号设置为电平有效。

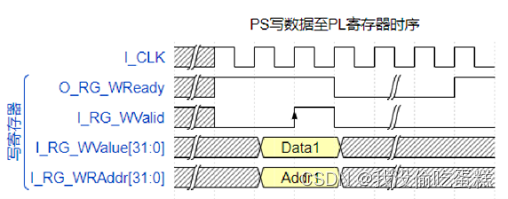

四·写寄存器时序

写寄存器时序图如下:

- 说明: PL侧IDLE状态WReady常保持高,PS侧IDLE状态WValid常保持低

- 注意: 在写期间,PL侧如果WReady拉低,要记得把PL侧的RValid信号拉低。

-

- Step1. PS将待写寄存器地址赋值给WRAddress

- Step2. PS将待写寄存器数据赋值给WValue

- Step3. PS检测WReady信号是否为高,如果不为高,持续检测,超时等待

- Step4. PS检测WReady信号为高后,拉高WValid信号,再拉低WValid信号

- Step5. PL接收到PS侧的WValid上升沿信号后,获取有效的待写入寄存器的地址和数据

- Step6. PL拉低WReady信号,执行寄存器所对应的业务(业务处理过程可能会在多个Tickling执行完)

- Step7. PL执行完业务后,拉高WReady信号,等待下次指令传输

- Step8. Done.

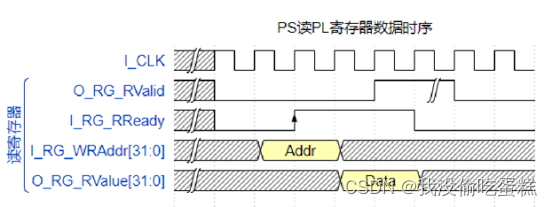

五·读寄存器时序

读寄存器时序图如下:

- 说明: PL侧IDLE状态RValid常保持低,PS侧IDLE状态RReady常保持低

- 注意: PL执行读业务时,WReady信号立刻拉高。

-

- Step1. PS将待读寄存器地址赋值给WRAddress;同时,拉高RReady信号

- Step2. PL执行读业务逻辑,更新待读寄存器内容,并将待读寄存器内容赋值给RValue

- Step3. PL检测如果RReady信号为高,则拉高RValid信号

- Step4. PS检测RValid信号是否为高,如果不为高,持续检测,超时等待

- Step5. PS检测RValid信号为高后,读取RValue数据

- Step6. PS读取完数据后,拉低RReady信号,进入IDEL状态

- Step7. PL检测到ReadReady信号的下降沿后,拉低RValid信号,拉高WReady信号,进入IDEL状态

- Step8. Done.

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/830675

推荐阅读

相关标签