热门标签

热门文章

- 1第三章:AI大模型的开发环境搭建3.1 Python编程基础3.1.2 Python库与模块_python 大语言模型 开发

- 27.1 数据库设计概述

- 3Visual Studio Code使用问题_若您正以管理员身份运行 visual studio code 用户范围的安装,更新功能会被禁用。

- 4pandas 用read_csv读取txt文件时,部分行丢失_pandas读取txt文件不全

- 5linux相对于windows环境为啥相对来说更加具有安全性_对于普通用户linux和windows哪个安全

- 6Linux权限有哪些?500代表什么意思?_权限500啥意思

- 7Redis主从配置

- 8人工智能火爆了!阿里机器人都会批改作文了!苹果开源机器学习框架;360 开源深度学习平台 XLearning;

- 9【卡车无人机协同】基于遗传算法卡车和两架无人机配送路径规划附matlab代码_卡车支持无人机运行配送

- 10NOIP 边权差值最小的生成树(小数据)_最小边权差生成树

当前位置: article > 正文

基于FPGA的fir滤波器设计verilog实现

作者:你好赵伟 | 2024-07-18 14:00:15

赞

踩

基于FPGA的fir滤波器设计verilog实现

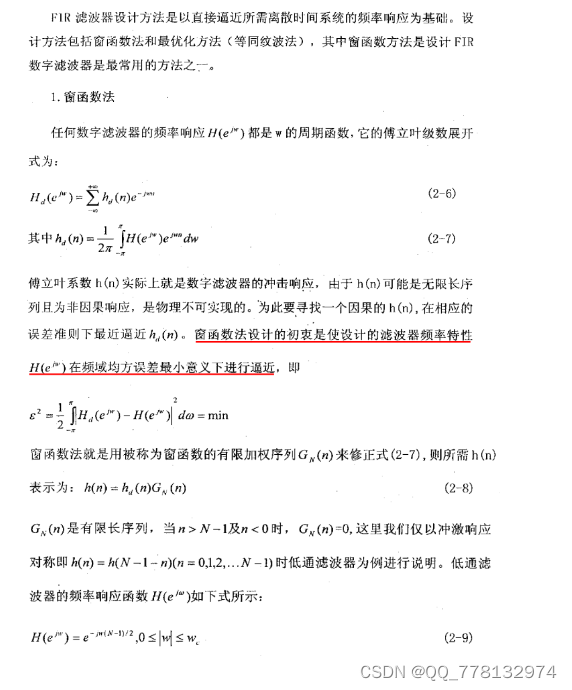

FIR滤波器的设计方法

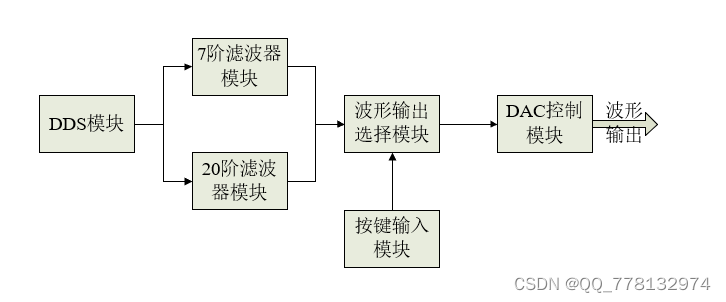

设计框架

设计的滤波器的采样频率为100K,截至频率为20K。

通过一个DDS产生两个正弦波,一个为1K的正弦波幅值较大,另一个为21K的正弦波幅值较小,然后将幅值较小的正弦波叠加到幅值较大的正弦波上。这样就产生含有高次谐波的正弦波,最后就是将该正弦波(其实都已经失真了)送往两个FIR滤波器中进行处理。

FIR8阶滤波器的采样频率为100K,截至频率为20K,通过Matlab软件导出需要的滤波器系数:0.009、0.048、0.164、0.279、0.279、0.164、0.048、0.009。因为该滤波器为线性相位滤波器,并且为偶对称滤波器。 工程设计中采用线性相位结构的滤波器。

Matlab软件导出需要的滤波器系数过程

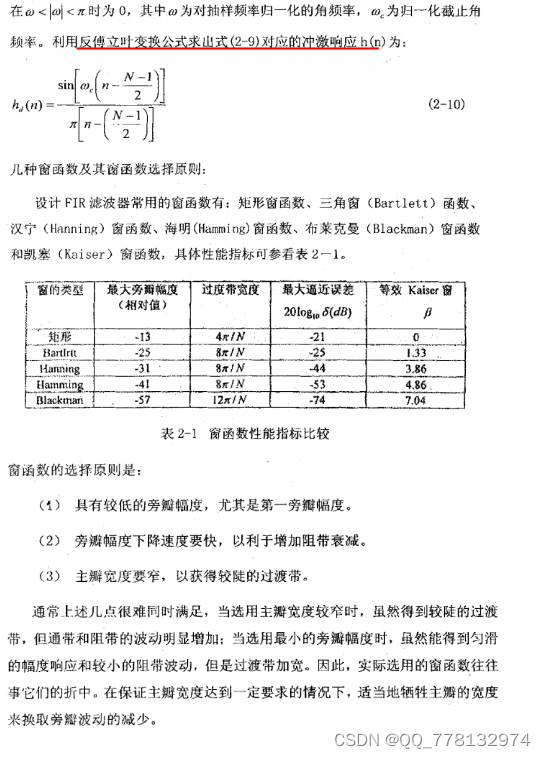

采用Matlab软件求取滤波器系数时,要先确定好截止频率、采样频率和滤波器系数,还有就是采用哪种窗函数,这里采用Matlab自带的两个函数,分别为:Fir1和Fir2,Fir1为窗函数设计方法,Fir2为任意频率响应的各种加窗FIR滤波器。在该设计中我们采用的是Fir1求取滤波器系数。过程如下:

打开Matlab软件

在指令窗口中键入ÿ

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/846021

推荐阅读

相关标签