热门标签

热门文章

- 1《python深度学习》可视化热力图_pytcv2.applycolormap热力图

- 2毕业设计课题:学生成绩管理系统,基于java+SSM+mysql

- 32、ospf邻居到邻接建立_ospf邻接关系建立过程中这些报文如何进行交互

- 4《Effective Java》:Java编程圣经,Bloch大师亲授高效优雅编程之道!_josh bloch

- 5爆火!开源多模态大模型在手机端进行本地部署!_多模态大模型 本地部署

- 6Flink1.12-2021黑马 8 Flink高级特性和新特性_黑马flink

- 7VS2013 预处理器定义 设置问题

- 8opencv人脸识别实战1:初始化及录入人脸(PyCharm实现)_config.txt人脸识别

- 9Stable Diffusion 图生图-蒙版重绘,Controlnet未生效的一个场景_controlnet 不生效

- 10第五章重采样方法

当前位置: article > 正文

多路竞赛抢答器的设计VHDL代码Quartus仿真_基于vhdl的抢答器的设计

作者:天景科技苑 | 2024-07-01 11:31:25

赞

踩

基于vhdl的抢答器的设计

名称:多路竞赛抢答器的设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

多路竞赛抢答器的设计与实现

实验目的:设计并制作一个多路竞赛抢答器(至少8路)

实验内容:抢答器是为智力竞赛参赛者答题时进行抢答而设计的一种优先判决器电路,竞赛者可以分为若干组,抢答时各组对主持人提出的问题要在最短的时间内做出判断,并按下抢答按键回答问题。当第一个人按下按键后,则在显示器上显示该组的号码,同时电路将其他各组按键封锁,使其不起作用。若抢答时间内无人抢答,警报器发出警报。回答完问题后,由主持人将所有按键恢复,重新开始下一轮抢答。

1. 工程文件

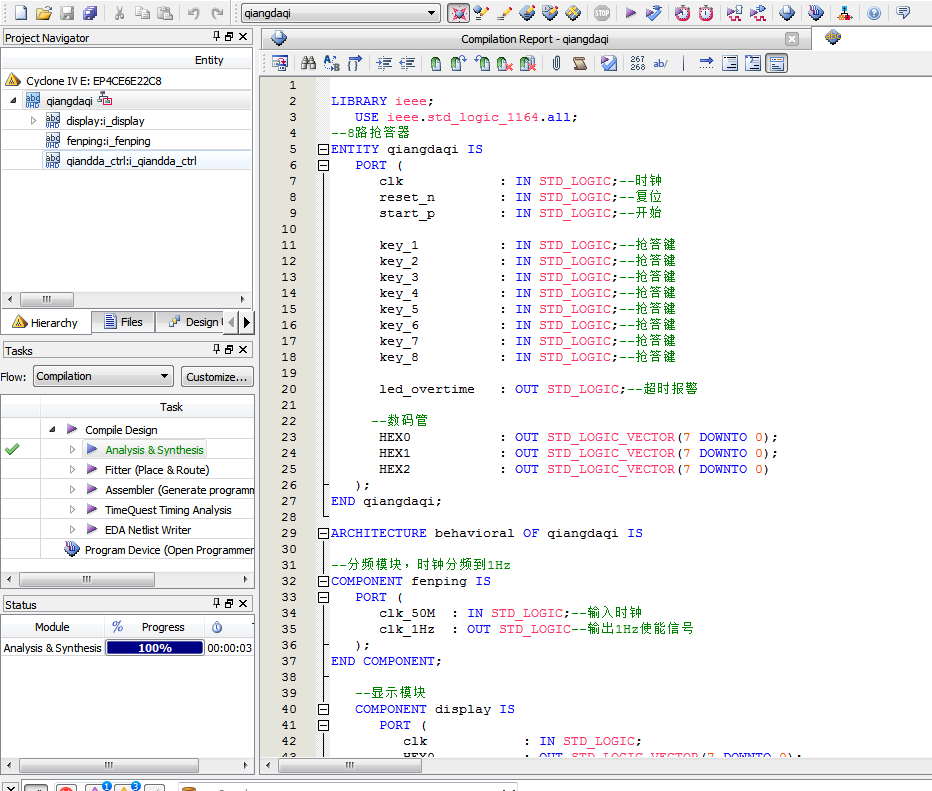

2. 程序文件

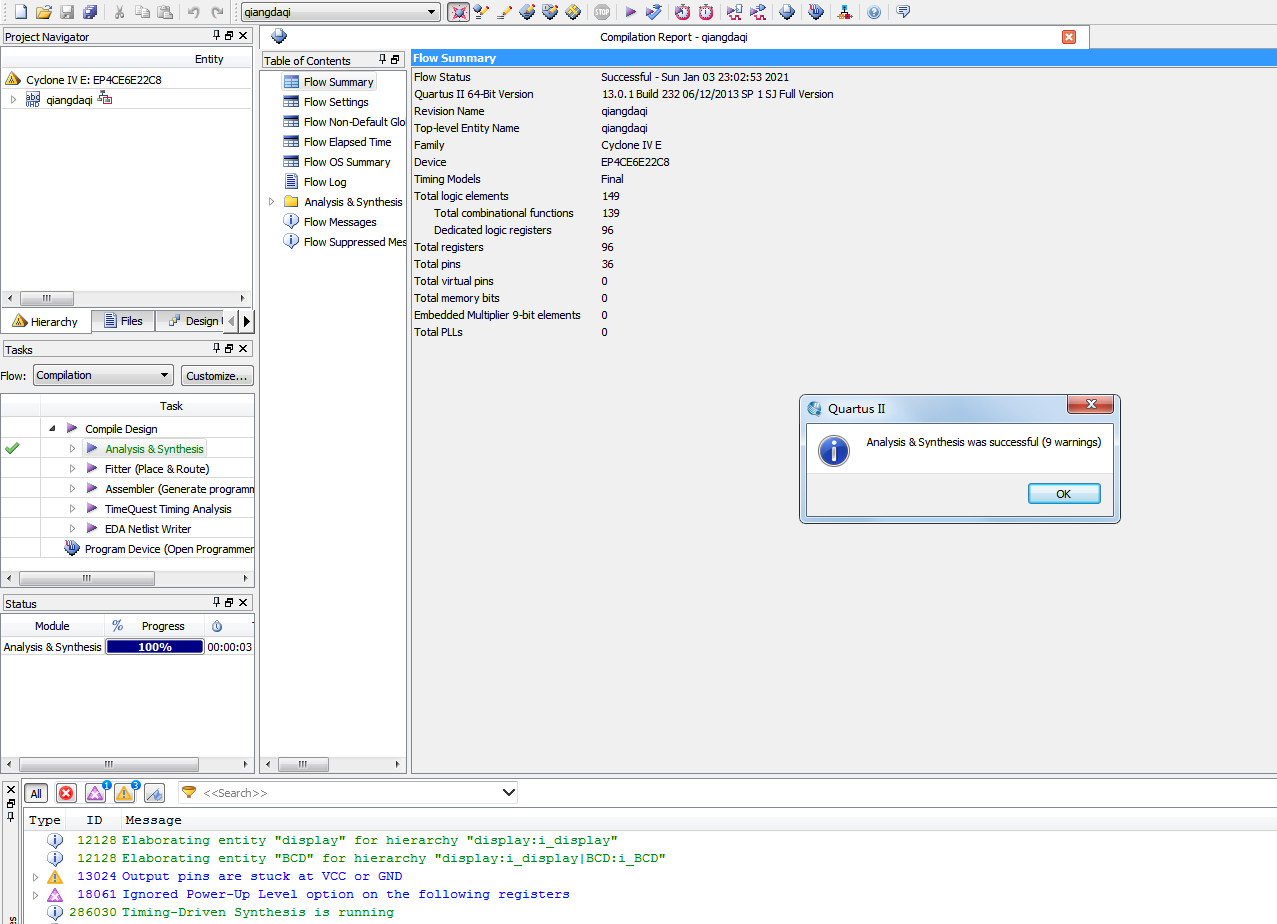

3. 程序编译

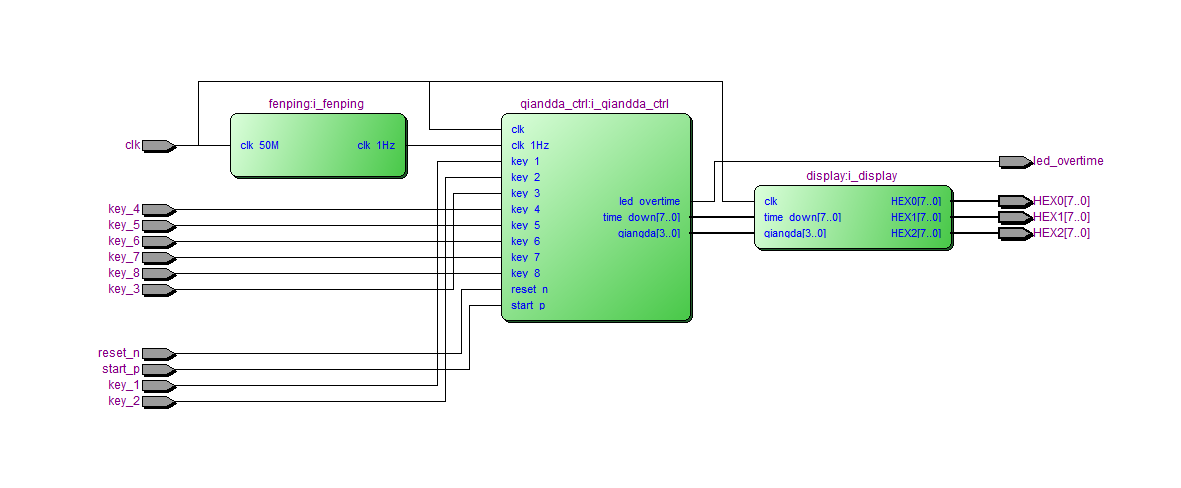

4. RTL图

5. 仿真图

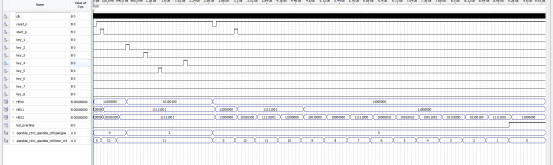

5.1 整体仿真

设置抢答时间为12秒内,若抢答时间内无人抢答,警报器发出警报。

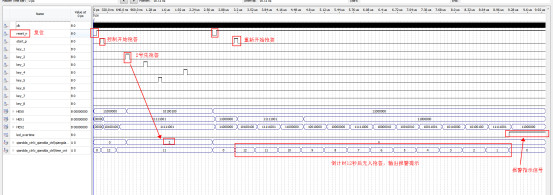

5.2 抢答控制模块

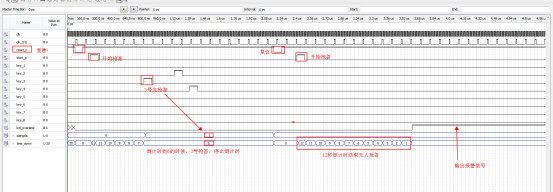

5.3 分频模块

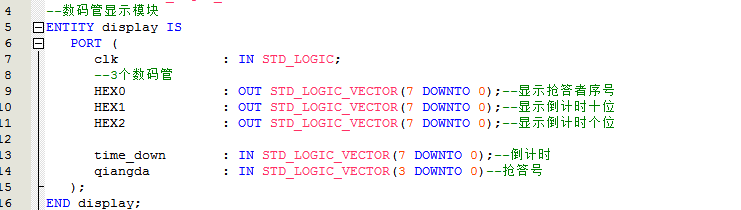

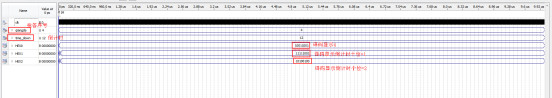

5.4 显示模块

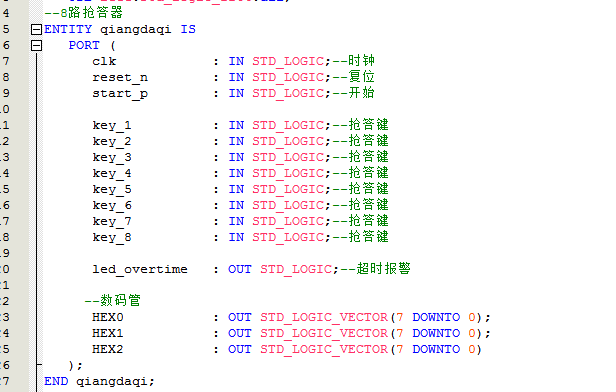

部分代码展示:

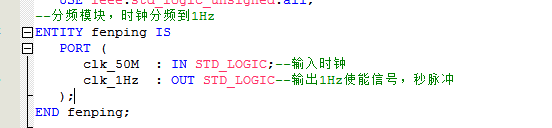

LIBRARY ieee; USE ieee.std_logic_1164.all; --8路抢答器 ENTITY qiangdaqi IS PORT ( clk : IN STD_LOGIC;--时钟 reset_n : IN STD_LOGIC;--复位 start_p : IN STD_LOGIC;--开始 key_1 : IN STD_LOGIC;--抢答键1 key_2 : IN STD_LOGIC;--抢答键2 key_3 : IN STD_LOGIC;--抢答键3 key_4 : IN STD_LOGIC;--抢答键4 key_5 : IN STD_LOGIC;--抢答键5 key_6 : IN STD_LOGIC;--抢答键6 key_7 : IN STD_LOGIC;--抢答键7 key_8 : IN STD_LOGIC;--抢答键8 led_overtime : OUT STD_LOGIC;--超时报警 --数码管 HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END qiangdaqi; ARCHITECTURE behavioral OF qiangdaqi IS --分频模块,时钟分频到1Hz COMPONENT fenping IS PORT ( clk_50M : IN STD_LOGIC;--输入时钟 clk_1Hz : OUT STD_LOGIC--输出1Hz使能信号 ); END COMPONENT; --显示模块 COMPONENT display IS PORT ( clk : IN STD_LOGIC; HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); time_down : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--倒计时 qiangda : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; --抢答控制模块 COMPONENT qiandda_ctrl IS PORT ( clk : IN STD_LOGIC;--时钟 clk_1Hz : IN STD_LOGIC;--1Hz时钟 reset_n : IN STD_LOGIC;--复位 start_p : IN STD_LOGIC;--开始 --8个抢答按键 key_1 : IN STD_LOGIC; key_2 : IN STD_LOGIC; key_3 : IN STD_LOGIC; key_4 : IN STD_LOGIC; key_5 : IN STD_LOGIC; key_6 : IN STD_LOGIC; key_7 : IN STD_LOGIC; key_8 : IN STD_LOGIC; led_overtime : OUT STD_LOGIC;--超时报警 time_down : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--倒计时 qiangda : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--抢答号 ); END COMPONENT; SIGNAL qiangda : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL clk_1Hz: STD_LOGIC; SIGNAL time_down : STD_LOGIC_VECTOR(7 DOWNTO 0);--倒计时 BEGIN --调用分频模块,时钟分频到1Hz i_fenping: fenping PORT MAP ( clk_50M => clk,--输入时钟 clk_1Hz => clk_1Hz--输出1Hz使能信号 ); --调用抢答控制模块 i_qiandda_ctrl : qiandda_ctrl PORT MAP ( clk => clk, clk_1Hz => clk_1Hz, reset_n => reset_n, start_p => start_p, key_1 => key_1, key_2 => key_2, key_3 => key_3, key_4 => key_4, key_5 => key_5, key_6 => key_6, key_7 => key_7, key_8 => key_8, led_overtime => led_overtime,--超时报警 time_down => time_down,--倒计时 qiangda => qiangda--抢答号 ); --调用显示模块 i_display : display PORT MAP ( clk => clk, time_down => time_down,--倒计时 qiangda => qiangda, HEX0 => HEX0, HEX1 => HEX1, HEX2 => HEX2 ); END behavioral;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:【wpsshop博客】

推荐阅读

相关标签