热门标签

热门文章

- 1Stable Diffusion WebUI 笔记本低显存无魔法本地安装使用(四)--- 安装和启动Stable Diffusion WebUI_stable diffusion web ui 社区

- 2NameNode内存生产配置探究_namenode占用的是什么内存

- 3新钛云服数字化转型服务案例入选Forrester报告!

- 440 个很有用的 Mac OS X Shell 脚本和终端命令_macbook xshell

- 5为什么要来CSDN_为什么要用csdn

- 6六、Git——提交版本管理

- 7开源AI项目:合同检查流程优化,提高工作效率与准确性_ai能够帮我们读懂合同吗

- 8Activity的启动流程详解_am strat启动activity

- 9糟糕程序员的7个通病,你中了几条?_程序员的性格通病

- 10Django3+Vue3进行前后端开发环境搭建_vue3 django

当前位置: article > 正文

野火A7学习第五次(时序逻辑相关)_时序延一拍会影响输出吗

作者:很楠不爱3 | 2024-05-05 04:07:13

赞

踩

时序延一拍会影响输出吗

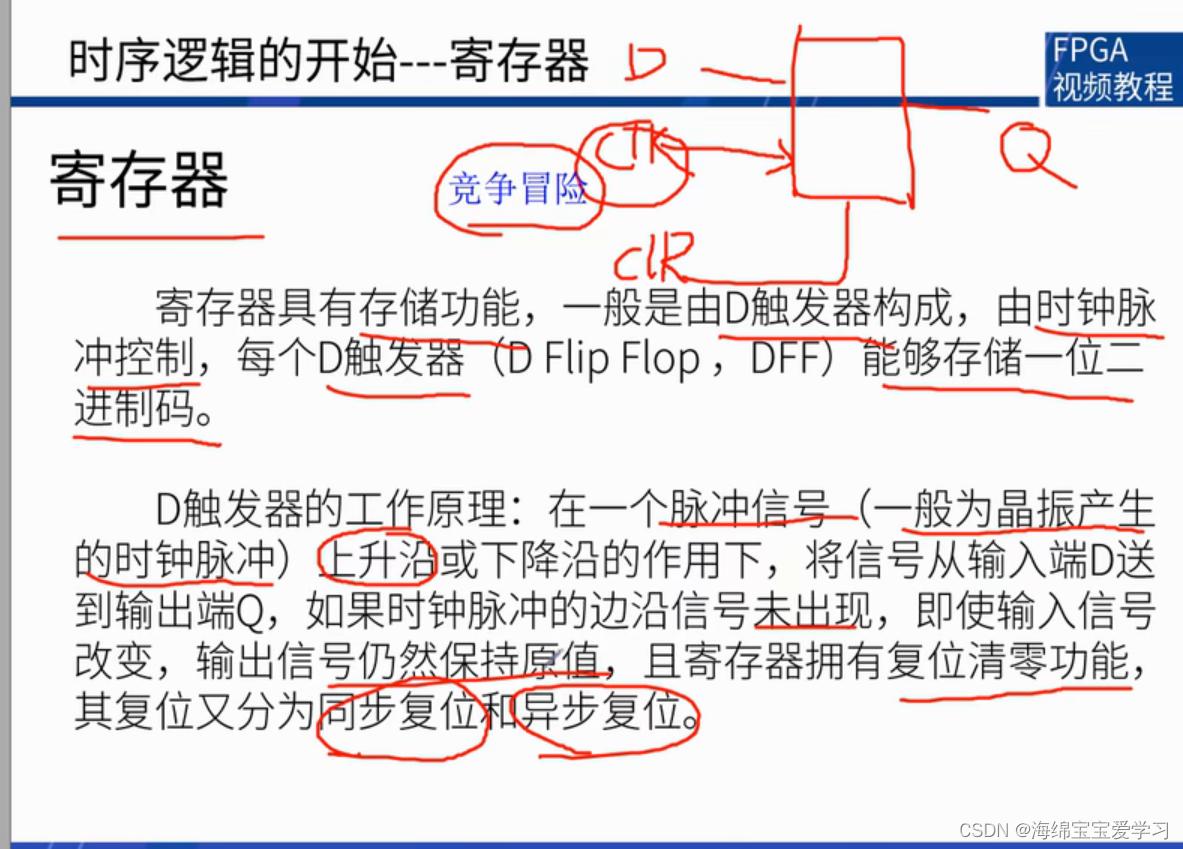

1 理论学习

1 组合逻辑最大的缺点就是存在竞争冒险(使电路存在不稳定的状态)

2 实战演练

使用按键控制LED灯

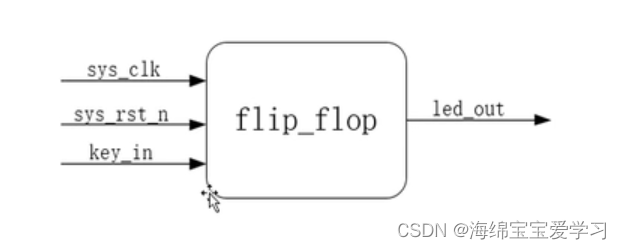

2.1 设计规划

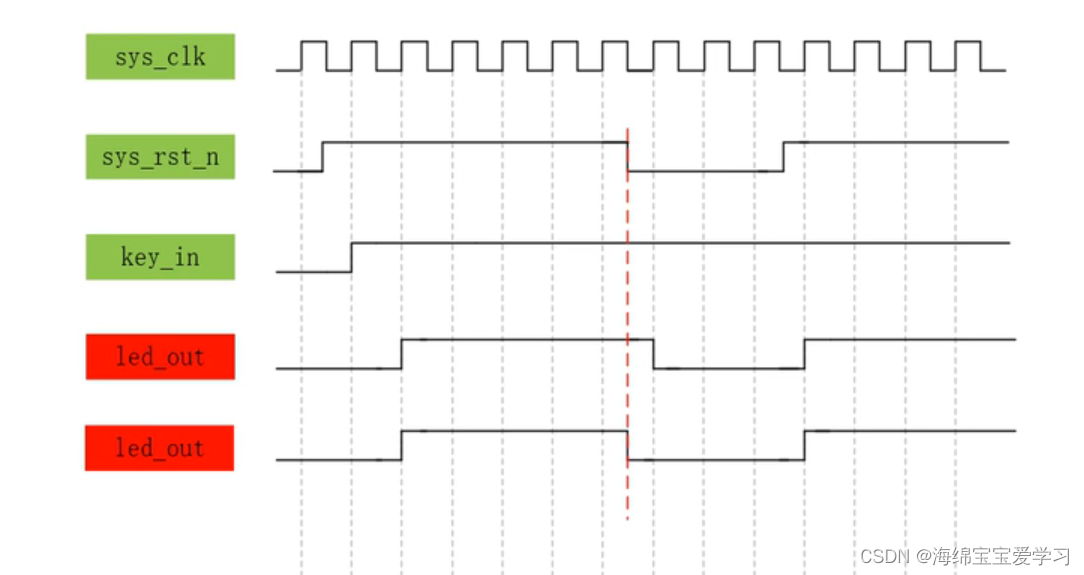

2.2 波形绘制

2.2.1 同步复位D触发器

只有时钟上升沿检测到有效才是有效的。

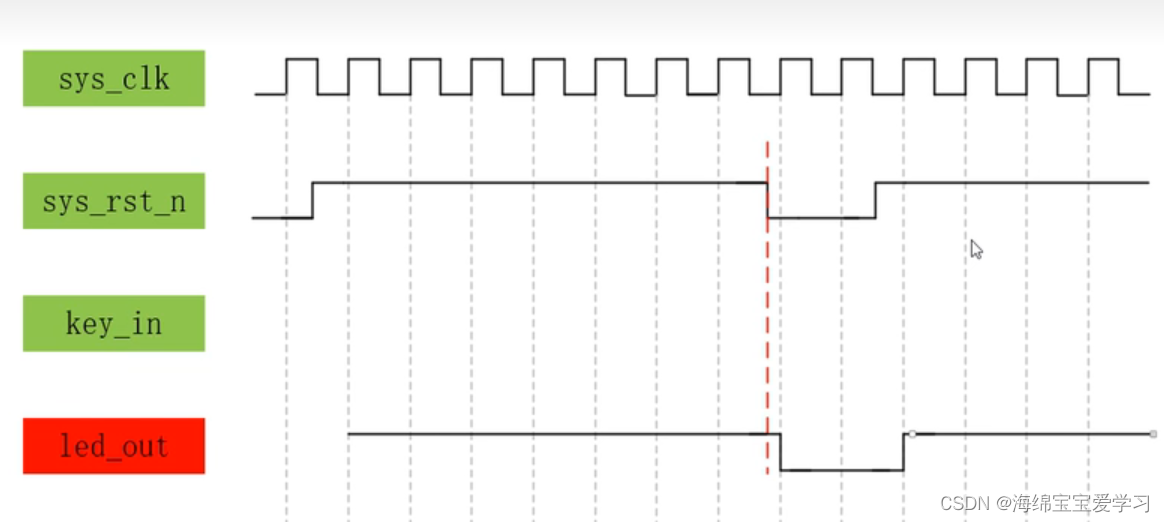

2.2.2 异步复位

寄存器的复位不管时钟上升沿来不来,只要触发就立即生效,但是后面复位信号的上升沿受到时钟的影响。异步复位 同步释放

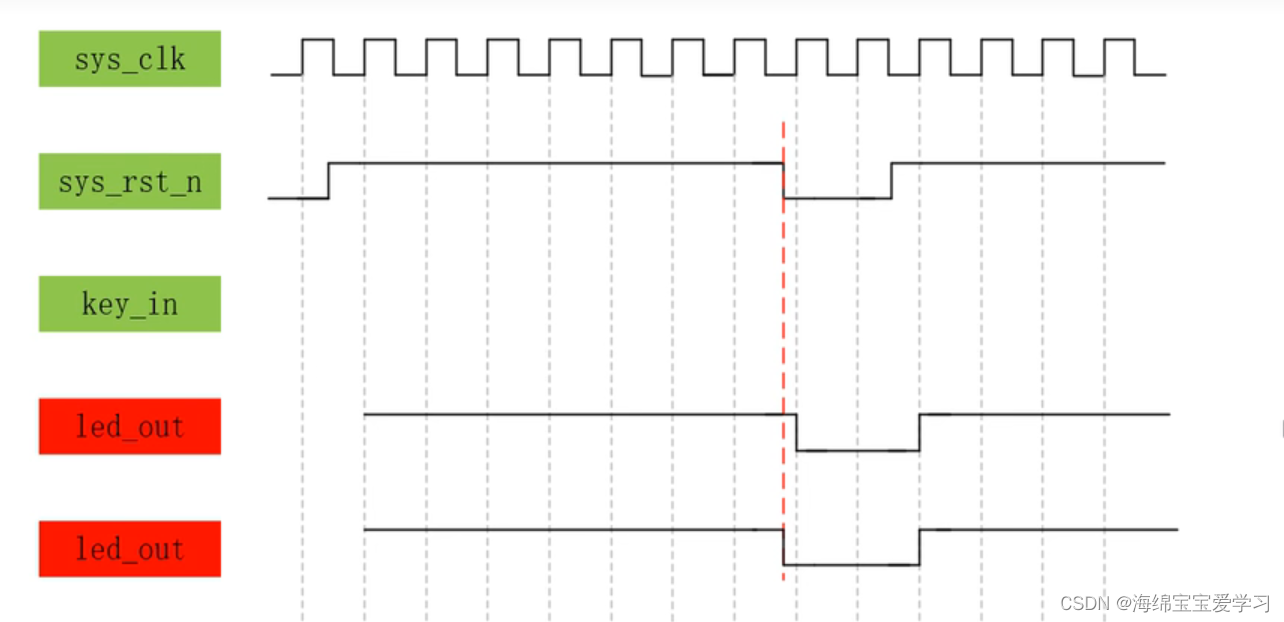

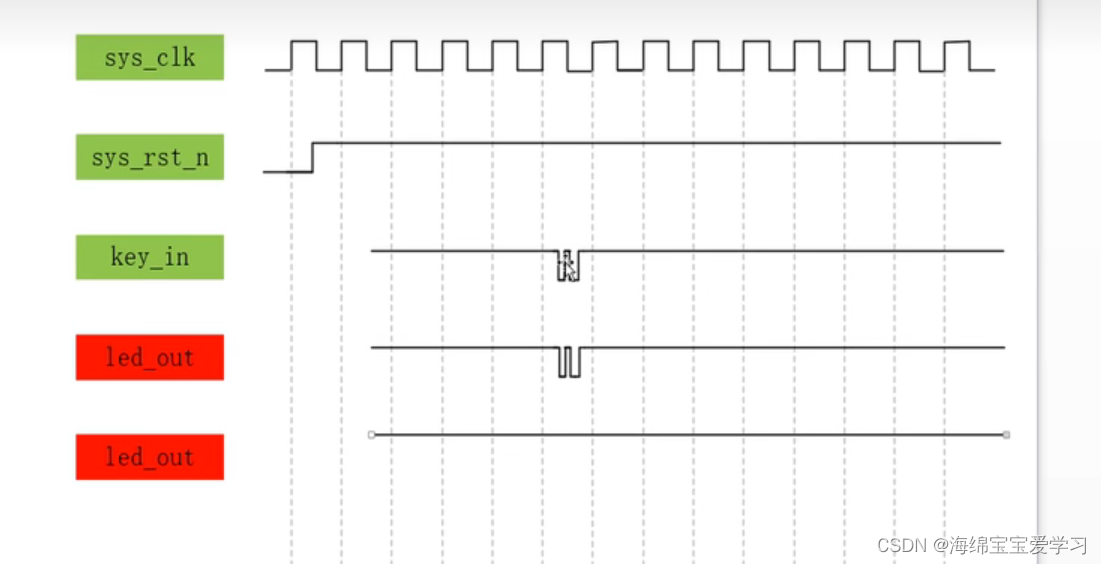

2.2.3 时序逻辑中可以滤除毛刺的现象

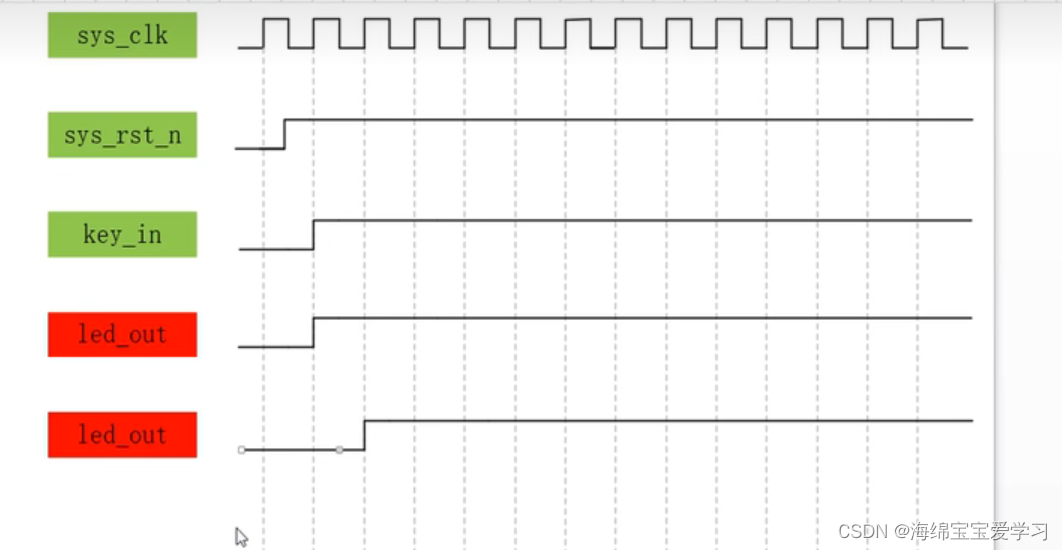

2.2.4 时序信号可以产生延迟一拍的效果

时序信号,默认的是时钟信号采集前一时刻的值。所以会出现延迟一拍的效果。

前面是同步复位,后面是异步复位。(异步复位,同步释放)

2.3 代码编写和调试

module flip_flop ( input wire sys_clk, input wire sys_rst_n, input wire key_in, output reg led_out ); always@(posedge sys_clk) // 同步复位 //always@(posedge sys_clk or negedge sys_clk_n) // 异步复位 if(sys_rst_n == 1'b0) led_out <= 1'b1; else led_out <= key_in; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

仿真代码:

`timescale 1ns/1ns module tb_flip_flop(); reg sys_clk; reg sys_rst_n; reg key_in; wire led_out; // 上电只执行一次 initial begin sys_clk = 1'b0; sys_rst_n <= 1'b0; key_in <= 1'b0; #20; sys_rst_n <= 1'b1; #210 sys_rst_n <= 1'b0; #40; sys_rst_n <= 1'b1; end always #10 sys_clk = ~sys_clk; always #20 key_in <= {$random} % 2; flip_flop flip_flop_inst ( .sys_clk(sys_clk), .sys_rst_n(sys_rst_n), .key_in(key_in), .led_out(led_out) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

声明:本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:【wpsshop博客】

推荐阅读

相关标签