- 1OpenAI安全系统负责人:从头构建视频生成扩散模型

- 2jieba分词与wordcloud词云_jieba和wordcloud制作词云

- 3免费,C++蓝桥杯比赛历年真题--第14届蓝桥杯省赛真题(含答案解析和代码)_第14届蓝桥杯大赛青少年组c++中级组省赛试题

- 4一文搞懂Stable Diffusion提示词,收藏这篇提示词合集就够了_stablediffusion提示词优先级

- 5解决selenium升级到版本 4.16后出现的问题: org/openqa/selenium/WebDriver 编译环境是55.0(jdk11),而运行环境为52.0( jdk8 )_selenium 4.16

- 6毕业设计——基于网络爬虫的电影数据可视化分析系统的设计与实现(综述+爬虫源码+web可视化展示源码)_爬虫可视化系统

- 7“新卷王”X-volution | 将卷积与自注意力进行高效集成,上交与华为海思提出了Xvolution_yvloution

- 8筛选十个免费商用图片网站,创作、壁纸、设计更加精彩,确定不来看看吗,赶快收藏起来吧_colorhub

- 9【ROS2安装记录】解决 curl: (7) Failed to connect to raw.githubusercontent.com port 443: Connection refused_ros2 curl key failed connect

- 10FreeRTOS的移植到STM32的多种方法_freertos移植stm32

FPGA之JESD204B接口——总体概要 实例上_jesd204b接口速率

赞

踩

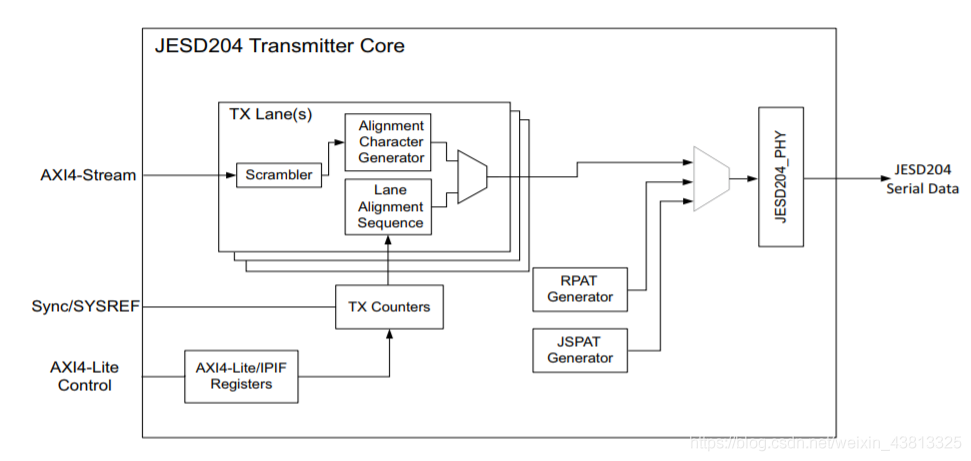

JESD204B IP CORE结构

JESD204B支持速率高达12.5Gbps,IPcore可以配置为发送端(如用于DAC)或接收端(如用于ADC),每个core支持1-8 lane数据,若要实现更高lane的操作需要通过multi cores实现。

JESD204B transmitter

主要包含以下功能模块

1、AXI4-STREAM数据流接口;

2、TX lane逻辑模块包括:

- 加扰;

- 插入对齐参数;

- ILAS序列生成;

3、TX计数器;

4、JESD204B PHY;

5、RPAT 生成器,用于测试模式;

6、JSPAT 生成器,用于测试模式;

7、AXI4-LITE管理接口和控制、状态寄存器,调试时使用;

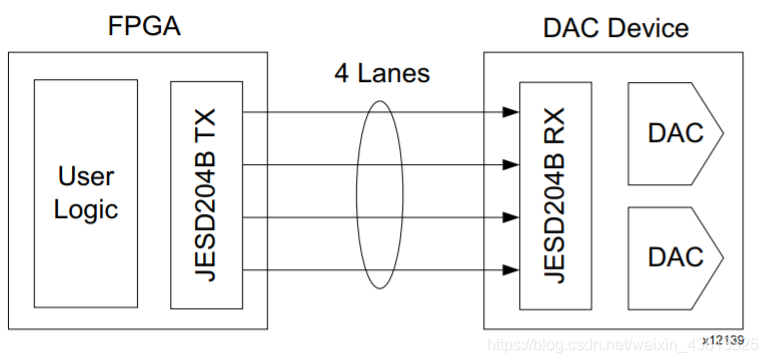

在逻辑设备和DAC之间,逻辑设备为JESD204B transmitter即发送端,DAC为JESD204B Receiver即接收端;在发送端,数据在传输层进行组帧,在数据链路层进行CGS、ILAS、数据传输等阶段。

1、在CGS阶段,接收端向发送端发起SYNC请求,然后发送端发送已知重复序列,当接收端检测到固定数量的K28.5后拉高SYNC,随后进入ILAS阶段。

2、ILAS阶段,在发端生成了初始通道对齐序列ILAS,主要用于对齐所有通道、验证链路参数等。

3、然后开始用户数据传输,最终数据将在物理层以固定速率将数据送入DAC。

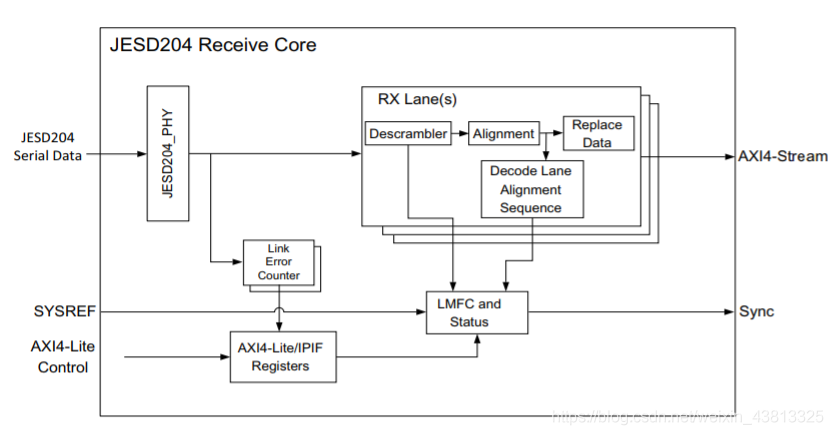

JESD204B Receiver

主要包含以下功能模块

1、AXI4-STREAM数据流接口;

2、RX lane逻辑包括:

- 捕捉ILA;

- 解扰;

- 对齐参数检测;

3、LMFC状态机;

4、JESD204B PHY;

5、通道错误计数器;

6、AXI4-LITE管理接口和控制、状态寄存器;

在逻辑设备和ADC之间,ADC为JESD204B transmitter即发送端,逻辑设备为JESD204B Receiver即接收端;在接收端,数据在物理层以一定速率接受数据,通过SYSREF对齐帧和多帧前沿时钟相位。在数据链路层进行CGS、ILAS、数据传输等阶段。

1、在CGS阶段,接收端向发送端发起SYNC请求,然后发送端发送已知重复序列,当接收端检测到固定数量的K28.5后拉高SYNC实现代码组同步。

2、ILAS(包含通道对齐字符和链路参数)阶段,在发端生成了初始通道对齐序列ILAS发送到收端,该序列主要用于对齐所有通道、验证链路参数等。

3、然后开始接受用户数据,最终数据将在传输层进行解帧。

三、JESD IPcore 调用

1、transmitter or receive:当发送数据时FPGA作为transmitter,如用于DAC、当接受数据时FPGA作为receiver,如用于ADC时。

1、transmitter or receive:当发送数据时FPGA作为transmitter,如用于DAC、当接受数据时FPGA作为receiver,如用于ADC时。

2、LMFC buffer:buffer容量要大于一个多帧数据容量,大于8xFxK。

F: 每帧中字节数

K:每个多帧中帧数

3、lanes:每个link中数据通道数。

4、pattern gen:用于测试模式

5、clocking:AXI4-LITE CLOCK

①ultrascale系列:10M < f < 200M;

②7 series系列:与shared logic有关,若shared logic in core AXI4时钟同DRP;若shared logic in example design AXI4时钟10M < f < 200M;

6、SYSREF sample:当SYSREF和核时钟异步时,下降沿采样提供良好的时钟裕量。

7、Drive core clk:可选输入,当refclk等于coreclk时或refclk不在规定范围时使用。

1、shared logic:时钟与shared logic有关,若shared logic in core AXI4时钟同DRP;若shared logic in example design AXI4时钟10M < f < 200M;

1、SYSREF状态。

2、SCR:加扰。

3、F:每帧中字节数。

4、K:每个多帧中帧数,0-32可选,一般为32。

5、RE-SYNC:是否需求sysref 。

1、transmitter type:收发器类型。

2、lane rate:根据ADC/DAC配置计算得到。

3、ref clk:收发器参考时钟,可选。

4、PLL类型:quad锁相环和通道锁相环可选QPLL/CPLL。

5、DRP时钟:若shared logic in core AXI4时钟同DRP,shared logic in example DRP可选。

6、debug:用于调试

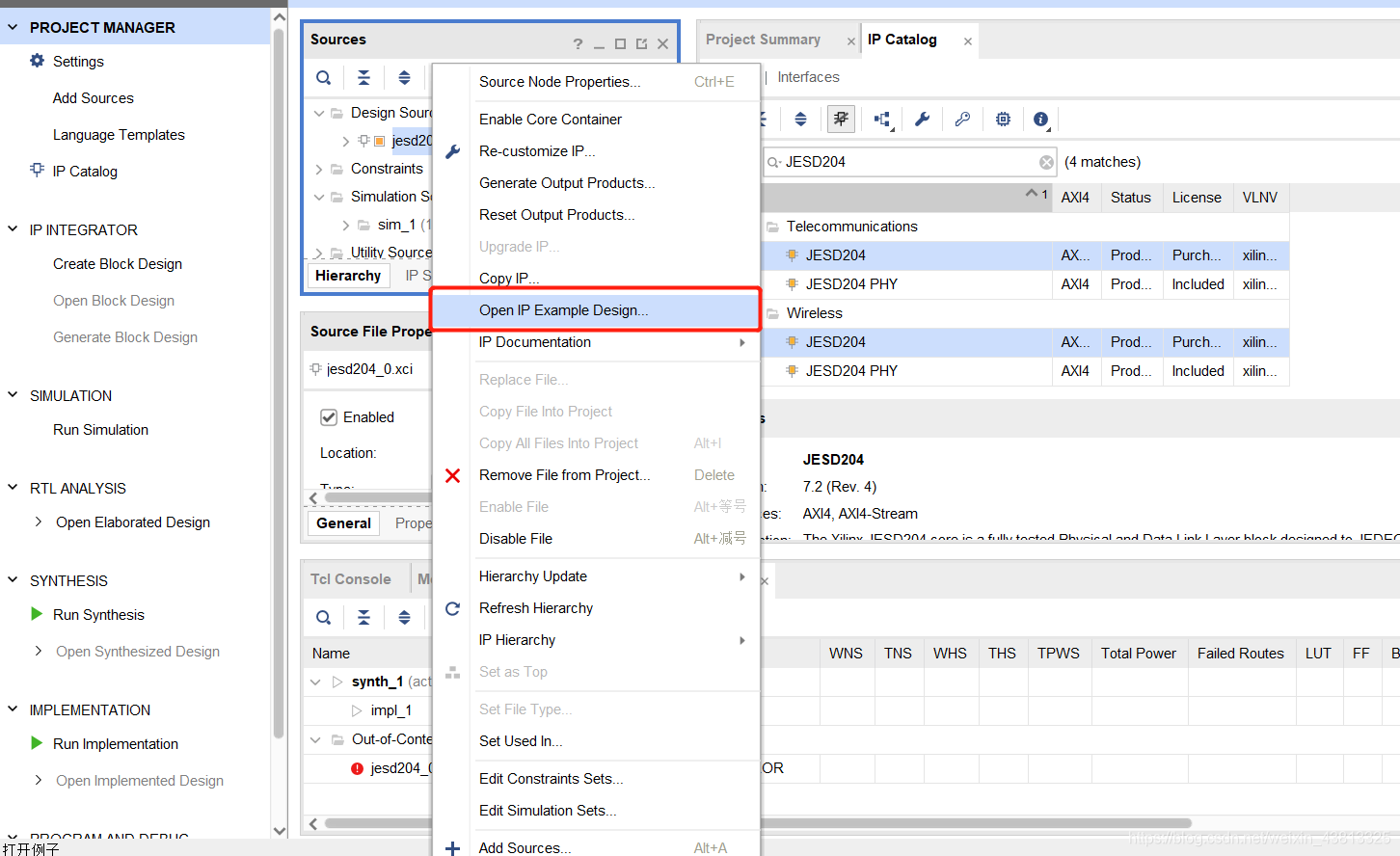

基于example design实现设计

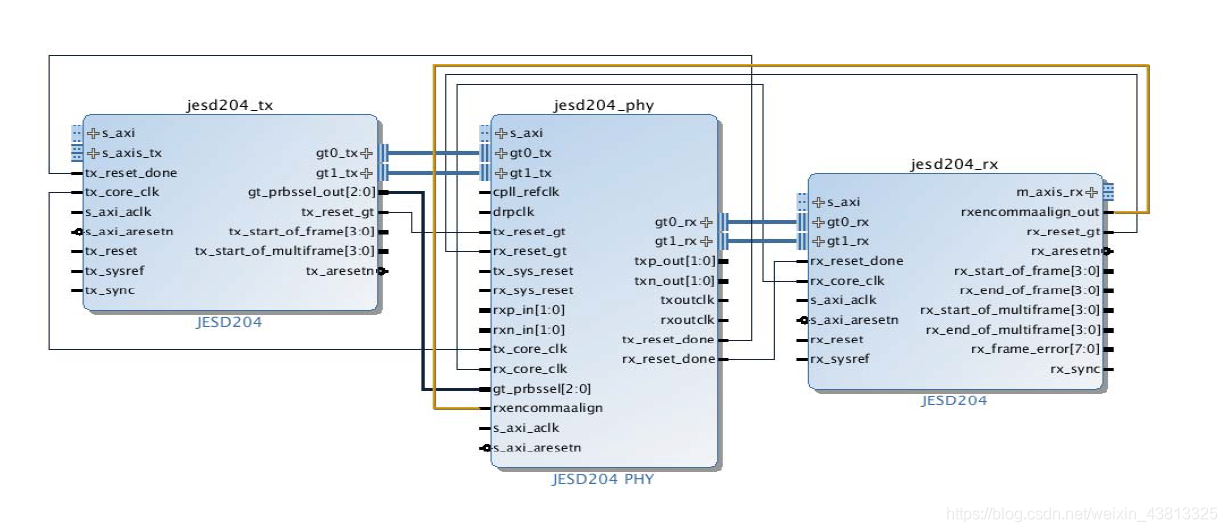

example程序框图

链路传输需要PHY和204B IPcore,例如ADC和FPGA应用,在example design中已经将数据通过PHY和204B core接收,从AXI4-STREAM中输出数据流,那么剩下需要做的就是将数据解帧,实现数据和采样值之间映射。

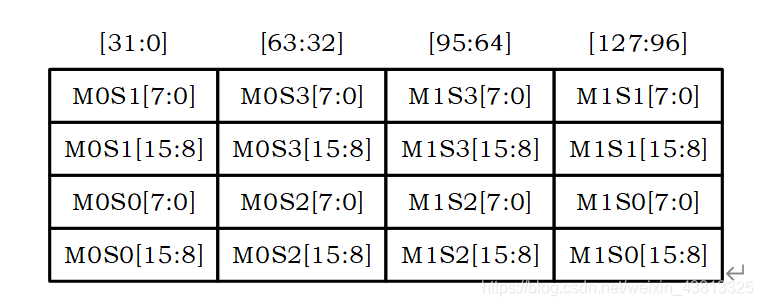

FPGA接收数据解帧:例如根据ADS54J60手册,JESD204B参数配置为:L=4、M=2、F=4、S=4、N=16、N’=16、K=32。让Fs=980M,那么lane rate计算得9.8Gbps,core clk=lane rete/40=245M,GTH clk=245M。 其输出数据帧格式如下图所示。加粗样式

JESD204B的IPcore输出为每个Lane输出32bit并行数据,因此4个Lane的情况下,JESD204B输出数据的位宽为128bit。因此每个245MHz core时钟下,输出的数据格式如下图所示。