- 1信息系统项目管理师 -- 目录_信息系统项目管理师目录

- 2WIN2K3&WINXP系统服务详解_aelookupsvc是什么服务

- 3编辑任何东西_editanything使用

- 4vue 使用axios发送请求或带参数的请求_axios同时传递请求体和参数

- 5递归--八皇后问题_用递归求解八(n)皇后问题。说明:在8*8格的国际象棋上(图6-1)摆放八个皇后,使其不

- 6Maven本地仓库安装jar包_maven install

- 7mysql 多表查询 优化_MySql多表查询优化

- 8Pycharm 通过 SVN 直接管理控制代码,原来这么方便又高级!_pycharm svn管理

- 9如何成为AI时代下的10倍程序员

- 10利用MongoDB构建现代支付系统|附《利用AI在支付领域的优势》报告下载_mongodb支付

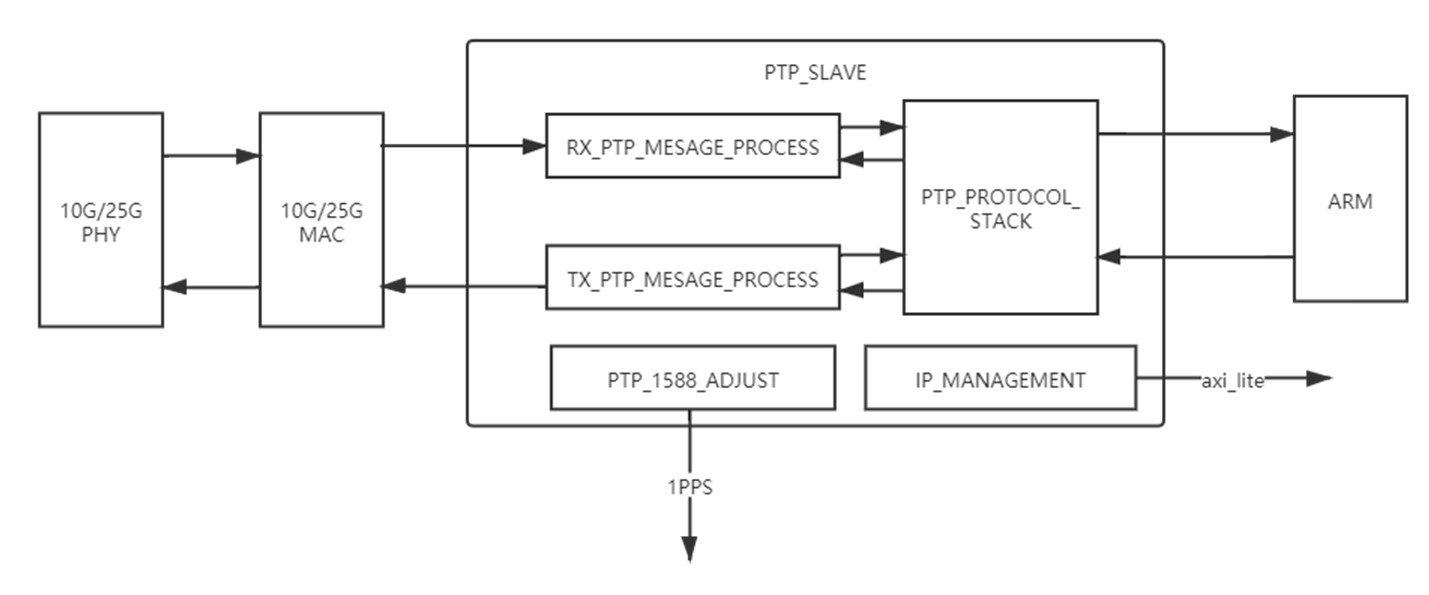

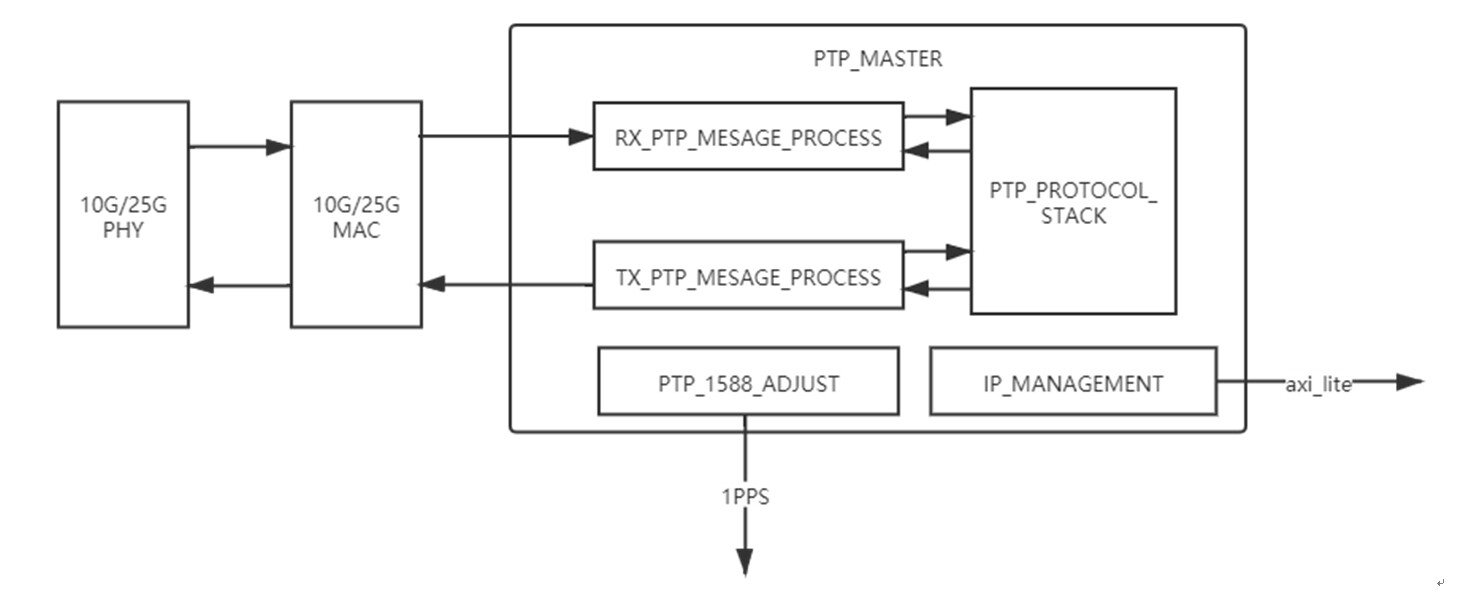

FPGA实现1588协议栈,时间同步精度4ns,支持多设备连接与PID算法调整_fpga 1588

赞

踩

fpga 1588 IP

fpga实现1588相关协议栈,时间调整,包含fpga处理,驱动软件处理。

主要特性

1.时间同步,同步精度达到4ns粒度。

2.MAC地址可设置,支持组播,单播。

3.兼容性强,可以与支持PTP4L协议的RU,DU等设备建立连接。

4.时间调整支持PID算法。

5.资源支持情况下,可无限扩展,支持多路。

6.支持BC,OC。

ID:69200646426507247

小小小fpga

FPGA 1588 IP:高精度的时间同步与调整

概述

最近,随着通信技术的不断进步和智能化网络的广泛应用,时间同步已经成为了网络中一个非常关键的问题。在许多应用场景中,需要对各个节点的时间进行同步,以保证数据的准确性和一致性。为了满足这一需求,FPGA(Field-Programmable Gate Array)技术被广泛应用于实现高精度的时间同步与调整。

FPGA实现1588相关协议栈

FPGA是一种可编程逻辑器件,具备高度的灵活性和可定制性。通过将1588相关协议栈部署在FPGA上,我们可以实现高精度的时间同步和调整功能。FPGA处理器可以通过硬件加速的方式,快速处理时间同步协议,提供低延迟和高精度的时间同步能力。

主要特性

-

时间同步精度达到4ns粒度:通过优化硬件设计和时间同步算法,我们的FPGA 1588 IP支持高达4ns的时间同步粒度,可以满足对时间同步精度要求较高的应用场景。

-

可设置MAC地址,支持组播和单播:为了适应不同的网络环境,我们的FPGA 1588 IP可以灵活设置MAC地址,并且支持组播和单播方式进行数据传输。

-

兼容性强,与PTP4L协议设备建立连接:我们的FPGA 1588 IP与支持PTP4L协议的RU、DU等设备兼容,可以与这些设备进行连接和数据交互,实现高效的时间同步。

-

时间调整支持PID算法:为了满足对时间调整的需求,我们的FPGA 1588 IP支持PID算法,可以根据实际情况对时间进行精确的调整,保证同步的准确性和稳定性。

-

资源支持情况下,可无限扩展,支持多路:通过合理的资源分配和扩展设计,我们的FPGA 1588 IP支持多路数据传输,可以同时处理多个节点的时间同步需求,提高系统的整体性能。

-

支持BC,OC:我们的FPGA 1588 IP支持BC(Boundary Clock)和OC(Ordinary Clock)模式,可以根据实际应用场景灵活选择,满足不同系统的需求。

结论

通过FPGA实现1588相关协议栈,我们可以实现高精度的时间同步和调整功能,满足网络中对时间同步精度要求较高的应用场景。我们的FPGA 1588 IP具备灵活的MAC地址设置、兼容性强、时间调整支持PID算法等多种特性,可以满足不同系统的需求。同时,我们的FPGA 1588 IP还支持多路数据传输和BC、OC模式,可以扩展系统的吞吐量和灵活性。未来,我们将继续研究和改进FPGA技术,在时间同步领域提供更加可靠和高效的解决方案。

(注:此文为虚构文章,仅供参考)

以上相关代码,程序地址:http://matup.cn/646426507247.html