热门标签

热门文章

- 1基于CentOS 7.2的CDH 6.3.2 Spark完整安装_cdh集成spark3

- 2贝叶斯滤波_∑yp(x,y)等于什么

- 3Guitar Pro8许可证2024最新免费_免费版guitar pro

- 4超详细!使用JMeter进行性能测试

- 5一篇学会Swagger2(集成knife4j)_swagger2和knife4j

- 6【条形码识别】基于机器视觉实现条形码识别附Matlab代码_机器视觉扫码读码

- 7Android RIL 动态切换 4G 模块适配_android 4g拨号上网ril

- 8网络协议——Modbus-TCP_modbustcp功能码

- 9SwiftUI调用相机拍照

- 10最新可用,国内国外免费GPT-4o模型的方式!_gpt-4o哪里可以用

当前位置: article > 正文

基于ARM+FPGA的驱控一体机器人控制器设计_fpga 机器人

作者:Gausst松鼠会 | 2024-06-09 18:03:02

赞

踩

fpga 机器人

目前市场上工业机器人,数控机床等多轴运动控制系统普遍采用运动控制器加

伺服驱动器的分布式控制方式。在这种控制方式中,控制器一方面完成人机交互,另

一方面进行

NC

代码的解释执行,插补运算,继而将计算出来的位置指令通过轴组模

块下发给各个伺服驱动器。下发过程通常是由现场总线完成,总线周期为 4

ms

或者

更小。伺服驱动器接收位置指令,位置细分后通过三环控制最终驱动电机。在这个过

程,通常是一个伺服驱动器驱动一个电机,六关节机器人就需要六个驱动器完成,各

个伺服驱动器各自独立地完成位置控制功能,从而实现机器人末端达到指定位置。各

个伺服驱动器的数据交互需要依靠总线完成,但是现场总线通信受通讯速率限制不

能完成一些实时数据(比如电流)交互,因此,轴与轴的数据并不能完全实时共享。

在实际应用中,分布式机器人控制系统结构相对分散,一些复杂控制算法,比如

结合机器人的运动学动力学的电流前馈加反馈线性化的伺服控制算法,多轴精确同

步控制算法等在分布式控制系统中实现有一定难度,而且现场总线需要一定的布线

成本。鉴于以上缺点,有必要进一步简化运动控制系统结构。

控驱一体的运动控制系统结构将原来相互独立的控制器和各个伺服驱动器结合

在一起,在

SoC

(

System-On-Chip

)芯片上实现控驱一体。这样做的好处是:

(1)整个运动控制系统的结构更加紧凑,控制电柜体积更小,集成度更高,适用

于物理空间有限的工作环境,同时方便运输和安装。

(2)基于单芯片

SoC

架构方案替代多单元控制器对多单元电机的驱动方式,不依

靠现场总线完成通讯,降低硬件和软件互连的成本,同时充分利用嵌入式

SoC

芯片特

性,满足运动控制器的功能性要求和伺服驱动器的实时性要求,降低控制器成本。

(3)控制器与驱动器更加紧密的耦合,有利于高级复杂运动控制算法实现。比如

多轴同步控制,速度加速度前馈,抖动抑制,摩擦补偿等。让运动学和动力学控制算

法参与或者得到伺服驱动中的电流环的运算结果,伺服驱动器也可以预测轨迹规划

的运算结果,有助于提高机器人控制性能。

(4)片内总线替代现场总线,

通信的带宽更高和稳定性更好

。与现在的工业现场

总线的分布式控制系统相比,信息交换完全依靠片内总线完成,它是一种并行总线,

相比于轮询式的串行现场总线,不仅考虑昂贵的布线成本,而且通讯速率受到串行通

讯方式限制。采用并行总线可以很好地保证多轴数据交互的同步性和实时性。

(5)控制器与驱动器之间数据交互的实时性能更好,控制器可以更加方便和及时

地利用驱动器的反馈状态信息,控制器根据反馈信息实时调整控制策略,从而使实现

更好的控制性能。

(6)控制器与驱动器的通讯速率得到提高,控制器的插补周期可以进一步减小,

位置环的刷新周期可以进一步减小,有助于实现高速状态下的高精,实现真正意义上

的高速高精。

(7)有利于控制器以更高的频率采集驱动器的运动变量参数,更精确的描述参数

的变化趋势,方便对机器人运动状态进行更细致分析。

1.3 国内外研究现状

1.3.1 伺服驱动系统的研究现状及发展趋势

典型的机器人控制系统在结构上大致分为三个层次:控制器,伺服驱动器,机器

人本体。近年来,出现了交流伺服驱动器的两种不同发展方向。第一种是运动控制器

保持不变,伺服驱动器和伺服电机一体化集成;第二种是伺服电机保持不变,伺服驱

动器和运动控制器一体化集成。

将伺服驱动器和伺服电机一体化集成对伺服驱动器要求较高,必须具备小型化,

散热好,高频特性的特点。目前国内对这方面研究正处于起步阶段。国外方面,以色

列的

ELMO

公司推出的

Twitter

伺服驱动器便是一种微小型高功率密度驱动器,如图

1-1 所示。采用 “快速软开关技术”,实现大于 99%的效率以及几乎可忽略不计的电

伺服电机保持不变,把伺服驱动器和运动控制器做一体化集成也是一种发展趋

势,即朝控驱一体方向发展。其优势包括:体积小,重量轻,成本低,可靠性高,部

署灵活,能够完成复杂的机器人算法,适合用于物理空间有限的工作场合等。目前国

内外公司已推出控驱一体化产品(如:固高、众为兴、台达、

KUKA

,

ABB

等等),

大多采用分布式

CPU

方式进行控驱一体整合,国内用于

3C

机械臂,桌面机械臂等

对空间要求较高的场合,国外更多应用在人机协作,自动化生产线等场合。

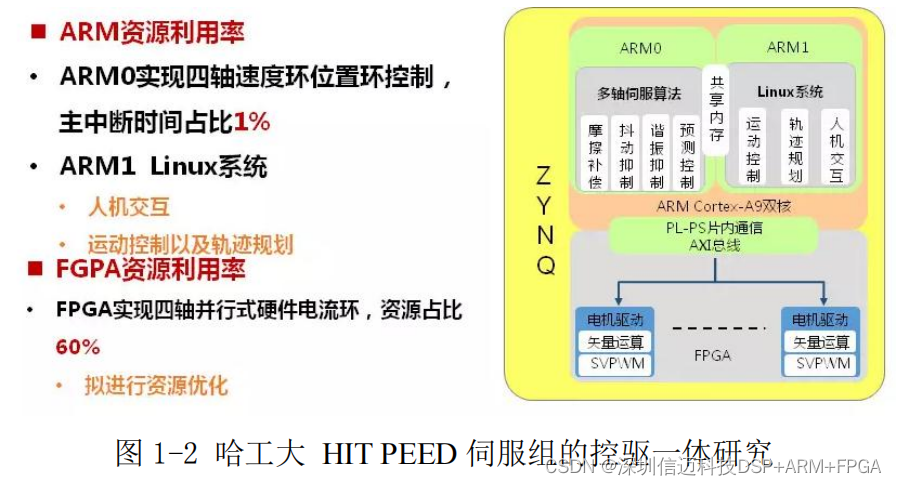

国内,2018 年哈尔滨工业大学

HIT PEED

伺服组基于

zynq

平台开发出小批量

驱控一体化样机,一个芯片可以独立控制 4-6 轴,如图 1-2 所示(图片引自 2019 智

能制造&中国运动控制行业发展高峰论坛)。采用赛灵思公司的高性能

SoC 芯片,其

中

PL(Progarmmable Logic)

部分完成多轴电机驱动,带宽高、响应快,

PS(Processing

System)

部分进行运动控制算法的实现和各类通讯及数据交互等功能。

总之,随着信号检测技术(例如高精度,低时延的采样技术),自动控制技术(例

如模糊控制,自适应,预测控制等),驱动控制技术(例如

PWM

调制技术,死区等

非线性因素补偿技术等),芯片技术(

SoC

芯片技术)的发展,伺服系统发展趋势朝

着高性能,集成化和模块化,通用化和专用化,网络化和智能化的方向发展。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/695230

推荐阅读

相关标签