- 1手动安装Nextcloud(非宝塔面板安装,LAMP安装)_nextcloud安装

- 2智慧医院解决方案如何落地 智慧医院解决方案实际应用_rg-apd-s

- 3OSNIT信息收集分析框架OSRFramework

- 4iOS 微信应用副本 (免费&安全)_微信副本

- 5Java基础篇--SecureRandom(安全随机)类_securerandom securerandom

- 6【小黑送书—第十二期】>>一本书讲透Elasticsearch_《一本书讲透 elasticsearch》pdf下载一本书讲透elasticsearch:原理、进阶

- 7华为 在ESPN中配置单区域MSTP_华为espn

- 8AX58100(ESC)通过MCU进行在线升级_mcu和ax58100的通信协议

- 9Python -- pygame(球球大作战)

- 10React脚手架的搭建与使用

Verilog基本语法_verilog里面sel

赞

踩

1.assign out = (sel==1)?a:b;

注释:当sel的取值为1的时候,out赋值为a,当sel取值不为1的时候,out赋值为b(二选一选择器)

2.'timescale 1ns/1ps'

注释:1ps指的是时间精度可以达到1ps,1ns指的是后续文件中#1指的是延时1ns

3.激励文件中:激励信号(输入)定义成Reg型

输出信号定义为Wire型

$stop停止下来

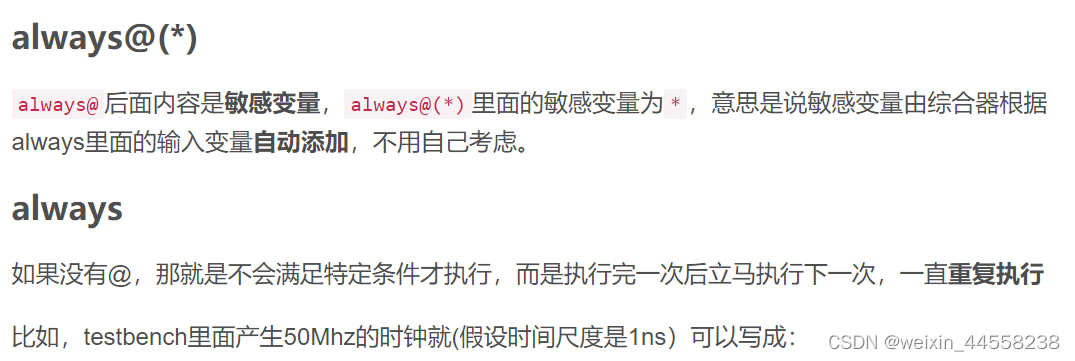

4.

5.位拼接:{},eg:a,b,c是一位的信号,{a,b,c}变成了一个3位的信号。

6.以always块描述的信号赋值,被赋值的对象必须定义为reg类型。

7.非阻塞赋值《=在时序逻辑电路里面使用,

阻塞赋值和非阻塞赋值的区别

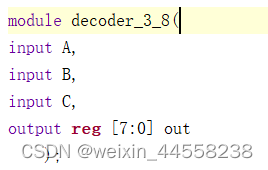

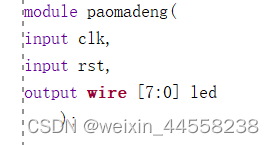

8.reg型只能在底层文件中,当顶层文件的输出和底层文件的输出相连接时,顶层文件的输出应该定义为WIRE型

例如: 这是底层文件的端口定义 这是顶层文件的端口定义

led和out相连,顶层文件的LED定义为out型。

9.左移位<< 替代:eg:led的初始值为00000001,有led<=led<<1等效于led<={led[6:0],led[7]}

右移位>> 替代:eg:led的初始值为00000001,有led<=led>>1等效于led<={led[0],led[7:1]}

详情参见跑马灯程序

10.位运算

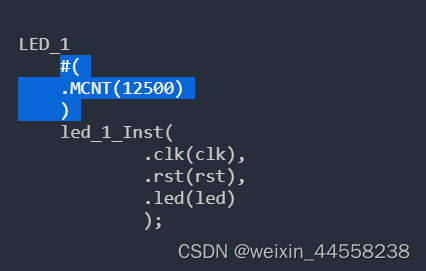

11.对于源文件中定义的parameter参数,在激励文件中和源文件中可以用defparam改变参数的数值。该方法可用于模块化设计

源文件中:

parameter MCNT=26'd50000000;激励文件中:

defparam led_1_Inst.MCNT = 27'd12500;或者:

上述两种方法将激励文件中的MCNT的数值改为了12500.

12:定义一个二维数组:reg 元素位宽 名字 元素数量

eg:

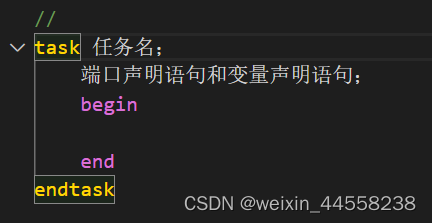

reg [3:0] x_bit [7:0]; //定义一个二维数组,该二维数组里面有7个元素,每个元素位宽三位 13:task块的使用:

(1)任务的输入、输出端口和双向端口数量不受限制,甚至可以没有输入、输出以及双向端口。

(2)在任务定义结构内不能出现 initial和 always过程块。

(3)在任务定义的描述语句中,可以使用出现不可综合操作符合语句(使用最为频繁

的就是延迟控制语句) ,但这样会造成该任务不可综合。

(4)在任务中可以调用其他的任务或函数,也可以调用自身。

14.随机函数在tb文件中得应用

- reg [24:0] rand_time;

- rand_time = $random % 60;

表示产生在[-59,59]里的有符号随机数

rand_time ={ $random }% 60; 表示产生0-59的无符号随机数。

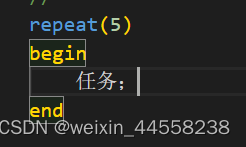

15 循环函数repeat()的使用,如图表示任务1循环5次

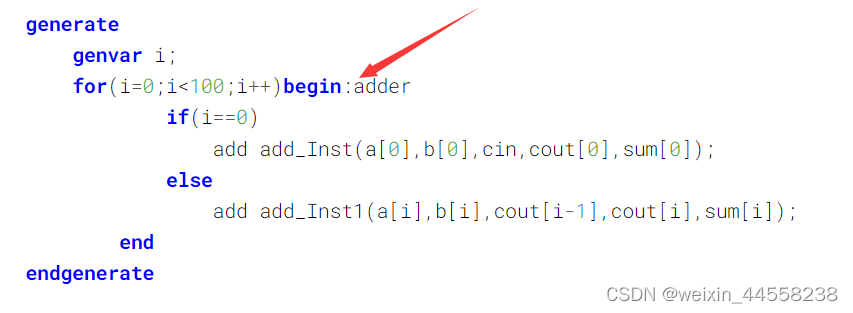

16.generate循环的使用,verilog中的generate语句常用于编写可配置的、可综合的RTL的设计结构,它可用于创建模块的多个实例化。在使用时必须先在genvar声明中声明循环中使用的索引变量名,然后才能使用它。genvar声明的索引变量被用作整数用来判断generate循环。genvar声明可以是generate结构的内部或外部区域,并且相同的循环索引变量可以在多个generate循环中,只要这些环不嵌套。genvar只有在建模的时候才会出现,在仿真时就已经消失了。

eg.例化100个add模块,注意:后边儿这个命名一定要加,即必须给for段取个名字。

17.parameter和localparam的区别

parameter: 全局参数定义,可在整个设计中传递参数

localparam: 1.仅限于当前模块的参数定义,跨模块不可用

2.指定的参数不能通过defparam进行修改;

3.指定的参数不能通过模块例化进行修改