热门标签

热门文章

- 1SpringBoot、Dubbo、Redis、Hibernate浅谈_springboothibernate架构图

- 2海量数据处理问题 分而治之 hash表 堆排序_海量数据怎样实时地分成两堆数

- 3Uniapp软件库源码 全新带勋章功能(包含前后端源码)

- 4详解DBSCAN聚类算法_dbscan 算法是一种基于密度的聚类算法,对异常值非常敏感,因此要在聚类前进行异常

- 5手把手教你打造游戏开发的完美简历(文末有福利哦!)_游戏 开发 简历 优化

- 6存储基础知识(三):文件系统_hpfs、nfs、cifs

- 7深入思考redis面经

- 8Android打印Trace堆栈_android 打印调用栈

- 9信息安全等级保护的政策依据及相关标准_1999年信息安全保障文件27号文件是什么

- 10python医学科研中能做什么-这个工具,可全网爬取科研圈中外文献!

当前位置: article > 正文

异步信号的set_max_delay设置_max delay时钟案例分析

作者:木道寻08 | 2024-07-13 08:44:51

赞

踩

max delay时钟案例分析

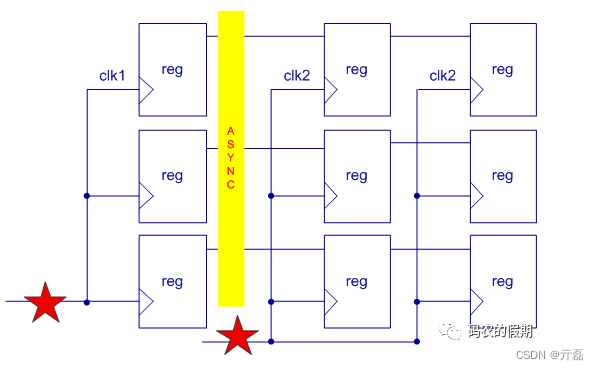

一、基本二级同步结构

源时钟域同步一拍,目的时钟域同步两拍。

二、源时钟域打拍输出信号,与目的时钟域采样之间,是一根线。这根线延迟如果不约束set_max_delay,会存在风险。

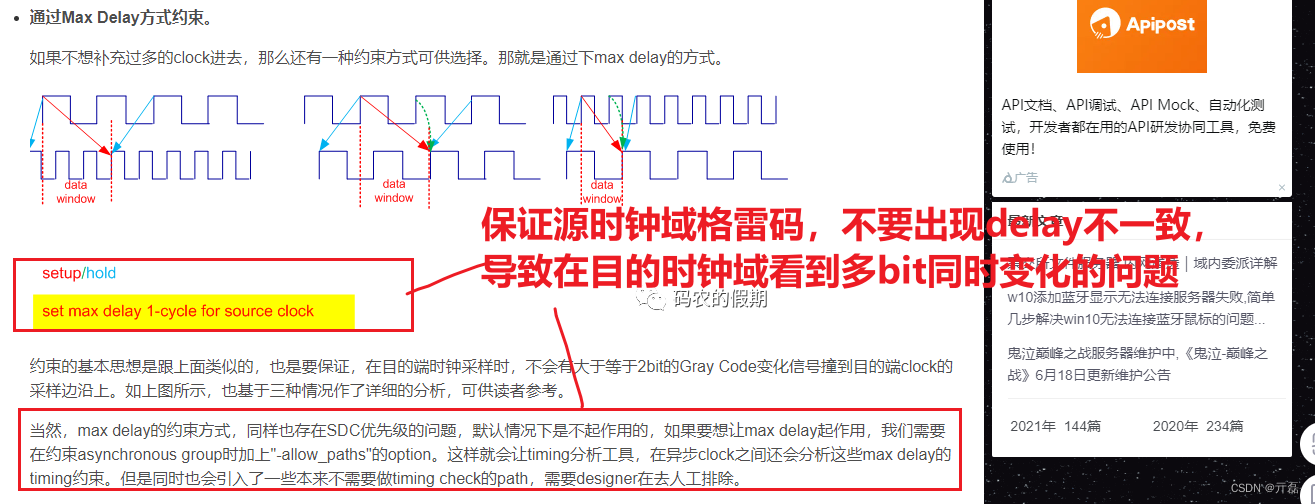

举例,格雷码总线信号,多根线,因为线延迟不一致,导致在目的时钟域采样的时候,有可能存在多bit同时翻转的问题现象。导致读写指针,空满标志判断出错,功能出错。

相关图片,转载来自:《异步fifo_Gray Code异步FIFO的多种约束方式》https://blog.csdn.net/weixin_39950083/article/details/111586325

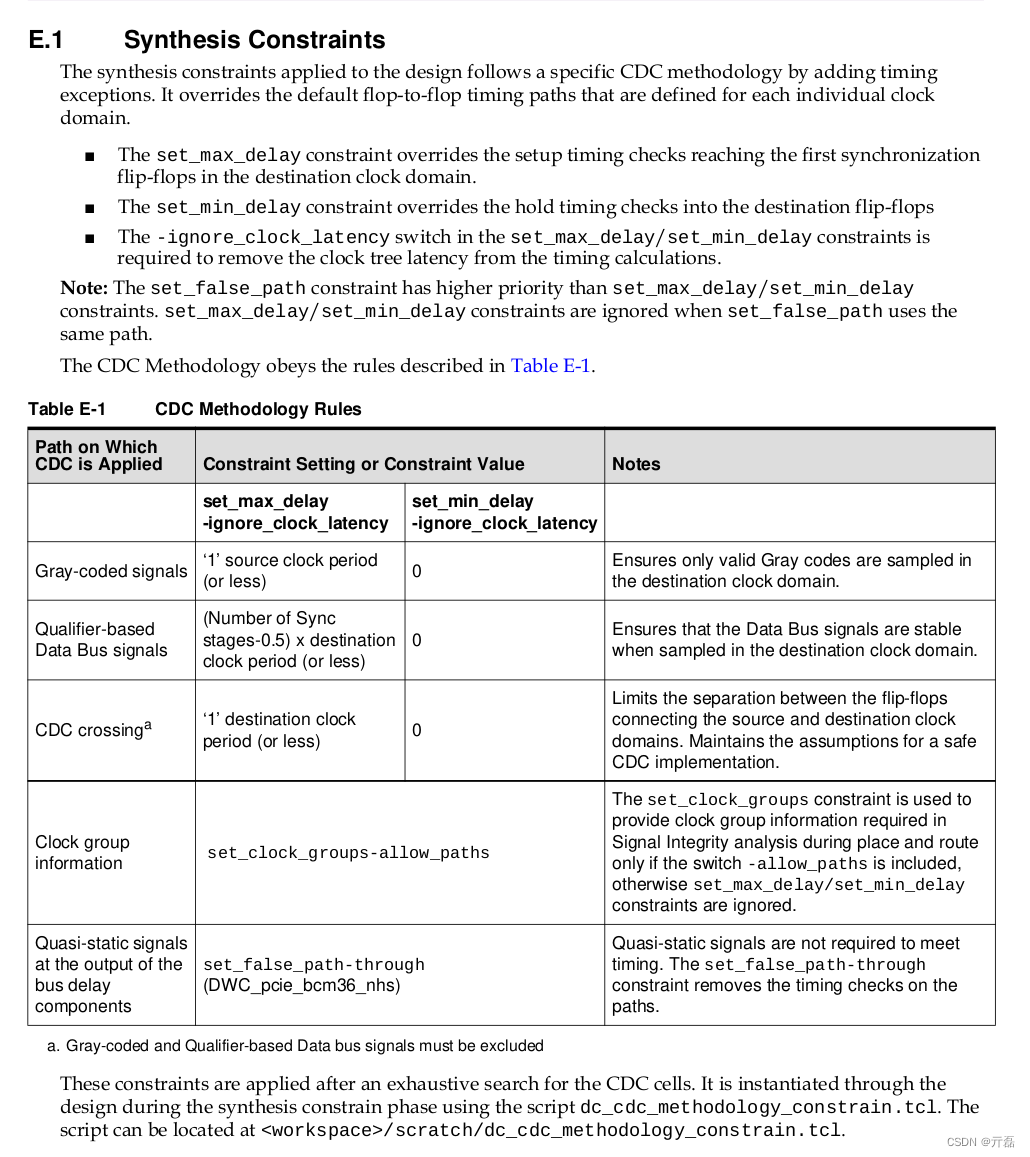

下图参考synopsys IP的设置方法:

配合下图,个人理解下图是有逻辑顺序的。【set_max_delay相比false_path,false_path优先级高】【路径越精确优先级越高】【最好是加余量,比如1T->0.8T】:

- 设置格雷码。set_max_delay 0.8T_source -ignore_clock_latency

- 然后设置静态数据总线信号(有同步的那种)。

- set_max_delay 0.8T_source -ignore_clock_latency先设置不同时钟域之间的set_max_delay 0.8T_destination -ignore_clock_latency。【比如有些数据总线信号/伴随信号,是通过握手同步传递的。注意,相关数据总线信号/伴随信号,也需要设置set_max_delay,否则会握手同步的伴随信号出错】

- 如果综合加上,就要-allow_paths。但是会影响dft设计,项目中还是把set_max_delay单独抓出来在后端STA阶段分析吧。

- 最后一条set_false_path,是去除上面,主要是第1条中的静态信号,保证时序收敛不要有太多过约现象。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/木道寻08/article/detail/818610

推荐阅读

相关标签