热门标签

热门文章

- 1HarmonyOS开发 :Router 和 NavPatchStatck 如何实现跳转(传参)及页面回调_import { router } from '@kit.arkui';

- 2【YOLOv8改进[CONV]】使用DynamicConv二次创新C2f模块实现轻量化 + 含全部代码和详细修改方式 + 手撕结构图

- 3多线程死锁问题

- 4用 winmm 播放音乐 - ChengKing - 博客园_winmm playsound mp3

- 5【机器学习】利用机器学习优化陆军战术决策与战场态势感知_作战 决策 数据集

- 6CA加密,网络安全HTTPS SSL-HMAC算法安全性浅析_ssl中使用了hamc

- 7stm32f103真实项目程序。 c原程序 keil工程。 硬件平台采用小米1代扫地机_小米扫地1c stm32

- 8PKI技术简介_pki 技术背景

- 9汇总国内最新GPT4o、4.0等网站【2024年最新】_gpt4国内写sql的网站

- 10大模型和传统ai的区别_ai大模型区别

当前位置: article > 正文

VIVADO软件DDS信号发生器Verilog代码的任意波形发生器_vivado生成cosnx波

作者:IT小白 | 2024-06-15 22:56:09

赞

踩

vivado生成cosnx波

名称:VIVADO软件DDS信号发生器Verilog语言的任意波形发生器

软件:VIVADO

语言:Verilog

代码功能:

1.可产生正弦波,锯齿波,三角波,方波4种波形

2.输出波形的频率可调、相位可调、幅值可调

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

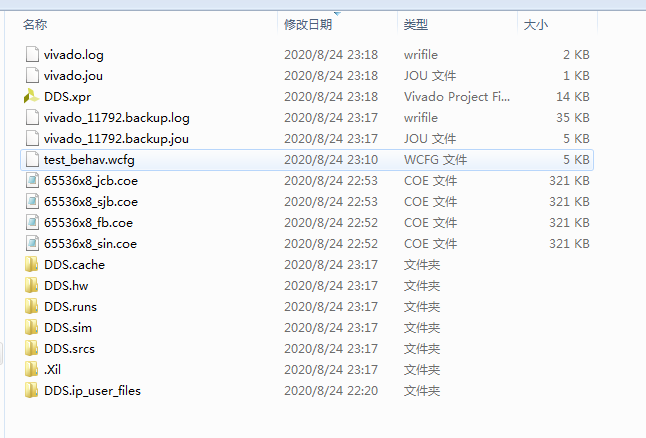

1. 工程文件

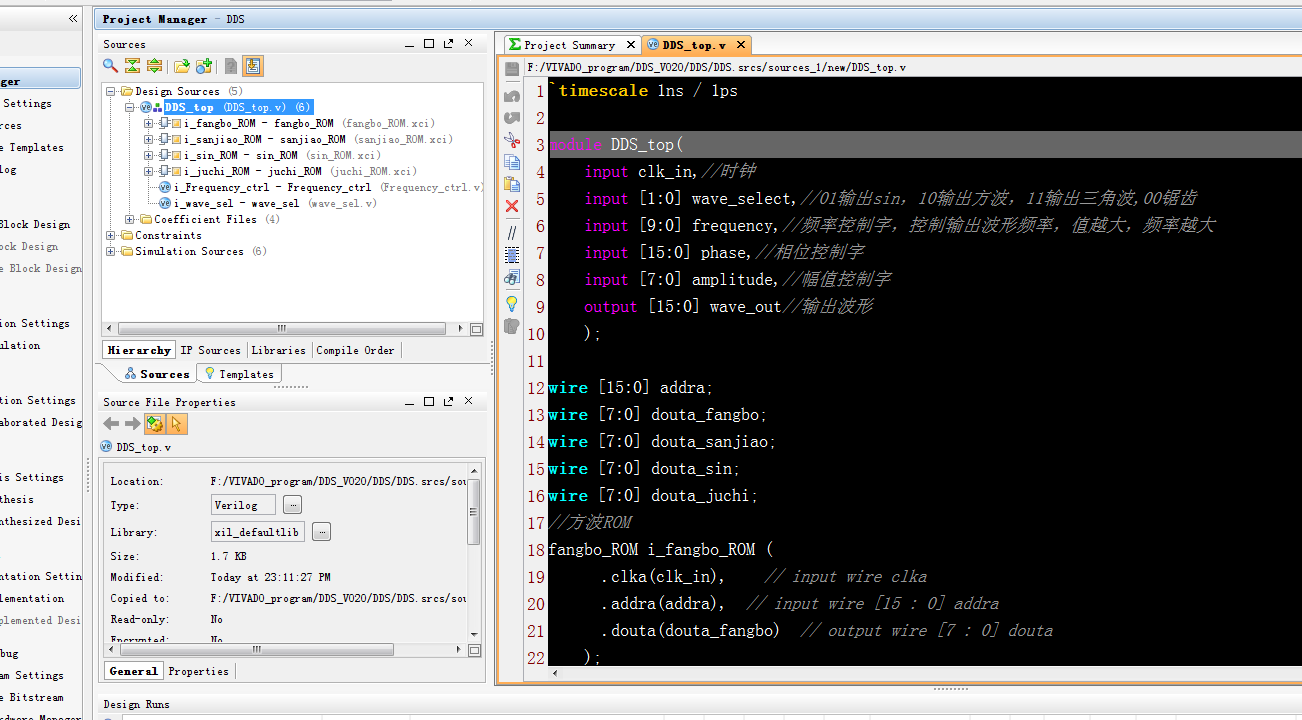

2. 程序文件

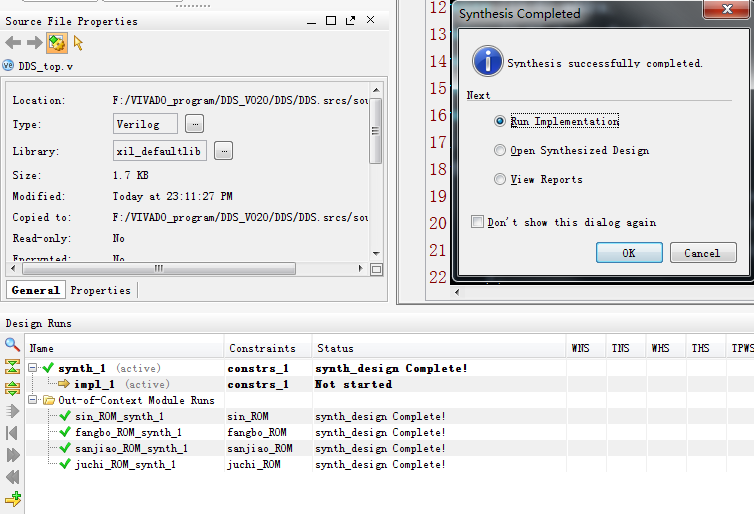

3. 程序编译

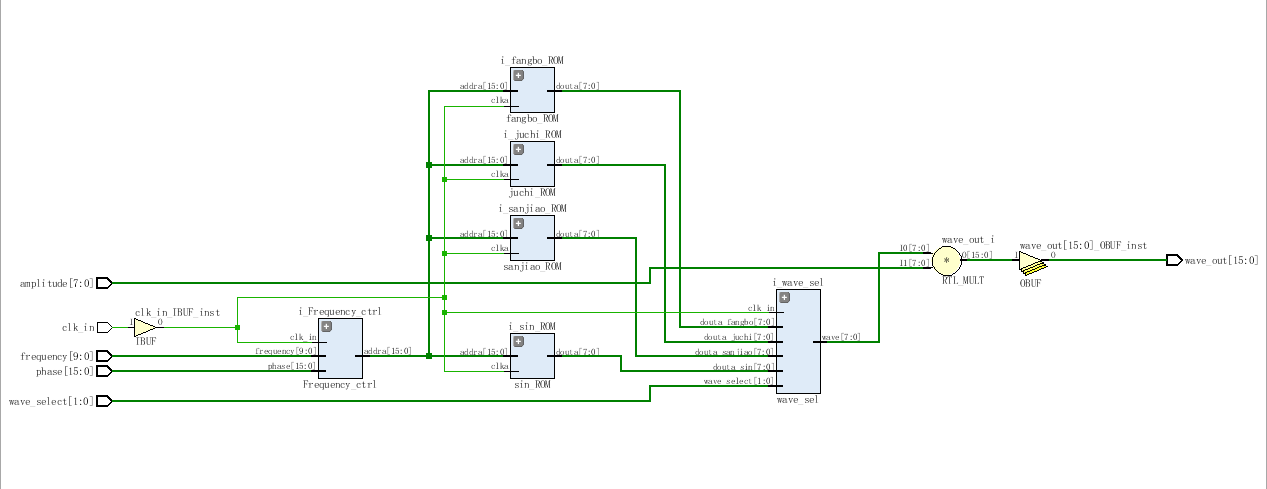

4. RTL图

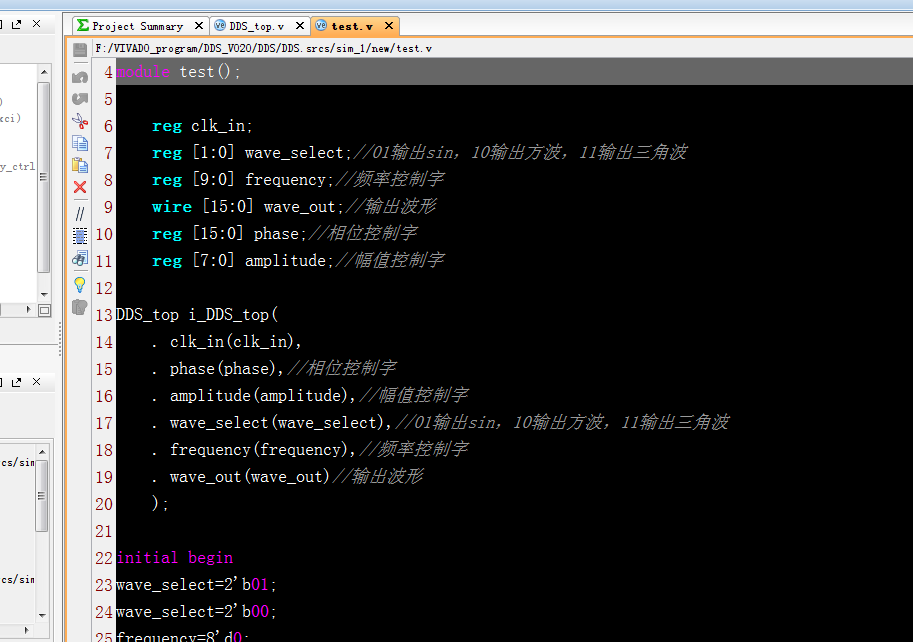

5. Testbench

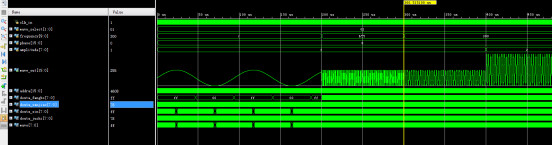

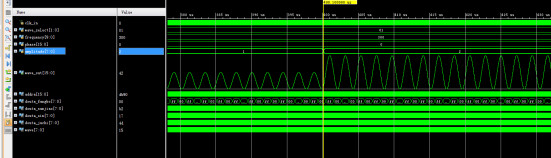

6. 仿真图

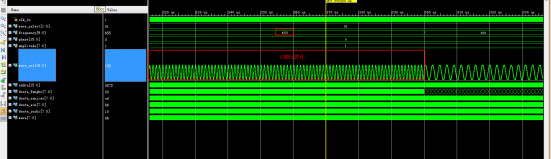

1. 任意正弦波输出

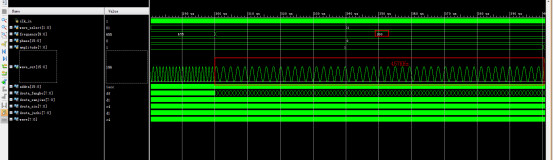

2. 10K、1MHz、10K~1MHz波形

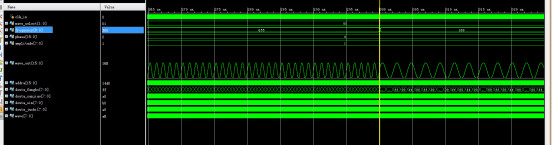

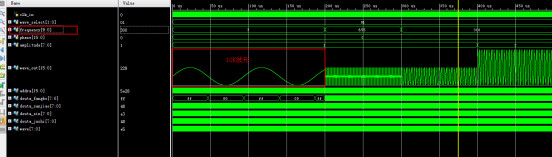

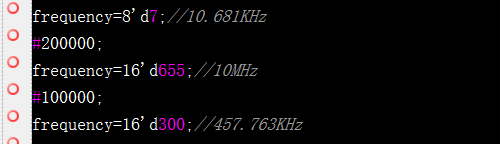

3. 对应频率控制字和相位控制字

![]()

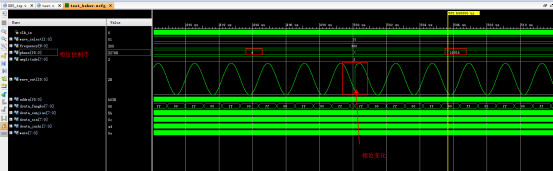

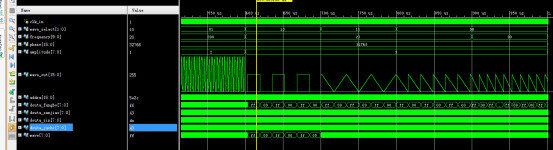

4. 不同初相正弦波

5. 不同振幅、均值正弦波

6. 方波、锯齿波、三角波等

部分代码展示:

`timescale 1ns / 1ps module DDS_top( input clk_in,//时钟 input [1:0] wave_select,//01输出sin,10输出方波,11输出三角波,00锯齿 input [9:0] frequency,//频率控制字,控制输出波形频率,值越大,频率越大 input [15:0] phase,//相位控制字 input [7:0] amplitude,//幅值控制字 output [15:0] wave_out//输出波形 ); wire [15:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; wire [7:0] douta_juchi; //方波ROM fangbo_ROM i_fangbo_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_fangbo) // output wire [7 : 0] douta ); //三角波ROM sanjiao_ROM i_sanjiao_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_sin) // output wire [7 : 0] douta ); //锯齿 juchi_ROM i_juchi_ROM ( .clka(clk_in), // input wire clka .addra(addra), // input wire [15 : 0] addra .douta(douta_juchi) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_in(clk_in), . frequency(frequency),//频率控制字 . phase(phase),//相位控制字 . addra(addra)//输出地址 ); wire [7:0] wave; //波形选择控制 wave_sel i_wave_sel( . clk_in(clk_in), . wave_select(wave_select),//01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_juchi(douta_juchi),//锯齿 . douta_sin(douta_sin), //正弦 . wave(wave)//输出波形 ); assign wave_out=wave*amplitude;//输出波形 endmodule

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/IT小白/article/detail/724153

推荐阅读

相关标签